数字系统设计与verilog HDL PPT学习教案.pptx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

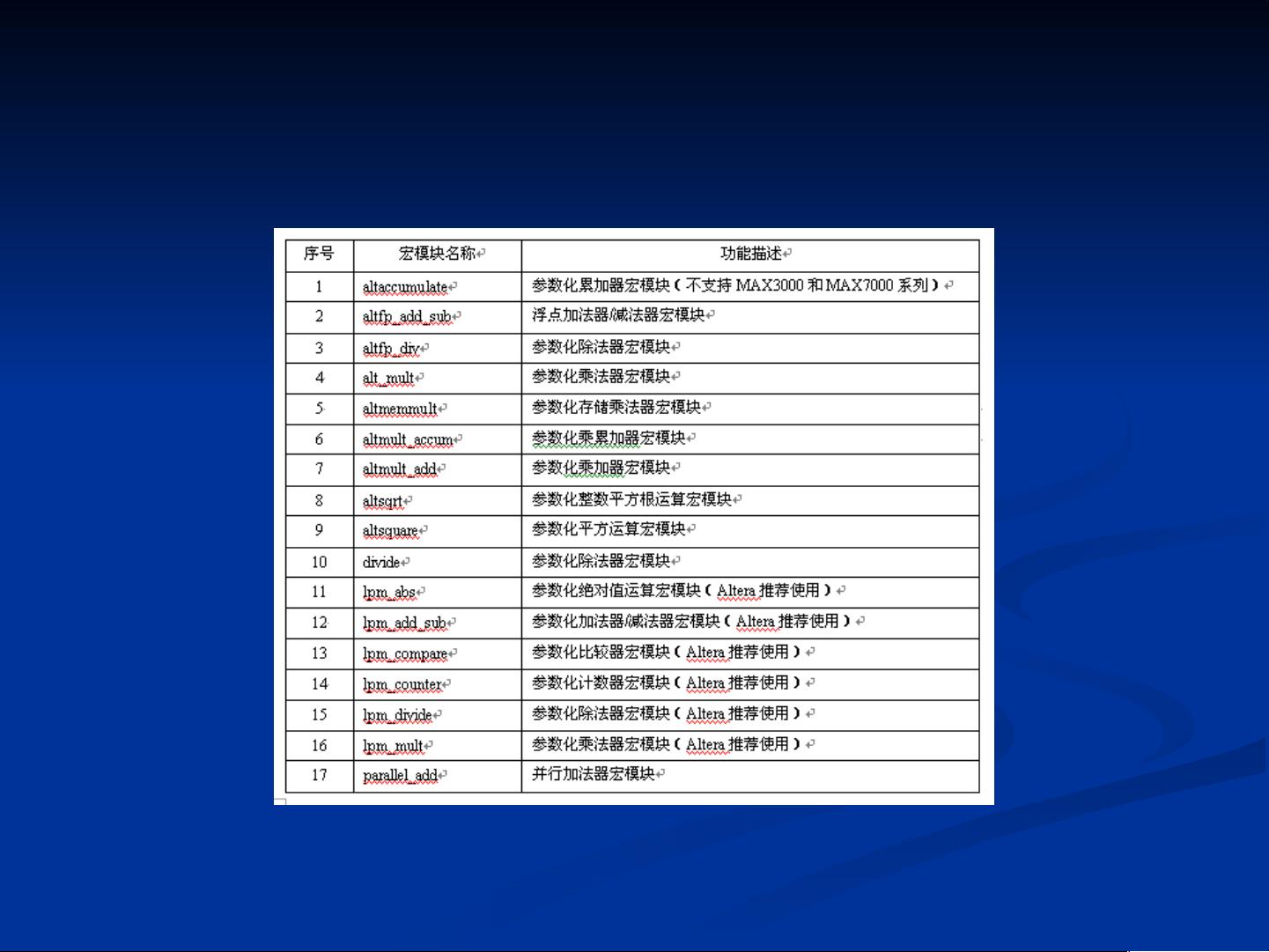

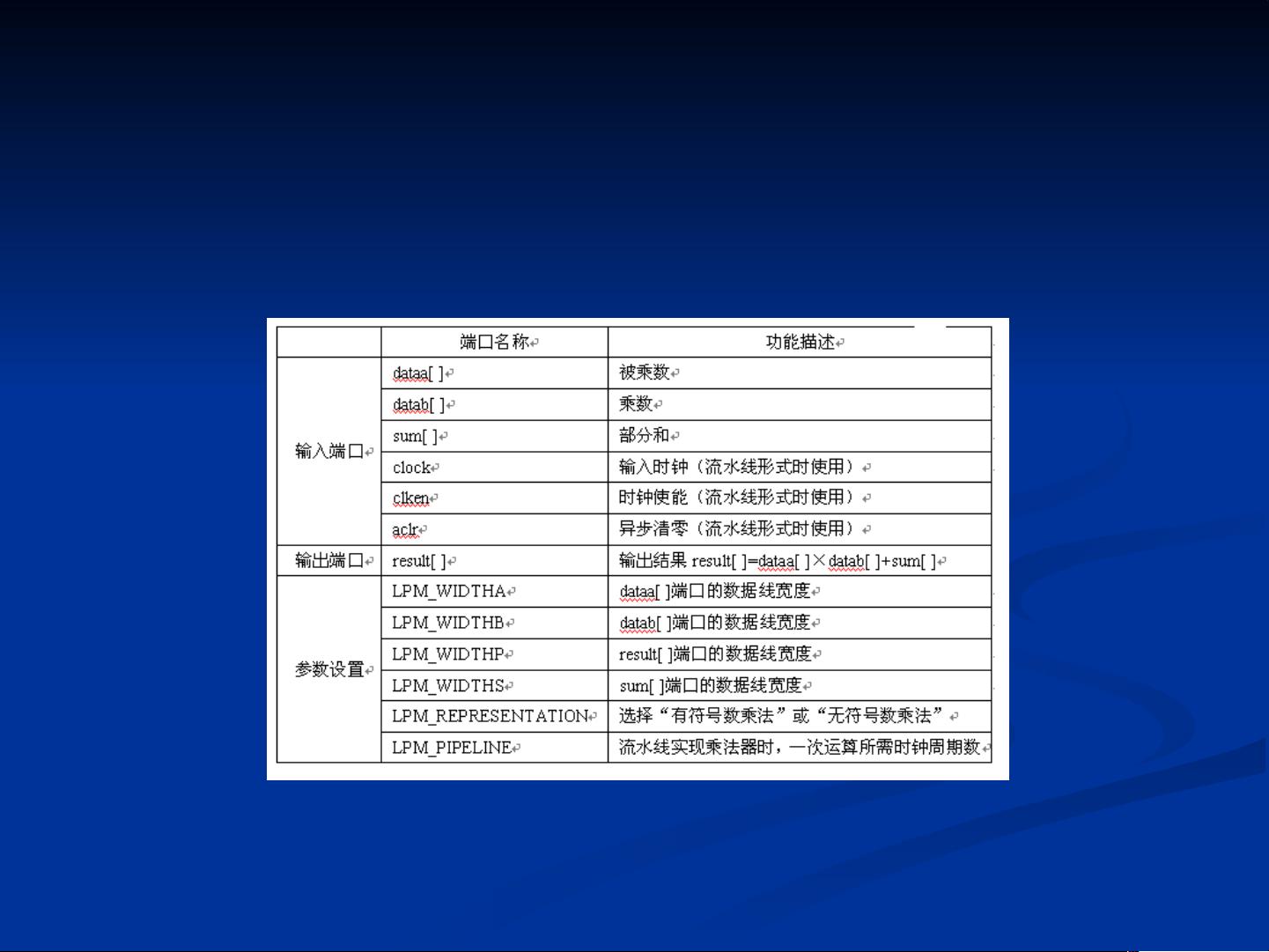

《数字系统设计与Verilog HDL学习教案》深入解析 在数字系统设计中,Verilog HDL是一种广泛使用的硬件描述语言,它允许设计者通过文本形式描述数字逻辑系统的结构和行为。本篇教程将围绕Verilog HDL,重点介绍基于Altera公司的Megafunction库进行设计的几个关键模块,包括乘法器、计数器、锁相环以及存储器。 我们关注乘法器模块。Altera的Megafunction库提供了参数化的lpm_mult宏功能,用于实现不同位宽的乘法操作。算术运算模块不仅限于乘法,还包括其他基本的数学运算。在使用lpm_mult时,我们需要设置输入输出位宽以及乘法器类型。在完成配置后,进行编译和仿真,例如创建一个8位有符号乘法器,并观察功能仿真波形,验证其正确性。 接下来是计数器模块。计数器是数字系统中不可或缺的部分,可以实现递增或递减计数。在Altera的Megafunction中,lpm_counter提供了灵活的计数器配置选项,包括输出端口宽度、计数方向、模值以及多种控制端口设置。以一个模24方向可控计数器为例,我们可以看到其电路设计及功能仿真的波形,以确保计数器按照预期工作。 锁相环(Phase-Locked Loop,PLL)是数字系统中处理时钟的重要组件。Altera的altpll宏功能模块可实现锁相,提供同步的倍频或分频时钟信号,以优化系统性能。在设置altpll时,我们需要选择合适的芯片,定义参考时钟,并调整锁相环的控制信号和输入时钟参数。通过编译和仿真,可以验证锁相环的性能,如时钟稳定性和频率转换效果。 我们讨论存储器模块,特别是只读存储器(ROM)。在FPGA设计中,虽然FPGA内部的存储器不具备传统ROM的非易失性,但它可以通过lpm_rom宏实现ROM的功能。以4位×4位无符号数乘法器为例,通过预加载数据到ROM并在运行时读取,可以实现乘法运算。在配置lpm_rom时,需设定数据线和地址线的宽度,以及必要的控制端口,以便在设计中灵活地访问和使用存储数据。 本教程详尽介绍了Verilog HDL在数字系统设计中的应用,通过Altera的Megafunction库,我们可以高效地实现乘法器、计数器、锁相环和存储器等核心模块,这对于理解和构建复杂的数字系统至关重要。理解并掌握这些基本模块的设计和配置方法,有助于提升数字系统设计的效率和质量。

剩余26页未读,继续阅读

- 粉丝: 7

- 资源: 58万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功