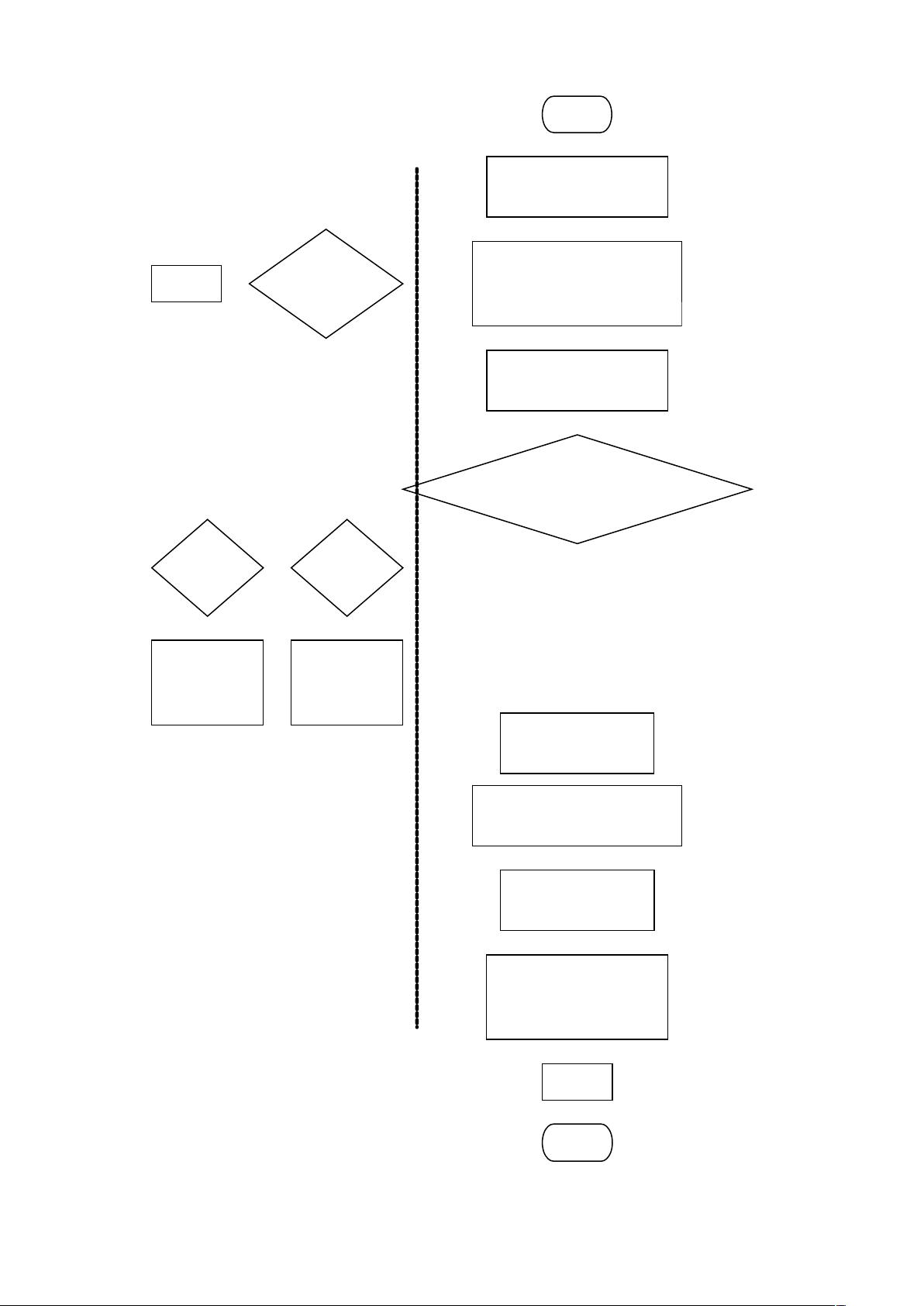

附录:

开始

先复位按下 RST ,使

所有状态都回复初始

态

按下使能键 EN 使 FPGA

在使能时间内计数,并使

单片机开始工作

延时一段时间,以使

FPGA 工作完成

使 能 是

否结束

计数

N

Y

发 送 传 送 控 制 信 号

SE 从 000~111 。结束

否

SE=

0~3

?

SE=

4~7

?

N

传送 相应 状

态的 被测 频

率计数数

传送 相应 状

态的 标准 频

率计数数

接收数据存入相应

数组相应位

将两组数据合并成 2 个 32

位的二进制数

Y

通过公式计算出被

测频率

译码处理将被测频率

处理作可以显示小数

点的八个段码

显示

由 于 FPGA 和 单 片 机

时 钟 都 为

20Mhz , FPGA 处 理

数据需要一段时间,故

需要延时一段时间才能

保证传出的数据的正确

性

结束

FPGA 部分

单片机部分

系统流程图

VCC

DCCLK

INPUT

VCC

EN

INPUT

VCC

BZCLK

INPUT

VCC

RST

INPUT

VCC

SE[2..0]

INPUT

DATA[7..0]

OUTPUT

CLK

D

Q

DFF1

inst2

EN

CLK

CLR

Q[31..0]

TF

inst5

EN

CLK

CLR

Q[31..0]

BZH

inst1

Q1[31..0]

Q2[31..0]

SE[2..0]

DATA1[7..0]

SEND

inst

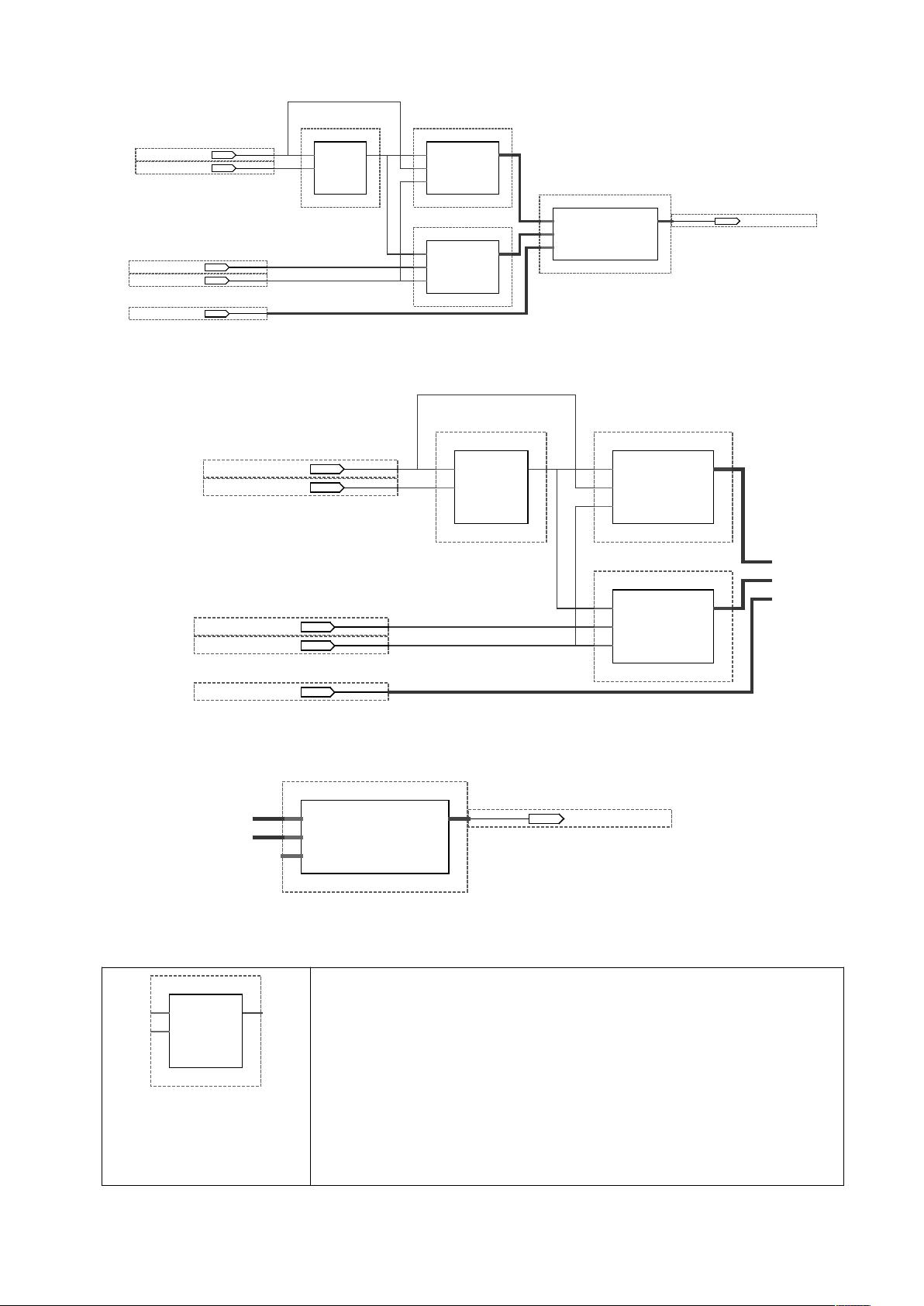

上图为 FPGA 的计数发送模块的的原理图

VCC

DCCLK

INPUT

VCC

EN

INPUT

VCC

BZCLK

INPUT

VCC

RST

INPUT

VCC

SE[2..0]

INPUT

CLK

D

Q

DFF1

inst2

EN

CLK

CLR

Q[31..0]

TF

inst5

EN

CLK

CLR

Q[31..0]

BZH

inst1

计数模块原理图

DATA[7..0]

OUTPUT

Q1[31..0]

Q2[31..0]

SE[2..0]

DATA1[7..0]

SEND

inst

发送模块原理图

FPGA 的各个模块说明

CLK

D

Q

DFF1

inst2

D 触发器

当时钟上升沿来时传出

D 的相反状态,作为使能

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DFF1 IS

PORT (CLK,D:IN STD_LOGIC;

Q: OUT STD_LOGIC );

END;

ARCHITECTURE BHV OF DFF1 IS

BEGIN

PROCESS (CLK)