没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

This is the Title of the Book, eMatter Edition

Copyright © 2005 O’Reilly & Associates, Inc. All rights reserved.

302

Chapter 12

CHAPTER 12

PCI Drivers

While Chapter 9 introduced the lowest levels of hardware control, this chapter pro-

vides an overview of the higher-level bus architectures. A bus is made up of both an

electrical interface and a programming interface. In this chapter, we deal with the

programming interface.

This chapter covers a number of bus architectures. However, the primary focus is on

the kernel functions that access Peripheral Component Interconnect (PCI) peripher-

als, because these days the PCI bus is the most commonly used peripheral bus on

desktops and bigger computers. The bus is the one that is best supported by the ker-

nel. ISA is still common for electronic hobbyists and is described later, although it is

pretty much a bare-metal kind of bus, and there isn’t much to say in addition to

what is covered in Chapters 9 and 10.

The PCI Interface

Although many computer users think of PCI as a way of laying out electrical wires, it

is actually a complete set of specifications defining how different parts of a computer

should interact.

The PCI specification covers most issues related to computer interfaces. We are not

going to cover it all here; in this section, we are mainly concerned with how a PCI

driver can find its hardware and gain access to it. The probing techniques discussed

in the sections “Module Parameters” in Chapter 2 and “Autodetecting the IRQ

Number” in Chapter 10 can be used with PCI devices, but the specification offers an

alternative that is preferable to probing.

The PCI architecture was designed as a replacement for the ISA standard, with three

main goals: to get better performance when transferring data between the computer

and its peripherals, to be as platform independent as possible, and to simplify add-

ing and removing peripherals to the system.

,ch12.1659 Page 302 Friday, January 21, 2005 3:08 PM

This is the Title of the Book, eMatter Edition

Copyright © 2005 O’Reilly & Associates, Inc. All rights reserved.

The PCI Interface

|

303

The PCI bus achieves better performance by using a higher clock rate than ISA; its

clock runs at 25 or 33 MHz (its actual rate being a factor of the system clock), and

66-MHz and even 133-MHz implementations have recently been deployed as well.

Moreover, it is equipped with a 32-bit data bus, and a 64-bit extension has been

included in the specification. Platform independence is often a goal in the design of a

computer bus, and it’s an especially important feature of PCI, because the PC world

has always been dominated by processor-specific interface standards. PCI is cur-

rently used extensively on IA-32, Alpha, PowerPC, SPARC64, and IA-64 systems,

and some other platforms as well.

What is most relevant to the driver writer, however, is PCI’s support for autodetec-

tion of interface boards. PCI devices are jumperless (unlike most older peripherals)

and are automatically configured at boot time. Then, the device driver must be able

to access configuration information in the device in order to complete initialization.

This happens without the need to perform any probing.

PCI Addressing

Each PCI peripheral is identified by a bus number, a device number, and a function

number. The PCI specification permits a single system to host up to 256 buses, but

because 256 buses are not sufficient for many large systems, Linux now supports PCI

domains. Each PCI domain can host up to 256 buses. Each bus hosts up to 32

devices, and each device can be a multifunction board (such as an audio device with

an accompanying CD-ROM drive) with a maximum of eight functions. Therefore,

each function can be identified at hardware level by a 16-bit address, or key. Device

drivers written for Linux, though, don’t need to deal with those binary addresses,

because they use a specific data structure, called

pci_dev, to act on the devices.

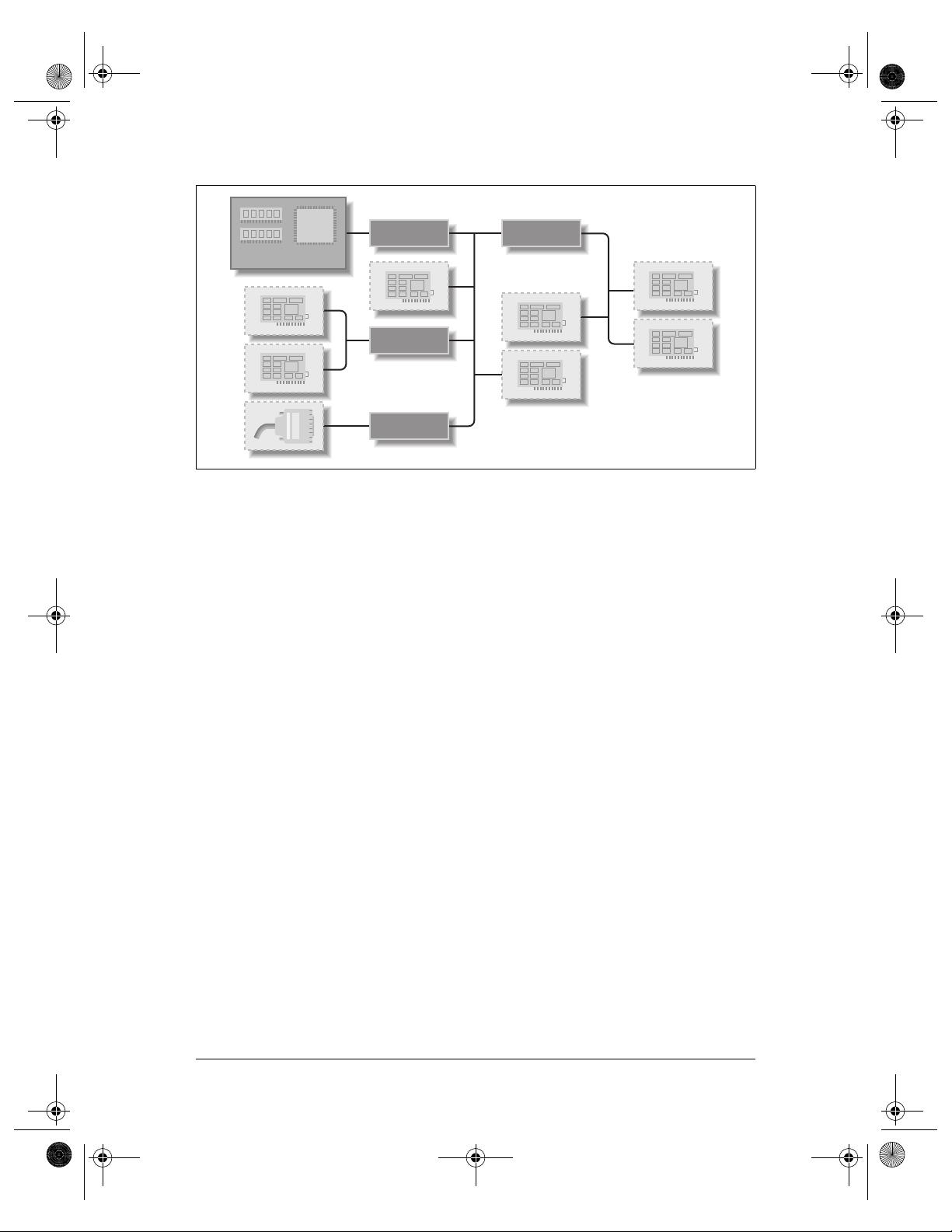

Most recent workstations feature at least two PCI buses. Plugging more than one bus

in a single system is accomplished by means of bridges, special-purpose PCI peripher-

als whose task is joining two buses. The overall layout of a PCI system is a tree where

each bus is connected to an upper-layer bus, up to bus 0 at the root of the tree. The

CardBus PC-card system is also connected to the PCI system via bridges. A typical

PCI system is represented in Figure 12-1, where the various bridges are highlighted.

The 16-bit hardware addresses associated with PCI peripherals, although mostly hid-

den in the

struct pci_dev object, are still visible occasionally, especially when lists of

devices are being used. One such situation is the output of lspci (part of the pciutils

package, available with most distributions) and the layout of information in /proc/pci

and /proc/bus/pci. The sysfs representation of PCI devices also shows this addressing

scheme, with the addition of the PCI domain information.

*

When the hardware

address is displayed, it can be shown as two values (an 8-bit bus number and an 8-bit

* Some architectures also display the PCI domain information in the /proc/pci and /proc/bus/pci files.

,ch12.1659 Page 303 Friday, January 21, 2005 3:08 PM

This is the Title of the Book, eMatter Edition

Copyright © 2005 O’Reilly & Associates, Inc. All rights reserved.

304

|

Chapter 12: PCI Drivers

device and function number), as three values (bus, device, and function), or as four

values (domain, bus, device, and function); all the values are usually displayed in

hexadecimal.

For example, /proc/bus/pci/devices uses a single 16-bit field (to ease parsing and sort-

ing), while /proc/bus/

busnumber splits the address into three fields. The following

shows how those addresses appear, showing only the beginning of the output lines:

$ lspci | cut -d: -f1-3

0000:00:00.0 Host bridge

0000:00:00.1 RAM memory

0000:00:00.2 RAM memory

0000:00:02.0 USB Controller

0000:00:04.0 Multimedia audio controller

0000:00:06.0 Bridge

0000:00:07.0 ISA bridge

0000:00:09.0 USB Controller

0000:00:09.1 USB Controller

0000:00:09.2 USB Controller

0000:00:0c.0 CardBus bridge

0000:00:0f.0 IDE interface

0000:00:10.0 Ethernet controller

0000:00:12.0 Network controller

0000:00:13.0 FireWire (IEEE 1394)

0000:00:14.0 VGA compatible controller

$ cat /proc/bus/pci/devices | cut -f1

0000

0001

0002

0010

0020

0030

Figure 12-1. Layout of a typical PCI system

PCI Bus 0 PCI Bus 1

Host Bridge PCI Bridge

ISA Bridge

CardBus Bridge

RAM CPU

,ch12.1659 Page 304 Friday, January 21, 2005 3:08 PM

This is the Title of the Book, eMatter Edition

Copyright © 2005 O’Reilly & Associates, Inc. All rights reserved.

The PCI Interface

|

305

0038

0048

0049

004a

0060

0078

0080

0090

0098

00a0

$ tree /sys/bus/pci/devices/

/sys/bus/pci/devices/

|-- 0000:00:00.0 -> ../../../devices/pci0000:00/0000:00:00.0

|-- 0000:00:00.1 -> ../../../devices/pci0000:00/0000:00:00.1

|-- 0000:00:00.2 -> ../../../devices/pci0000:00/0000:00:00.2

|-- 0000:00:02.0 -> ../../../devices/pci0000:00/0000:00:02.0

|-- 0000:00:04.0 -> ../../../devices/pci0000:00/0000:00:04.0

|-- 0000:00:06.0 -> ../../../devices/pci0000:00/0000:00:06.0

|-- 0000:00:07.0 -> ../../../devices/pci0000:00/0000:00:07.0

|-- 0000:00:09.0 -> ../../../devices/pci0000:00/0000:00:09.0

|-- 0000:00:09.1 -> ../../../devices/pci0000:00/0000:00:09.1

|-- 0000:00:09.2 -> ../../../devices/pci0000:00/0000:00:09.2

|-- 0000:00:0c.0 -> ../../../devices/pci0000:00/0000:00:0c.0

|-- 0000:00:0f.0 -> ../../../devices/pci0000:00/0000:00:0f.0

|-- 0000:00:10.0 -> ../../../devices/pci0000:00/0000:00:10.0

|-- 0000:00:12.0 -> ../../../devices/pci0000:00/0000:00:12.0

|-- 0000:00:13.0 -> ../../../devices/pci0000:00/0000:00:13.0

`-- 0000:00:14.0 -> ../../../devices/pci0000:00/0000:00:14.0

All three lists of devices are sorted in the same order, since lspci uses the /proc files as

its source of information. Taking the VGA video controller as an example,

0x00a0

means 0000:00:14.0 when split into domain (16 bits), bus (8 bits), device (5 bits) and

function (3 bits).

The hardware circuitry of each peripheral board answers queries pertaining to three

address spaces: memory locations, I/O ports, and configuration registers. The first

two address spaces are shared by all the devices on the same PCI bus (i.e., when you

access a memory location, all the devices on that PCI bus see the bus cycle at the

same time). The configuration space, on the other hand, exploits geographical

addressing. Configuration queries address only one slot at a time, so they never collide.

As far as the driver is concerned, memory and I/O regions are accessed in the usual

ways via inb, readb, and so forth. Configuration transactions, on the other hand, are

performed by calling specific kernel functions to access configuration registers. With

regard to interrupts, every PCI slot has four interrupt pins, and each device function

can use one of them without being concerned about how those pins are routed to the

CPU. Such routing is the responsibility of the computer platform and is imple-

mented outside of the PCI bus. Since the PCI specification requires interrupt lines to

be shareable, even a processor with a limited number of IRQ lines, such as the x86,

can host many PCI interface boards (each with four interrupt pins).

,ch12.1659 Page 305 Friday, January 21, 2005 3:08 PM

剩余24页未读,继续阅读

资源评论

高手不高

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【创新无忧】基于鸽群优化算法PIO优化广义神经网络GRNN实现光伏预测附matlab代码.rar

- 【创新无忧】基于鸽群优化算法PIO优化相关向量机RVM实现北半球光伏数据预测附matlab代码.rar

- 【创新无忧】基于鸽群优化算法PIO优化极限学习机KELM实现故障诊断附matlab代码.rar

- 【创新无忧】基于哈里斯鹰优化算法HHO优化广义神经网络GRNN实现数据回归预测附matlab代码.rar

- 【创新无忧】基于哈里斯鹰优化算法HHO优化广义神经网络GRNN实现电机故障诊断附matlab代码.rar

- 【创新无忧】基于哈里斯鹰优化算法HHO优化广义神经网络GRNN实现光伏预测附matlab代码.rar

- 【创新无忧】基于哈里斯鹰优化算法HHO优化相关向量机RVM实现北半球光伏数据预测附matlab代码.rar

- 【创新无忧】基于哈里斯鹰优化算法HHO优化极限学习机ELM实现乳腺肿瘤诊断附matlab代码.rar

- 【创新无忧】基于哈里斯鹰优化算法HHO优化极限学习机KELM实现故障诊断附matlab代码.rar

- 【创新无忧】基于哈里斯鹰优化算法HHO优化相关向量机RVM实现数据多输入单输出回归预测附matlab代码.rar

- 【创新无忧】基于海鸥优化算法SOA优化广义神经网络GRNN实现光伏预测附matlab代码.rar

- 【创新无忧】基于海鸥优化算法SOA优化广义神经网络GRNN实现电机故障诊断附matlab代码.rar

- 【创新无忧】基于海鸥优化算法SOA优化极限学习机ELM实现乳腺肿瘤诊断附matlab代码.rar

- 【创新无忧】基于海鸥优化算法SOA优化极限学习机KELM实现故障诊断附matlab代码.rar

- 【创新无忧】基于海鸥优化算法SOA优化广义神经网络GRNN实现数据回归预测附matlab代码.rar

- 【创新无忧】基于海洋捕食者优化算法MPA优化广义神经网络GRNN实现电机故障诊断附matlab代码.rar

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功