4.实验方法和步骤(含设计)

1、触发器之间的相互转换

在集成触发器的产品中,每一种触发器都有自己固定的逻辑功能。但可以

利用转换的方法获得具有其它功能的触发器。例如将 JK 触发器的 J、k 两端连

在一起,并认它为 T 端,就得到所需的 T 触发器,其状态方程为: Q

n+1

=T

Q

n

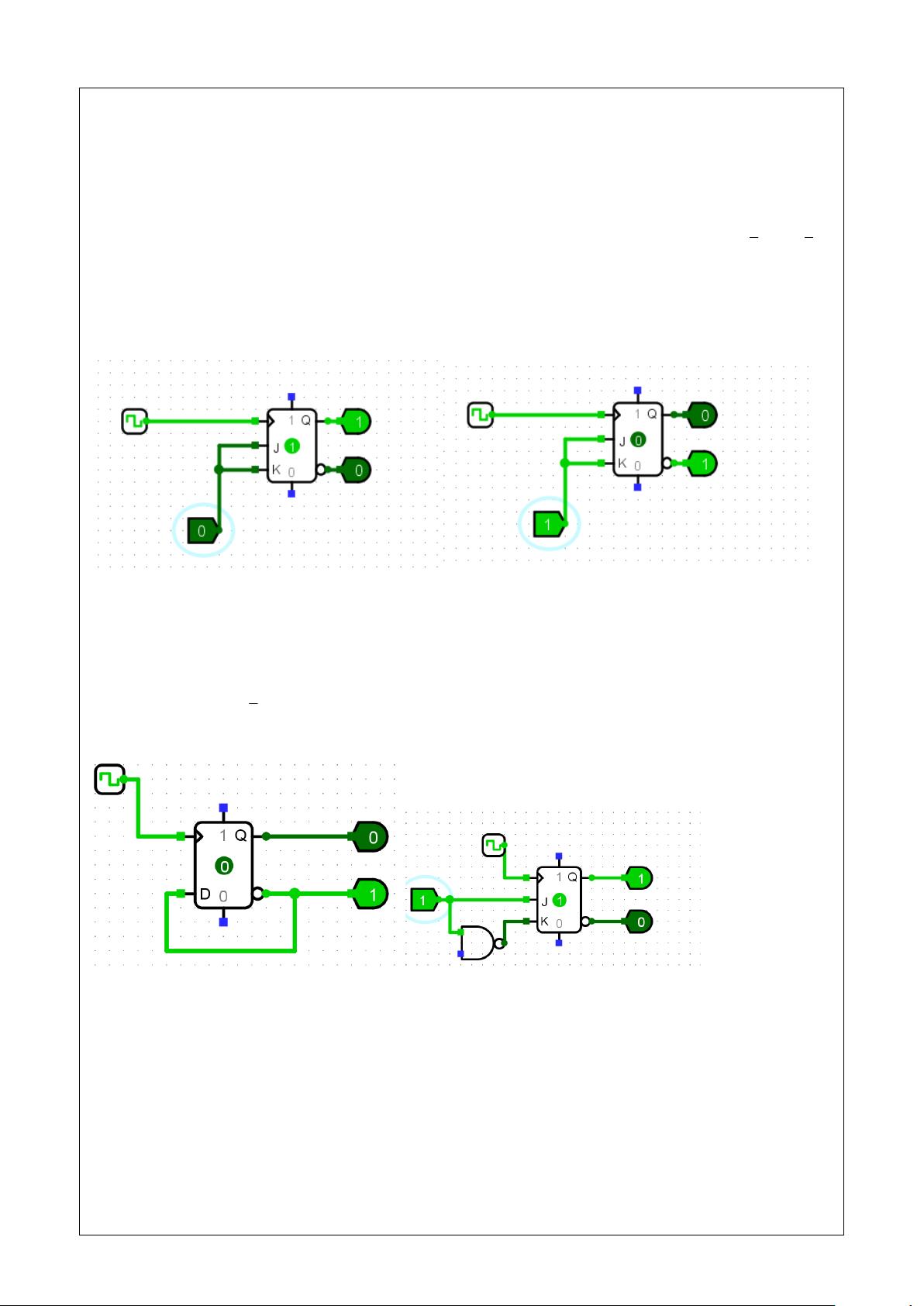

JK 触发器转化为 T 触发器:

由触发器的功能表可见,当 T=0 时,时钟脉冲作用后,其状态保持不变;当 T=1 时,时钟脉冲作用

后,触发器状态翻转。所以,若将 T 触发器的 T 端置“1”,如图 8-4(b)所示,即得 T'触发器。在 T'触发

器的 CP 端每来一个 CP 脉冲信号,触发器的状态就翻转一次,故称之为反转触发器,广泛用于计数电路

中。

同样,若将 D 触发器

端与 D 端相连,便转换成 T'触发器。

2. 单次脉冲触发器

用 74LS76 型 JK 功能触发器,设计一个单次脉冲发生器,要求将频率高的

系列脉冲信号和手控触发脉冲分别作为两个触发器的 CP 脉冲输入,只要手控脉

冲送出一个脉冲(高电平一次或低电平一次),单次脉冲发生器 就送出一个脉冲。

且该脉冲宽度与手控触发脉冲的时间长短无关。图是用 JK 触发器组成的单次脉

冲发生器电路图。