没有合适的资源?快使用搜索试试~ 我知道了~

pg046 Aurora 8B/10B

需积分: 0 1 下载量 139 浏览量

2024-10-30

22:40:09

上传

评论 2

收藏 2.67MB PDF 举报

温馨提示

pg046 Aurora 8B/10B

资源推荐

资源详情

资源评论

Aurora 8B/10B v11.1

LogiCORE IP Product Guide

Vivado Design Suite

PG046 October 19, 2023

AMD Adaptive Computing is creating an environment where

employees, customers, and partners feel welcome and included.

To that end, we’re removing non-inclusive language from our

products and related collateral. We’ve launched an internal

initiative to remove language that could exclude people or

reinforce historical biases, including terms embedded in our

software and IPs. You may still find examples of non-inclusive

language in our older products as we work to make these

changes and align with evolving industry standards. Follow this

link for more information.

Aurora 8B/10B v11.1 2

PG046 October 19, 2023

Table of Contents

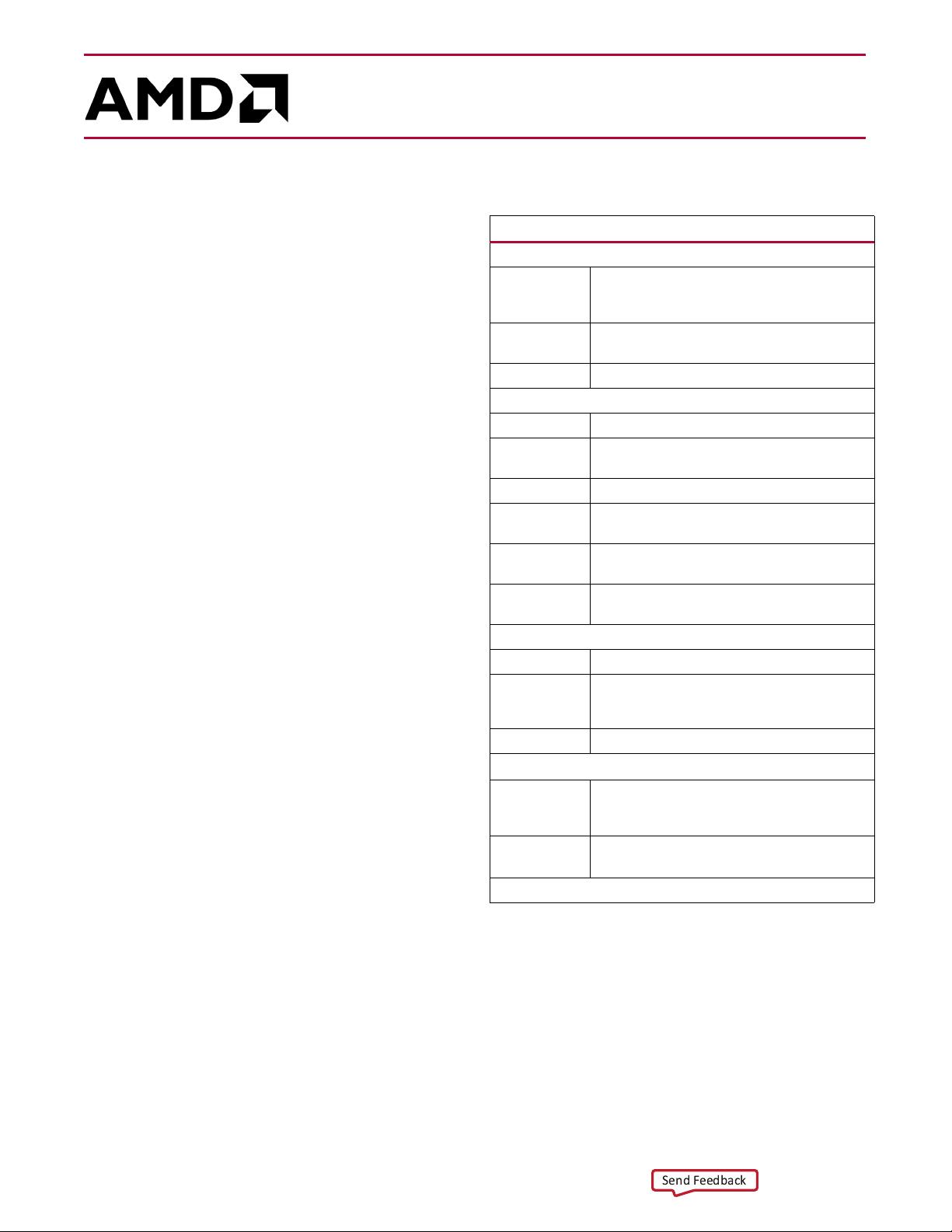

IP Facts

Chapter 1: Overview

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Licensing and Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 2: Product Specification

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Serial Transceiver Reference Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Reset and Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Shared Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Using the Scrambler/Descrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Using CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Hot-Plug Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Clock Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Using Little Endian Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Chapter 5: Detailed Example Design

Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Using the Vivado Design Suite Debug Feature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Send Feedback

Aurora 8B/10B v11.1 3

PG046 October 19, 2023

Chapter 6: Test Bench

Appendix A: Verification, Compliance, and Interoperability

Appendix B: Upgrading

Device Migration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Migrating Local Link-based Aurora Cores to the AXI4-Stream Aurora Core . . . . . . . . . . . . . . . . . . 91

Appendix C: Debugging

Finding Help with AMD Adaptive Computing Solutions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Next Step . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

AXI4-Stream Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Appendix D: Generating a Wrapper File from the Transceiver Wizard

Appendix E: Handling Timing Errors

Appendix F: Additional Resources and Legal Notices

Support Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Finding Additional Documentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Send Feedback

Aurora 8B/10B v11.1 4

PG046 October 19, 2023

Introduction

The AMD LogiCORE™ IP Aurora 8B/10B core

supports the AMBA® protocol AXI4-Stream

user interface. The core implements the Aurora

8B/10B protocol using the high-speed serial

transceivers on AMD Zynq™ 7000 SoC, AMD

Artix™ 7, AMD Kintex™ 7 and AMD Virtex™ 7

families, AMD UltraScale™ and AMD

UltraScale+

™ families.

Features

• General-purpose data channels with throughput

range from 480 Mbps to 84.48 Gbps

• Supports up to 16 consecutively bonded 7

series GTX/GTH, UltraScale™ GTH or UltraScale+

GTH transceivers and up to four bonded GTP

transceivers

• Aurora 8B/10B protocol specification v2.3

compliant

• Low resource cost (see Resource Utilization)

• Easy-to-use AXI4-Stream based framing (or

streaming) and flow control interfaces

• Automatically initializes and maintains the

channel

• Full-duplex or simplex operation

• 16-bit additive scrambler/descrambler

• 16-bit or 32-bit Cyclic Redundancy Check (CRC)

for user data

• Hot-plug logic

• Configurable DRP/INIT clock

• Single/Differential clocking option for

GTREFCLK and core INIT_CLK

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family

(1)

AMD UltraScale+™

(2)

, AMD UltraScale™

(2)

,

AMD Zynq™ 7000,

AMD 7 Series

(3)

Supported

User Interfaces

AXI4-Stream

Resources Performance and Resource Utilization web page

Provided with Core

Design Files Register transfer level (RTL)

Example

Design

Verilog and VHDL

(2)

Test Bench Verilog and VHDL

(4)

Constraints

File

Xilinx Design Constraints (XDC)

Simulation

Model

Source HDL with SecureIP transceiver simulation

models

Supported

S/W Driver

N/A

Tested Design Flows

(5)

Design Entry AMD Vivado™ Design Suite

Simulation

For supported simulators, see the

Vivado Design Suite User Guide: Release Notes,

Installation, and Licensing.

Synthesis Vivado Synthesis

Support

Release Notes

and Known

Issues

Master Answer Record: 54367

All Vivado IP

Change Logs

Master Vivado IP Change Logs: 72775

Support web page

Notes:

1. For a complete list of supported devices and configurations, see the

Vivado IP catalog and associated FPGA data sheets.

2. For more information, see the Virtex UltraScale FPGAs Data Sheet: DC

and AC Switching Characteristics (DS893) [Ref 20], Kintex UltraScale

FPGAs Data Sheet: DC and AC Switching Characteristics (DS892) [Ref 19],

Kintex UltraScale+ FPGAs Data Sheet: DC and AC Switching

Characteristics (DS922) [Ref 21], and Virtex UltraScale+ FPGAs Data

Sheet: DC and AC Switching Characteristics (DS923) [Ref 22].

3. For more information, see the 7 Series FPGAs Overview (DS180) [Ref 17]

and the UltraScale Architecture and Product Overview (DS890) [Ref 18].

4. The IP core is delivered as Verilog source code and comes with an

example design and supporting modules for simple simulation and

hardware demonstration.

5. For the supported versions of the tools, see the

Vivado Design Suite User Guide: Release Notes, Installation, and

Licensing.

Send Feedback

Aurora 8B/10B v11.1 5

PG046 October 19, 2023

Chapter 1

Overview

This guide describes how to generate an AMD LogiCORE™ IP Aurora 8B/10B core using

AMD UltraScale™ and UltraScale+™ family GTH transceivers, AMD Kintex™ 7, Virtex™ 7

FPGA GTX and GTH transceivers, AMD Artix™ 7 FPGA GTP transceivers, and AMD Zynq™

7000 device GTX and GTP transceivers. The Aurora 8B/10B core supports the AMBA®

protocol AXI4-Stream user interface.

The AMD Vivado™ Design Suite produces source code for Aurora 8B/10B cores with a

configurable datapath width. The cores can be simplex or full-duplex, and feature one of

two simple user interfaces and optional flow control.

The Aurora 8B/10B core (Figure 1-1) is a scalable, lightweight, link-layer protocol for

high-speed serial communication. The protocol is open and can be implemented using

AMD FPGA technology. The protocol is typically used in applications requiring simple,

low-cost, high-rate, data channels and is used to transfer data between devices using one

or many transceivers.

X-Ref Target - Figure 1-1

Figure 1‐1: Aurora 8B/10B Channel Overview

User

Application

Aurora Core Aurora Core

User

Application

User

Interface

User Data

Aurora

Lane 1

Aurora

Channel

Aurora

Lane n

User

Interface

User Data

X13009

8B/10B

Encoded Data

Aurora Channel

Partners

Send Feedback

剩余116页未读,继续阅读

资源评论

千寻xun

- 粉丝: 1w+

- 资源: 11

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 光储直流微电网Simulink仿真模型:双向DC-DC变换器能量管理与MPPT最大功率点跟踪技术探讨,光储直流微电网Simulink仿真模型:双向DC-DC变换器能量管理与MPPT控制策略应用,光储直

- COMSOL增材制造多层多道模拟教程及独家资料,内含高价专业模型和视频指南,COMSOL增材制造多层多道模拟:专业模型与视频教程分享,comsol增材制造多层多道模拟,同时附赠价值2k+以前学习 的

- 基于DL00350的CNN-LSTM模型:深度融合特征提取与长期依赖关系建模的用电量预测方法,基于DL00350的CNN-LSTM模型:深度融合特征提取与长期依赖关系建模的用电量预测方法,DL0035

- 电动汽车削峰填谷场景下的多目标充放电优化调度策略:综合负荷、电池损耗与峰谷平衡的三重优化求解,电动汽车削峰填谷多目标充放电优化调度策略详解:综合负荷、电池损耗与峰谷平衡优化研究,面向削峰填谷的电动汽车

- Comsol技术:折叠演示的未来应用探索,COMSOL软件的折叠功能演示及其动态应用体验,Comsol能带折叠演示 ,Comsol; 折叠; 演示,Comsol技术:可折叠演示的创新解决方案

- 基于超螺旋滑模观测器的高精度无传感器矢量控制-永磁无刷直流电机角度与转速的精确估算技术,基于超螺旋滑模观测器的高精度无传感器矢量控制-永磁无刷直流电机角度与转速的精确估算技术,基于超螺旋滑模观测器

- 基于TLBO算法优化混沌图像加密技术:利用图像摘要和SHA-512算法提高熵值,M00680:基于混沌映射与TLBO算法优化的高效图像加密策略,运用SHA-512计算图像摘要生成密钥,采用标准地图特殊

- 《Java开发,支持多端互通的高效客户管理CRM系统源码 - 整合Vue、Springboot与MySQL的解决方案》,Java语言开发的移动端CRM系统源码:支持手机端、小程序及全功能管理模块的Sp

- 风电叶片高精度动态数据测量与联合优化技术:无靶标标定、模态与应力分析的SOTA解决方案,高精度风电叶片动态数据测量解决方案:全参数联合优化与高效率数据跟踪分析,风电叶片动态数据测量 现场无需任何人工靶

- MATLAB环境下基于MCMC的贝叶斯稀疏盲反卷积算法:多场景信号处理与优化策略的研究与实践,MATLAB环境下基于MCMC的贝叶斯稀疏盲反卷积算法:在多领域信号处理中的通用性与实践应用,MATLAB

- 基于MATLAB R2018A环境的超声图像反卷积方法:基波和谐波图像处理及应用优化参数设置,MATLAB环境下超声图像反卷积方法的研究与实践:基于基波和谐波图像的算法优化与应用,MATLAB环境下基

- **基于SCNGO-CNN-LSTM的注意力机制数据分类预测程序:创新融合正余弦与折射反向学习算法**,**基于SCNGO-CNN-LSTM的注意力机制数据分类预测程序:创新融合正余弦与折射反向学习算

- 基于单片机与矩阵按键的门禁系统Proteus仿真程序:初始密码设置与电磁锁控制,基于单片机与矩阵按键的门禁系统Proteus仿真程序:六位数密码开锁与锁定键防错机制,单片机+1602+矩阵按键 门禁系

- 风光储并网控制系统的设计与Matlab Simulink仿真建模研究,风光储并网控制系统的设计与Matlab Simulink仿真建模研究,风光储并网控制系统,Matlab simulink仿真建模

- SVPWM调制Simulink离散模型:带死区补偿七段式对称发波,三相正弦波PWM调制算法推导文档附赠,SVPWM调制Simulink离散模型:高效死区补偿与三相正弦波PWM调制算法详解,SVPWM调

- Matlab仿真研究Hermite-Gaussian与Laguerre-Gaussian光束的传播特性,Matlab仿真研究Hermite-Gaussian与Laguerre-Gaussian光束的传

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功