40 Gbs高速串行接口接收机模拟前端电路设计.docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

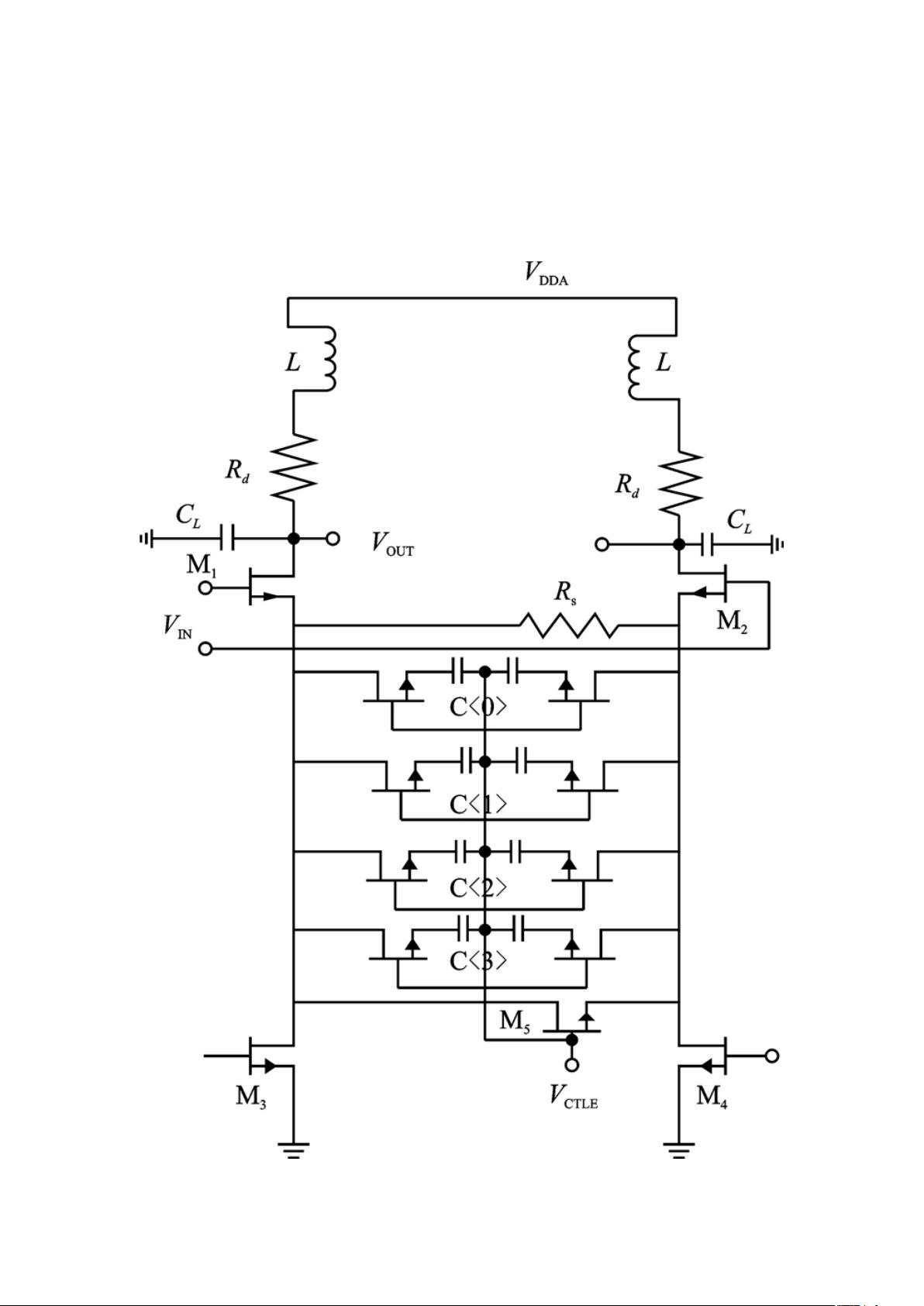

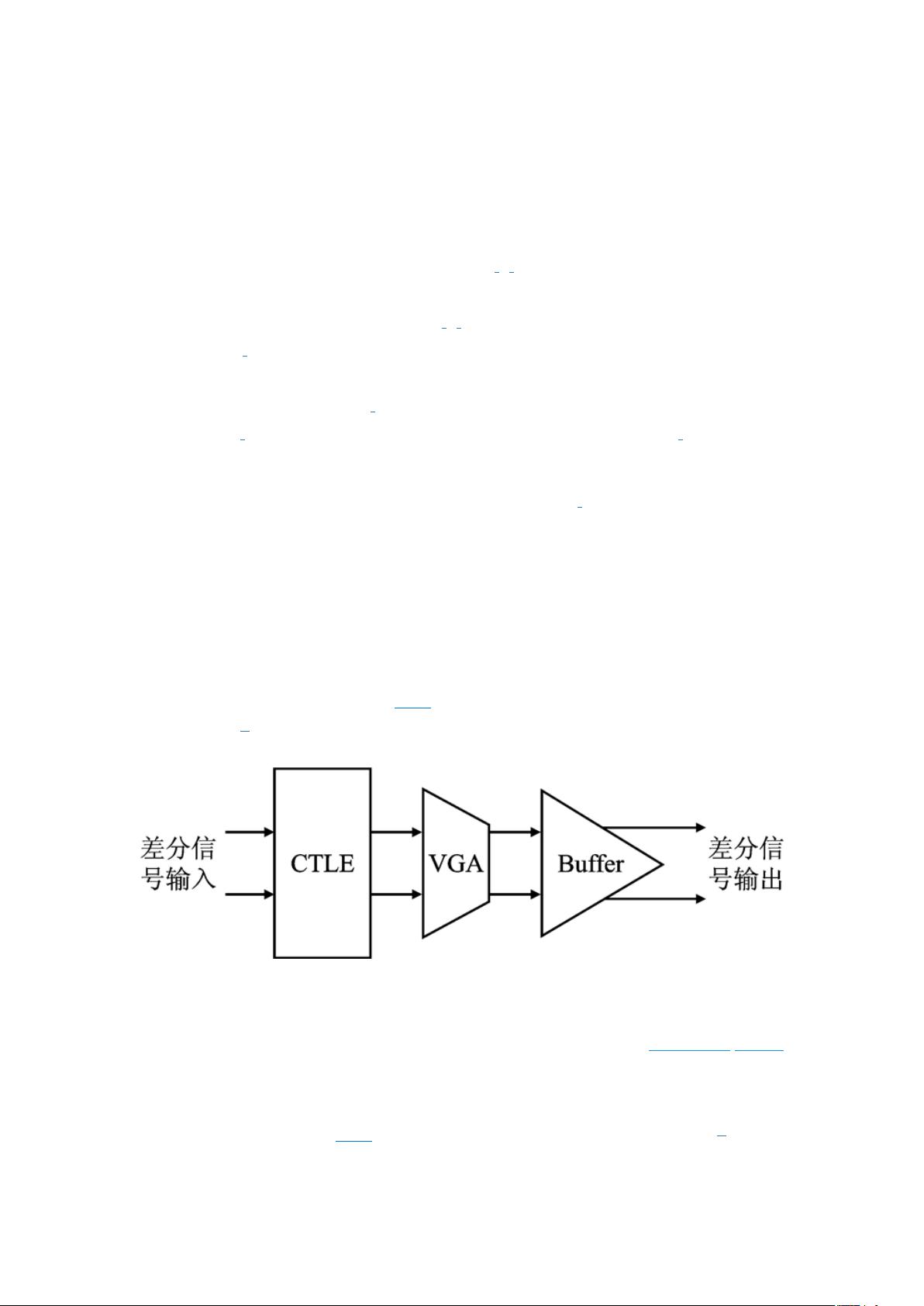

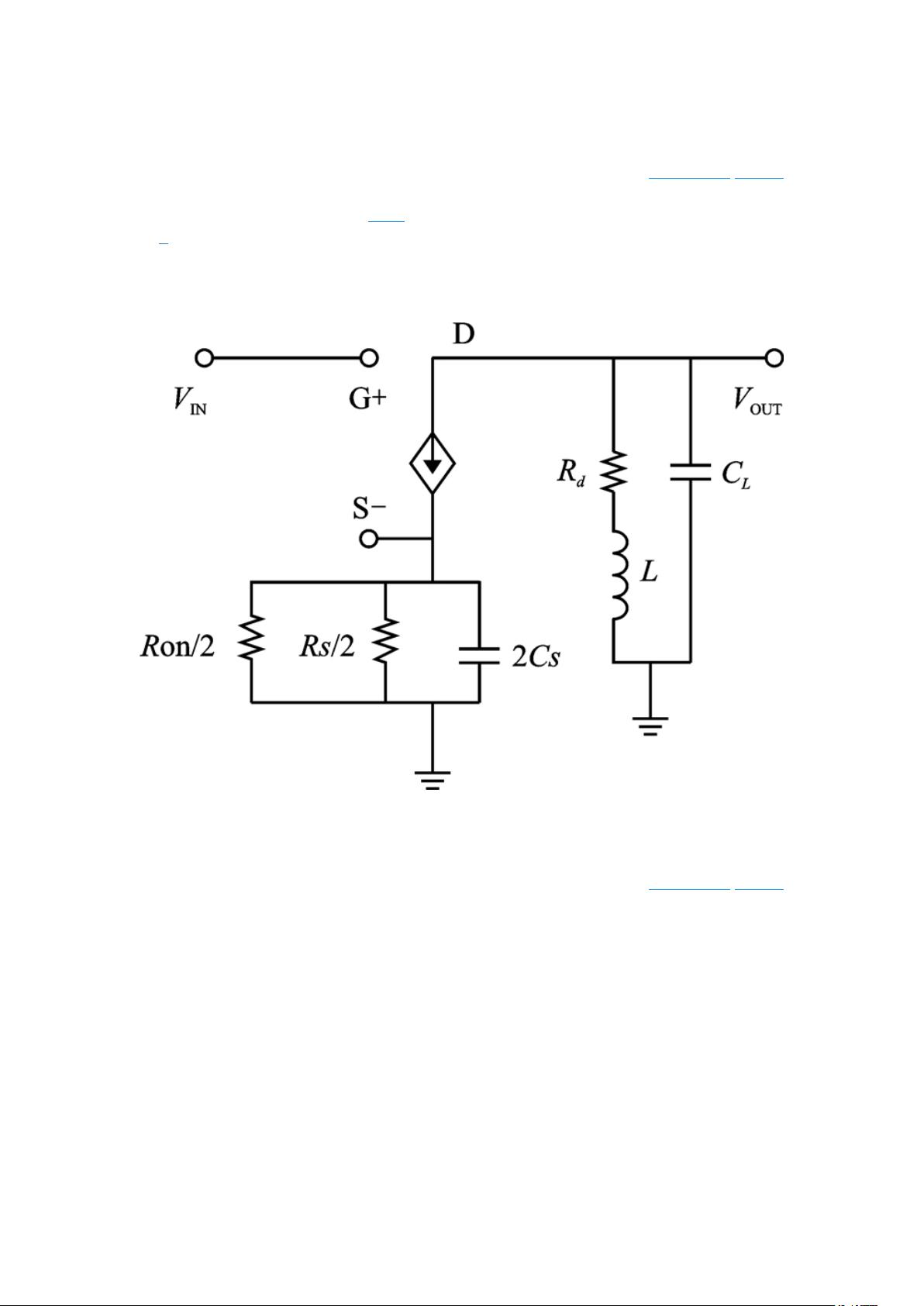

本文研究了40 Gbps高速串行接口接收机模拟前端电路设计,重点介绍了基于模拟数字转换器(Analog-to-Digital Converter,ADC)和数字信号处理器(Digital Signal Processor,DSP)的新结构,讨论了传统接收机结构和新的结构的优缺点,并详细介绍了CTLE电路设计和VGA增益可调、参数均衡设置的方法。 Knowledge Point 1: 传统接收机结构 vs 新结构 * 传统接收机结构:使用模拟电路,优点是延时短、功耗低、面积小;缺点是均衡能力有限,数据率较低,通常在56Gbps以下。 * 新结构:基于ADC和DSP,优点是均衡能力强,数据率高,能达到100 Gbps以上;缺点是功耗较高,延时较长。 Knowledge Point 2: CTLE电路设计 * CTLE电路原理图:采用电感峰化和源级负反馈电阻电容形式,电阻Rs和NMOS管M5并联构成源级负反馈电阻,改变M5管的栅极电压VCTLE可改变源极负反馈电阻的大小。 * CTLE小信号等效电路:忽略沟道调制效应和体效应,以简化公式推导,得到传输函数表达式。 * CTLE的直流增益和零极点之间存在折中关系,源极负反馈电阻和电容可进行调节。 Knowledge Point 3: VGA增益可调和参数均衡设置 * VGA在信号奈奎斯特频率范围内调整低频增益,补偿CTLE的衰减。 * 使用Buffer增加驱动能力,避免AFE级联DFE的负载较重的问题。 Knowledge Point 4: 模拟前端电路设计 * 模拟前端电路设计的总体结构框图:包括CTLE、VGA和Buffer三个部分。 * CTLE提高信号的高频增益,同时降低信号的低频增益。 * VGA在信号奈奎斯特频率范围内调整低频增益,补偿CTLE的衰减。 Knowledge Point 5: CTLE电路设计中的参数调整 * 源极负反馈电阻和电容可进行调节,以改变CTLE的零极点分布和直流增益。 * Rd和Cs的选择对CTLE的性能有重要影响。 Knowledge Point 6: 高速串行接口接收机模拟前端电路设计中的挑战 * 高速串行接口接收机模拟前端电路设计需要考虑数据率高、功耗低、面积小等多个方面的性能指标。 * 需要设计合适的CTLE电路和VGA增益可调、参数均衡设置,以满足高速串行接口接收机的性能要求。

剩余13页未读,继续阅读

- 粉丝: 4494

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功