没有合适的资源?快使用搜索试试~ 我知道了~

CMOS图像传感器的四通道扩展计数ADC设计.docx

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 175 浏览量

2022-11-30

09:30:20

上传

评论

收藏 698KB DOCX 举报

温馨提示

试读

14页

CMOS图像传感器的四通道扩展计数ADC设计.docx

资源推荐

资源详情

资源评论

1. 引言

采用列并行读出电路的 CMOS 图像传感器(CMOS Image Sensor, CIS)在高分辨率、高

速度、低噪声等方面具有优势

[1]

.这些特点使得 CMOS 图像传感器被广泛用于工业、安防、

生物医学、科研等领域.在科研领域的应用中,为了实现微弱图像信号的检测,对图像传感

器的性能有更高的要求,通常需要达到极低的噪声水平(<1e

-

)、高动态范围(>80dB)和高

灰度分辨率(>15 位)

[2]

.

常用于列读出电路的模数转换器(ADC)结构有单斜式 ADC、逐次逼近型(SAR)ADC、

循环型 ADC、ΔΣ ADC、增量型 ADC(Incremental ΔΣ ADC)以及扩展计数 ADC 等.其中,单

斜式 ADC 的转换速度慢,通常需要 2

n

个时钟周期来得到 n 位分辨率的转换结果,不适合

高速高精度图像传感器应用.高精度的 SAR ADC 由于需要大电容提高匹配性,不适合面积

敏感的图像传感器列读出电路应用.

增量型 ADC,也被称作增量型 ΔΣ ADC 或折叠积分(Folding Integration, FI)ADC

[3]

,在

转换时会对输入信号做多次的采样,即相关多采样技术(CMS).相关多采样技术在较高的多

采样次数下,能使 CMOS 图像传感器能够获得极低的噪声水平(<1e

-

),与相关双采样技术

(CDS)相比,能更好的满足科研领域图像传感器中低噪声读出电路的设计需求

[4]

.但一阶增量

型 ADC 在实现高分辨率时需要很高的采样次数,导致转换速度低,因此,通常在中低分

辨率增量型 ADC 之后,增加循环型 ADC、SAR ADC 等奈奎斯特率 ADC 作为第二级,组

成具有多级结构的扩展计数(Extended Counting, EC)ADC

[5-8]

,以此来扩展 ADC 的分辨率,

减少高分辨所需的采样次数和转换时间.

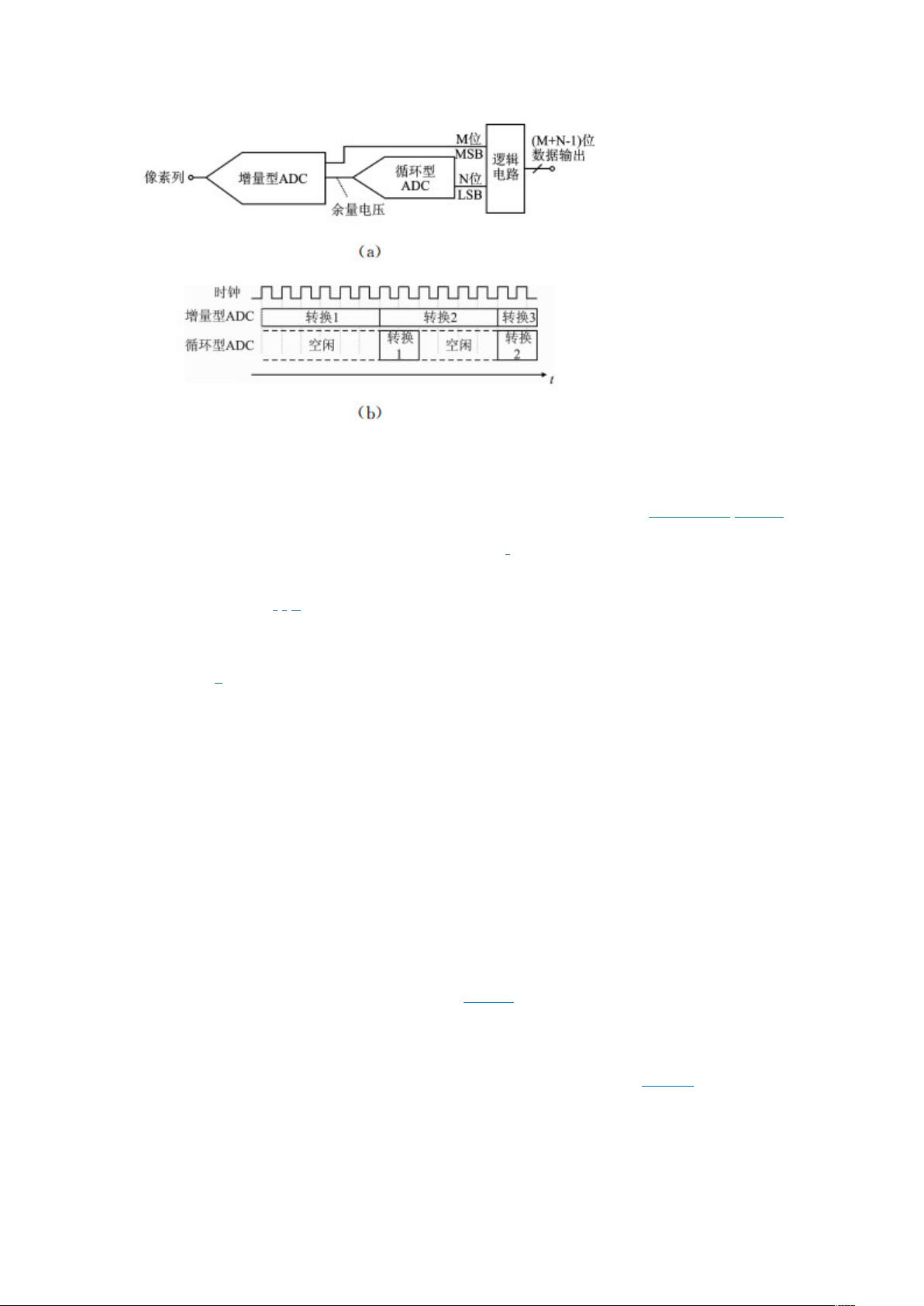

一种传统单通道扩展计数 ADC 的结构和工作时序如图 1.首先由增量型 ADC 对输入

进行 m 次相关多采样得到 M=log

2

(m)位的高有效位(MSB)和余量电压.然后由循环型 ADC 采

样余量电压,进行低有效位(LSB)的转换.但两级 ADC 均以运算放大器作为主要电路结构,

在图像传感器的读出电路阵列中占用了较大的芯片面积和功耗,限制了扩展计数 ADC 在

小像素、高分辨率图像传感器中的应用.

图 1 传统单通道扩展计数 ADC 电路结构及工作时序

Figure 1. Circuit structure and timing diagram of a conventional single-channelEC ADC

下载: 全尺寸图片 幻灯片

利用硬件复用的方式可以减小面积并提高能效

[9]

.扩展计数 ADC 中第一级增量型和第

二级循环型 ADC 具有类似的硬件电路结构,因此可通过在两级 ADC 间复用同一个运算放

大器实现硬件复用

[3, 6, 10]

,减小电路面积.但是,这种硬件复用的方法无法采用流水线等工作

方式,导致扩展计数 ADC 的转换速率较低.

文献[7]中采用 ADC 级联结构,实现了基于流水线工作方式的扩展计数 ADC 结构,

获得了转换速率的大幅提高,然而第一级增量型 ADC 的相关多采样次数不高,使其无法

满足科研领域对于低噪声和高动态范围的要求.

为了解决传统扩展计数 ADC 占用面积大,在高采样次数下转换速率低的问题,本文

提出了一种四通道扩展计数 ADC 结构,该结构通过在四个增量型 ADC 间复用同一个循环

型 ADC 的流水线方式,节省了列读出电路的面积,在高采样次数下保持较高的转换速

度,满足科研领域图像传感器的设计需求.

2. 四通道扩展计数 ADC 结构设计

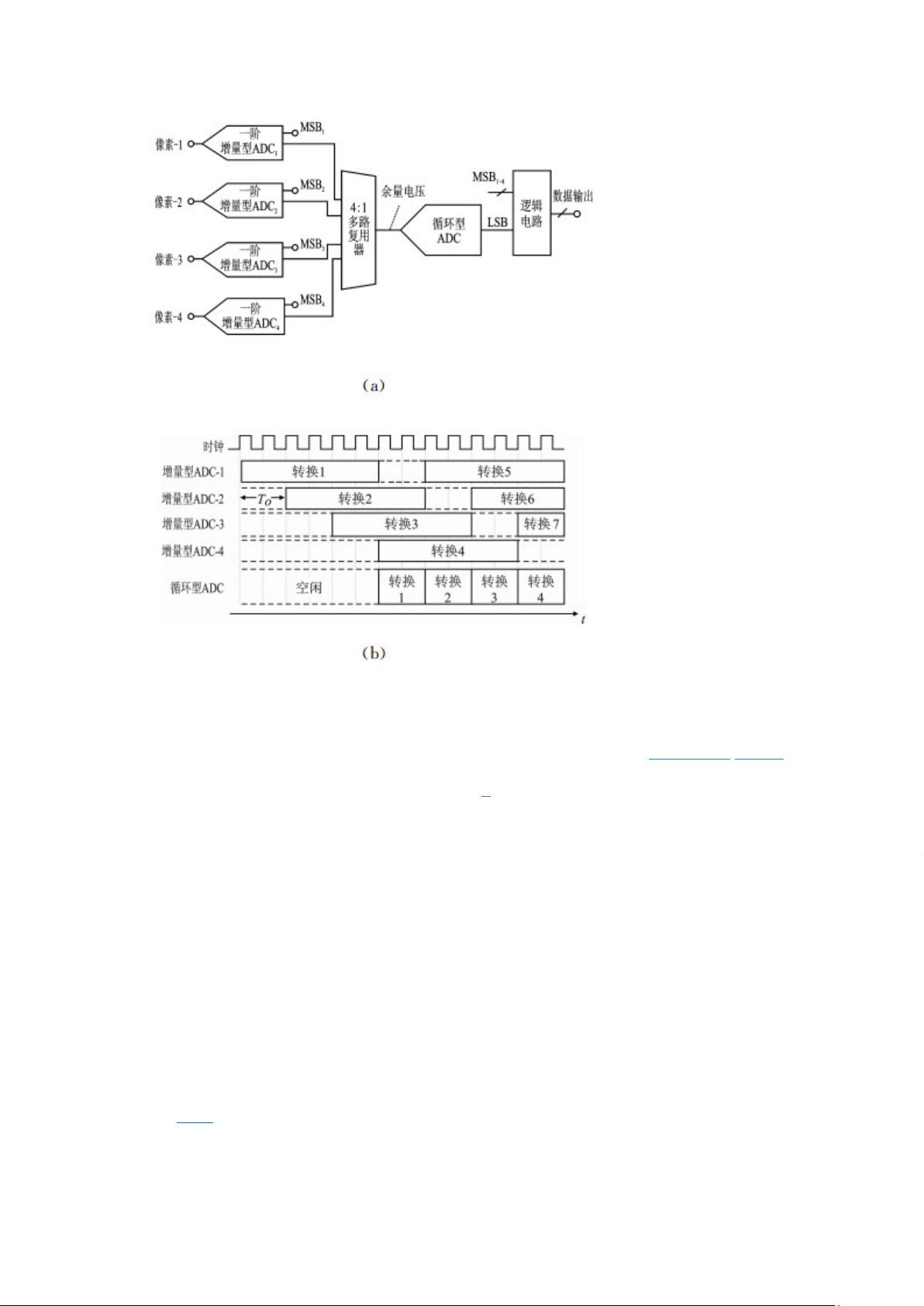

本文提出的四通道扩展计数 ADC 结构如图 2(a),通过在扩展计数 ADC 的第一级设

计 4 通道并行的结构,每个通道采用一个增量型 ADC 进行相关多采样,降低噪声.由于第

一级的转换时间通常远长于第二级循环型 ADC(大于 4 倍),因此可以通过复用同一个循环

型 ADC 的流水线方式来提高转换速率,从而减小列读出电路的面积.如图 2(b)所示,增量

型 ADC 之间以固定延时 T

o

作为间隔依次启动工作,4 个增量型 ADC 的余量电压由同一个

循环型 ADC 采样和转换,实现了高效的流水线运行.

图 2 四通道扩展计数 ADC 结构及工作时序

Figure 2. Structure and timing diagram of the 4-channel EC ADC

下载: 全尺寸图片 幻灯片

ADC 性能参数较多,通常采用如式(1)所示

[11]

品质因数(FoM)衡量 ADC 综合性能,综

合考虑了图像传感器读出电路关注的面积、功耗、转换速度以及动态范围等性能参数.

FoM=P×ConvTime×A10∣(DRdB−1.76)∣10[fJ⋅μm2conv.step]FoM=P×ConvTime×A10∣(DRdB−1.76)∣10[fJ⋅μm2conv.step]

(1)

式中,P 为功耗; ConvTime 是 ADC 的转换时间; A 为 ADC 的面积; DR

dB

是 ADC 的动

态范围.越小的品质因数代表了越好的设计,品质因数受到通道个数 n 和多采样次数 m 的影

响,需要通过对结构进行分析以确定扩展计数 ADC 设计中最优的通道个数和相关多采样

次数.

对于 n 列像素的 ADC 读出电路,有 n 列并行传统单通道扩展计数 ADC 和 n 通道扩展

计数 ADC 两种结构,两者性能差异主要体现在转换时间和面积上.以下对两种结构进行分

析和对比.

表 1 给出了 n 列并行单通道结构和 n 通道扩展计数结构的 ADC 参数计算方式,其中

f

1

和 f

2

分别表示 ADC 第一级和第二级的采样率; A

1

和 A

2

分别表示 ADC 第一级和第二级电

剩余13页未读,继续阅读

资源评论

罗伯特之技术屋

- 粉丝: 3541

- 资源: 1万+

下载权益

C知道特权

VIP文章

课程特权

开通VIP

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功