Tomasulo 算法

1、实验目的

(1)加深对指令级并行性及其开发的理解。

(2)加深对 Tomasulo 算法的理解。

(3)掌握 Tomasulo 算法在指令流出、执行、写回各阶段对浮点指令和 Load/ Store

指令进行的操作。

(4)掌握采用了 Tomasulo 算法的浮点处理部件的结构。

(5)掌握保留站的结构

(6)给定被执行代码片段,对于具体某个时钟周期,能够写出保留站、指令状

态表以及浮点寄存器状态表内容的变化情况。

2、实验平台

实验平台采用 Tomasulo 算法模拟器。

3、实验内容

(1)假设浮点功能部件的延迟时间为:加减法 2 个时钟周期,乘法 10 个时钟

周期,除法 40 个时钟周期,Load 部件 2 个时钟周期。

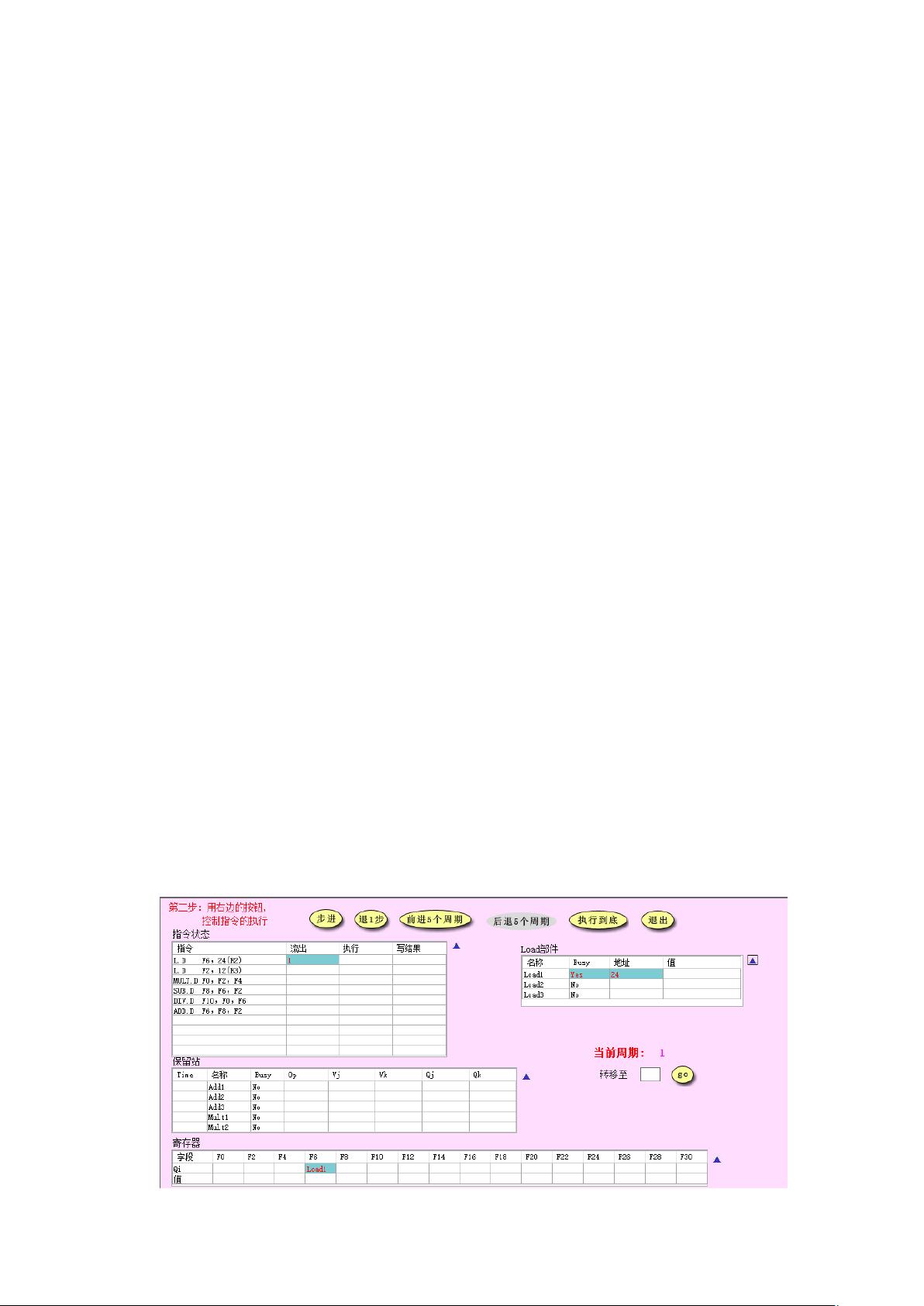

① 对于下面的代码段,给出当指令 MUL.D 即将写回时,保留站、Load 缓冲

器以及寄存器状态表中的内容。

L.D F6, 24(R2)

L.D F2, 12(R3)

MUL.D F0, F2, F4

SUB.D F8, F6, F2

DIV.D F10, F0, F6

ADD.D F6, F8, F2

②按步进方式执行上述代码,利用模拟器的“小三角按钮”的对比显示功能,

观察每一个时钟周期前后各信息表中内容的变化情况。

周期 1:取出第一条指令 L.D F6, 24(R2),地址偏移量 24 写入 LOAD 部件中的

LOAD1 并且将 LOAD1 名存入寄存器字段 F6 中。

评论1

最新资源