DS25MB200

SNLS220G –MARCH 2006–REVISED APRIL 2013

www.ti.com

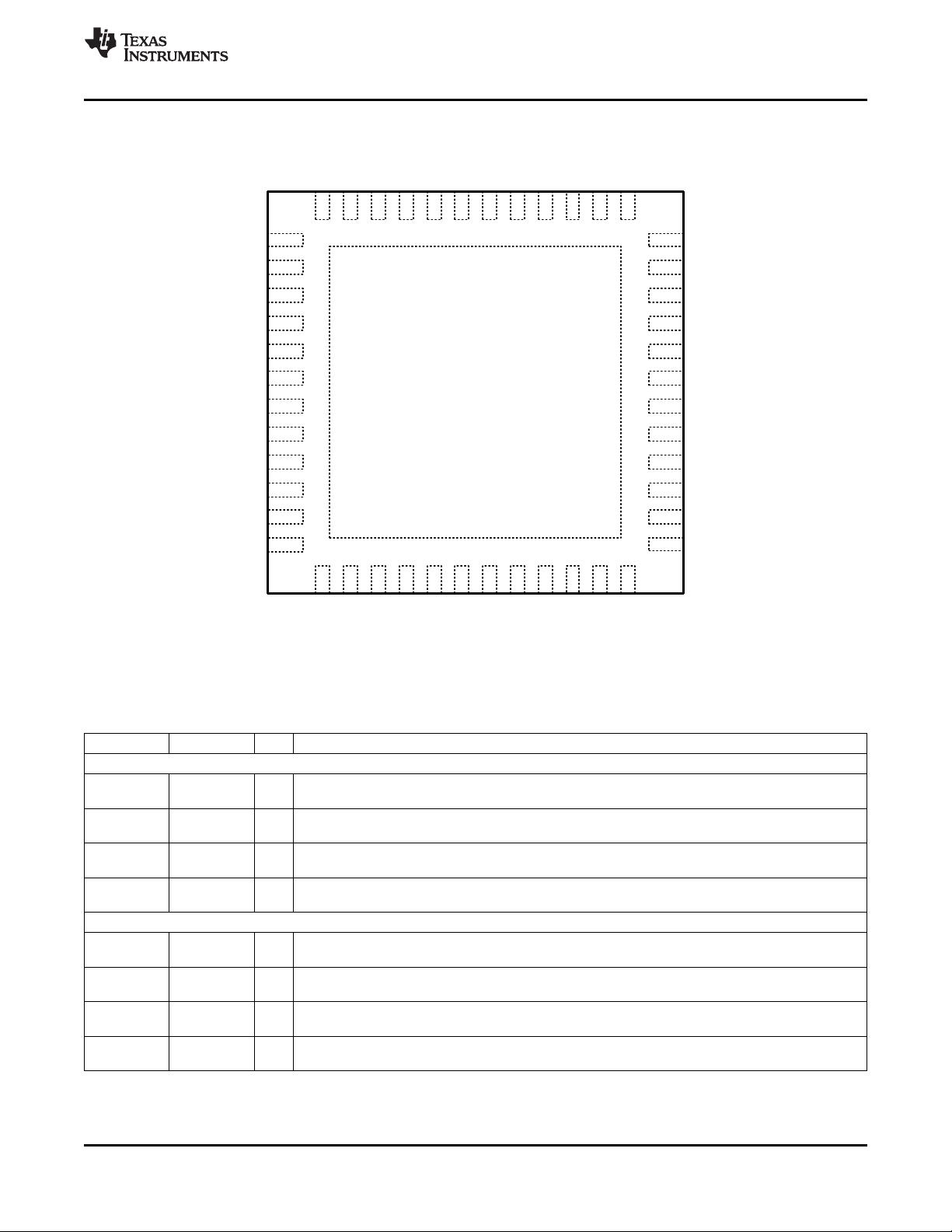

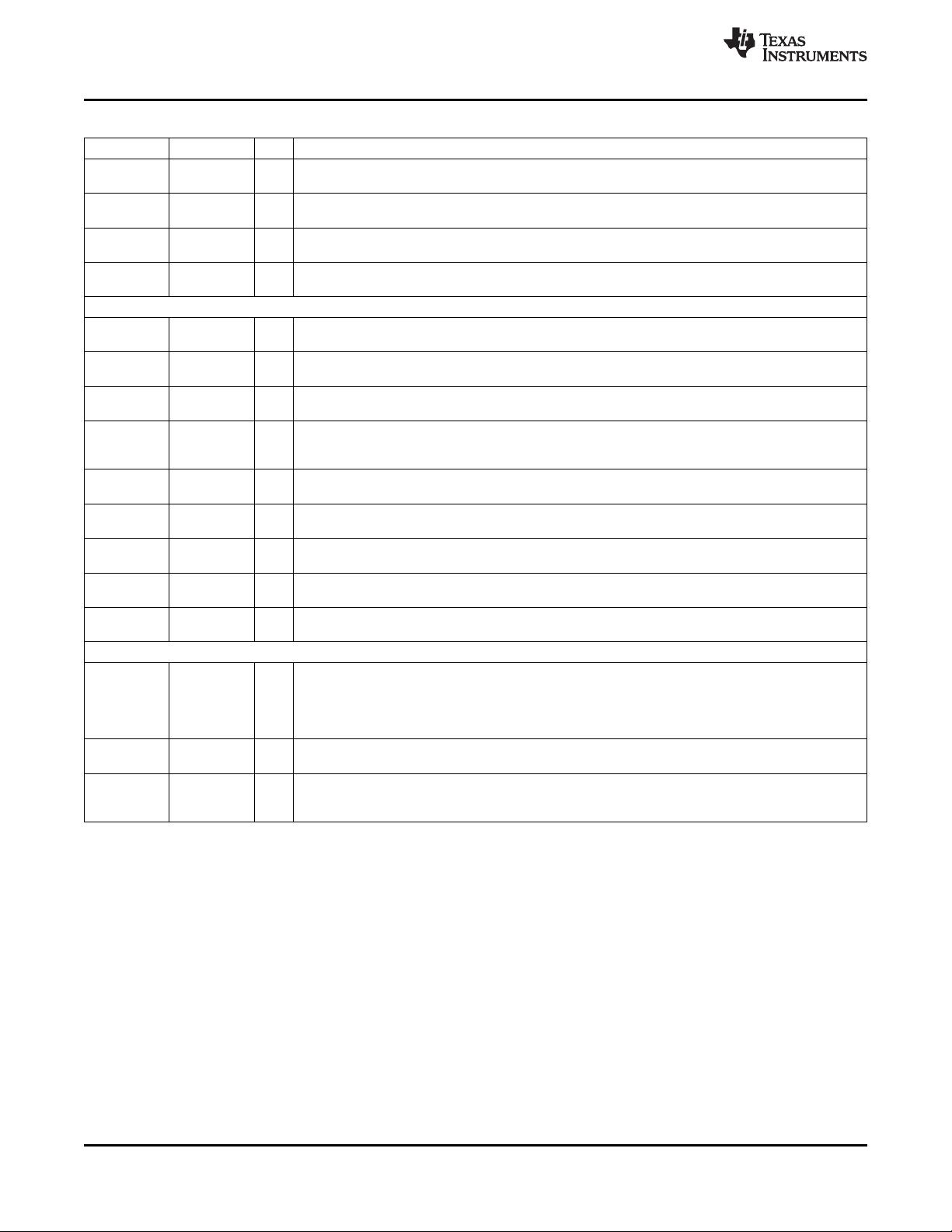

PIN DESCRIPTIONS

(1)

(continued)

Pin Name Pin Number I/O

(2)

Description

SOA_1+ 22 O Inverting and non-inverting differential outputs of mux_1 at the switch_A side. SOA_1+ and SOA_1−

SOA_1− 21 have an internal 50Ω connected to V

CC

.

SOB_1+ 28 O Inverting and non-inverting differential outputs of mux_1 at the switch_B side. SOB_1+ and SOB_1−

SOB_1− 27 have an internal 50Ω connected to V

CC

.

SIA_1+ 16 I Inverting and non-inverting differential inputs to the mux_1 at the switch_A side. SIA_1+ and SIA_1−

SIA_1− 15 have an internal 50Ω connected to an internal reference voltage. See Figure 7.

SIB_1+ 19 I Inverting and non-inverting differential inputs to the mux_1 at the switch_B side. SIB_1+ and SIB_1−

SIB_1− 18 have an internal 50Ω connected to an internal reference voltage. See Figure 7.

CONTROL (3.3V LVCMOS)

MUX_S0 37 I A logic low at MUX_S0 selects mux_0 to switch B. MUX_S0 is internally pulled high. Default state for

mux_0 is switch A.

MUX_S1 13 I A logic low at MUX_S1 selects mux_1 to switch B. MUX_S0 is internally pulled high. Default state for

mux_1 is switch A.

PREL_0 12 I PREL_0 and PREL_1 select the output pre-emphasis of the line side drivers (LO_0± and LO_1±).

PREL_1 1 PREL_0 and PREL_1 are internally pulled high. See Table 3 for line side pre-emphasis levels.

PRES_0 36 I PRES_0 and PRES_1 select the output pre-emphasis of the switch side drivers (SOA_0±, SOB_0±,

PRES_1 25 SOA_1± and SOB_1±). PRES_0 and PRES_1 are internally pulled high. See Table 4 for switch side

pre-emphasis levels.

LB0A 47 I A logic low at LB0A enables the internal loopback path from SIA_0± to SOA_0±. LB0A is internally

pulled high.

LB0B 48 I A logic low at LB0B enables the internal loopback path from SIB_0± to SOB_0±. LB0B is internally

pulled high.

LB1A 23 I A logic low at LB1A enables the internal loopback path from SIA_1± to SOA_1±. LB1A is internally

pulled high.

LB1B 24 I A logic low at LB1B enables the internal loopback path from SIB_1± to SOB_1±. LB1B is internally

pulled high.

RSV 26 I Reserve pin to support factory testing. This pin can be left open, or tied to GND, or tied to GND

through an external pull-down resistor.

POWER

V

CC

2, 8, 14, 20, P V

CC

= 3.3V ± 5%.

29, 35, 38, Each V

CC

pin should be connected to the V

CC

plane through a low inductance path, typically with a

44 via located as close as possible to the landing pad of the V

CC

pin.

It is recommended to have a 0.01 μF or 0.1 μF, X7R, size-0402 bypass capacitor from each V

CC

pin

to ground plane.

GND 5, 11, 17, 32, P Ground reference. Each ground pin should be connected to the ground plane through a low

41 inductance path, typically with a via located as close as possible to the landing pad of the GND pin.

GND DAP P Die Attach Pad (DAP) is the metal contact at the bottom side, located at the center of the WQFN-48

package. It should be connected to the GND plane with at least 4 via to lower the ground impedance

and improve the thermal performance of the package.

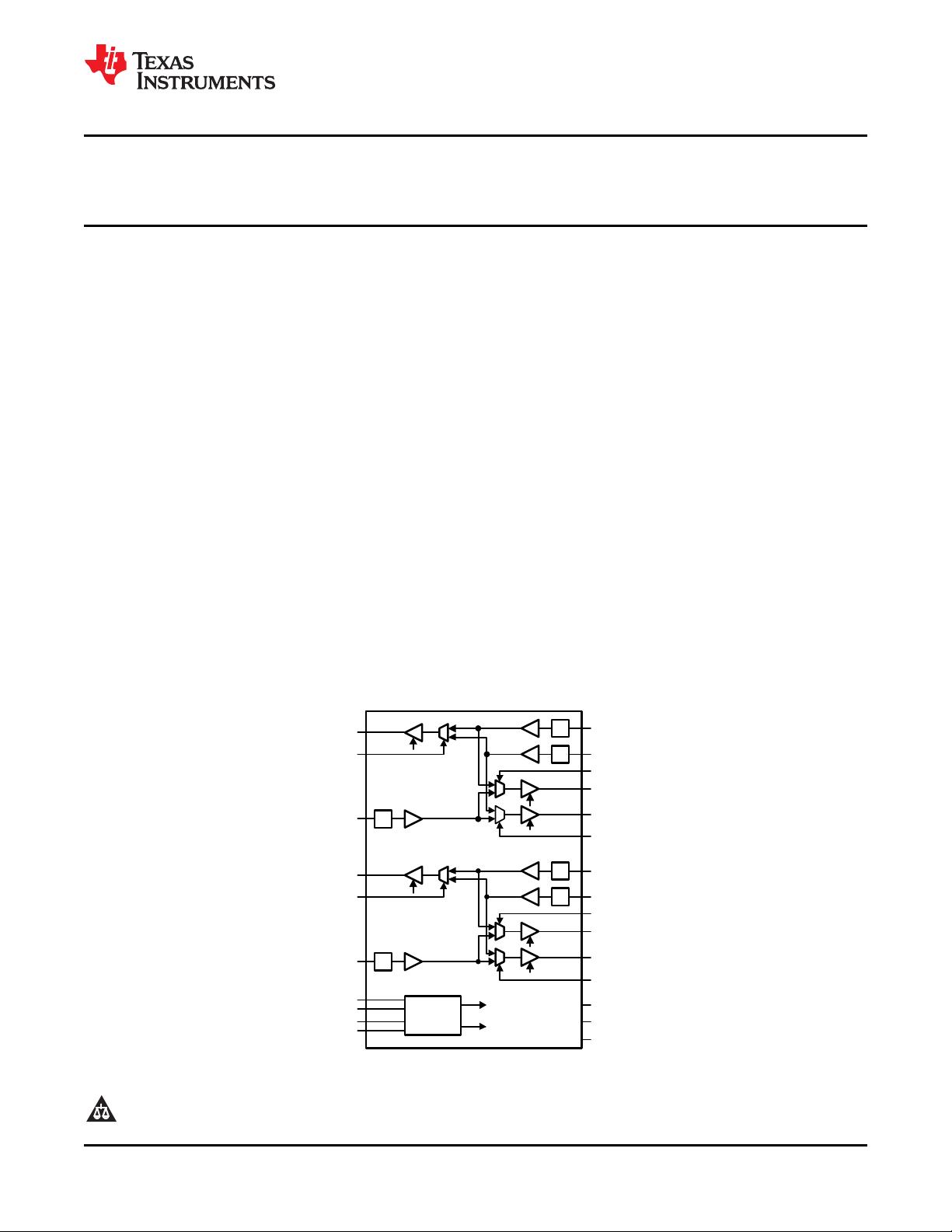

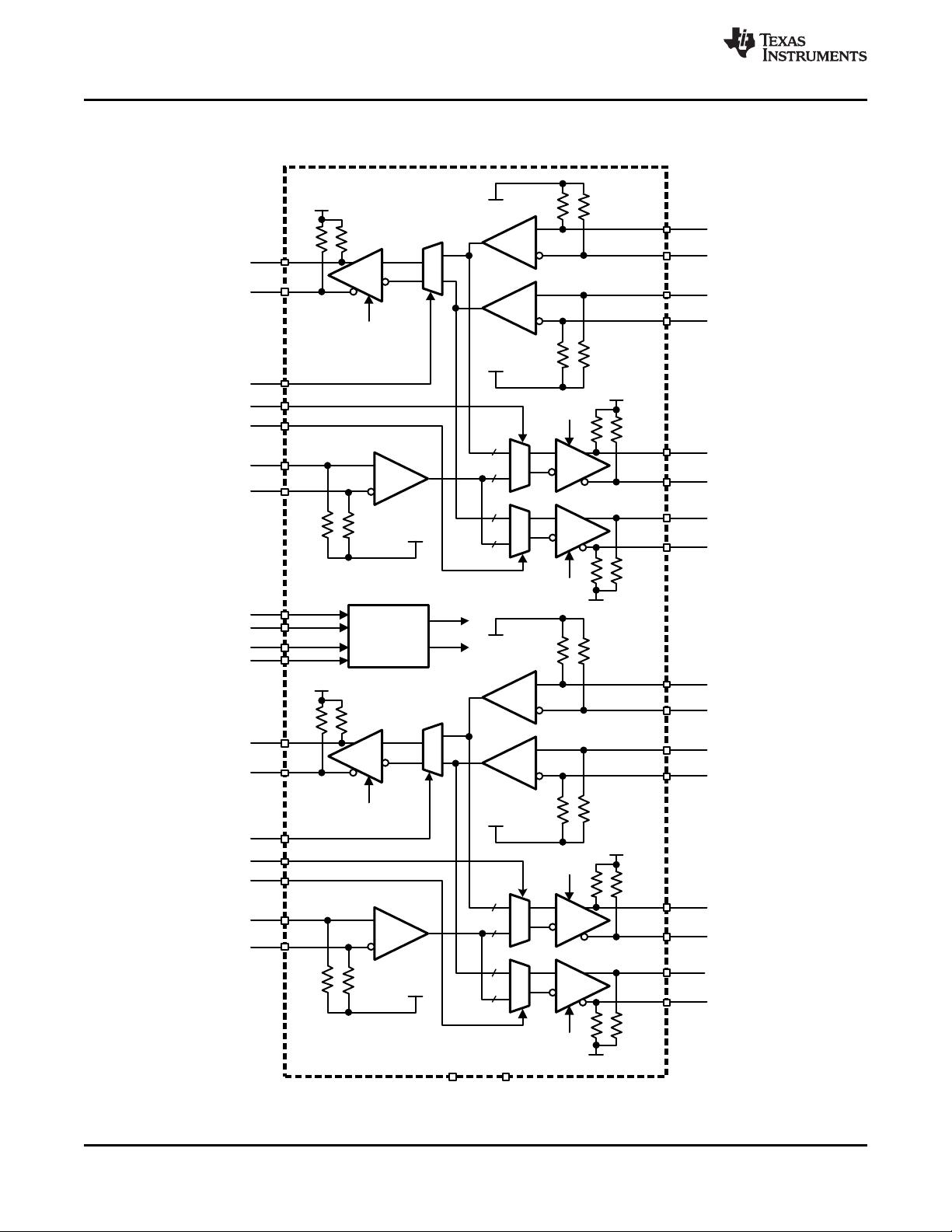

Functional Description

The DS25MB200 is a signal conditioning 2:1 multiplexer and a 1:2 buffer designed to support port redundancy up

to 2.5 Gbps. The high speed inputs are self-biased to about 1.3V and are designed for AC coupling. See

Figure 7 for details. The inputs are compatible to most AC coupling differential signals such as LVDS, LVPECL

and CML. The DS25MB200 is not designed to operate with data rates below 250 Mbps or with a DC bias applied

to the CML inputs or outputs. Most high speed links are encoded for DC balance and have been defined to

include AC coupling capacitors allowing the DS25MB200 to be directly inserted into the datapath without any

limitation. The ideal AC coupling capacitor value is often based on the lowest frequency component embedded

within the serial link. A typical AC coupling capacitor value ranges between 100 and 1000nF. Some

specifications with scrambled data may require a larger capacitor for optimal performance. To reduce unwanted

parasitics around and within the AC coupling capacitor, a body size of 0402 is recommended. Figure 6 shows the

AC coupling capacitor placement in an AC test circuit.

4 Submit Documentation Feedback Copyright © 2006–2013, Texas Instruments Incorporated

Product Folder Links: DS25MB200

qq_335607272023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

qq_335607272023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 m0_745259962023-02-15#完美解决问题 #运行顺畅 #内容详尽 #注释完整

m0_745259962023-02-15#完美解决问题 #运行顺畅 #内容详尽 #注释完整 CSDN_1872023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

CSDN_1872023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功