没有合适的资源?快使用搜索试试~ 我知道了~

TI-SN3257-Q1.pdf

需积分: 9 1 下载量 94 浏览量

2022-12-01

23:28:05

上传

评论 4

收藏 1.87MB PDF 举报

温馨提示

试读

37页

TI-SN3257-Q1.pdf

资源推荐

资源详情

资源评论

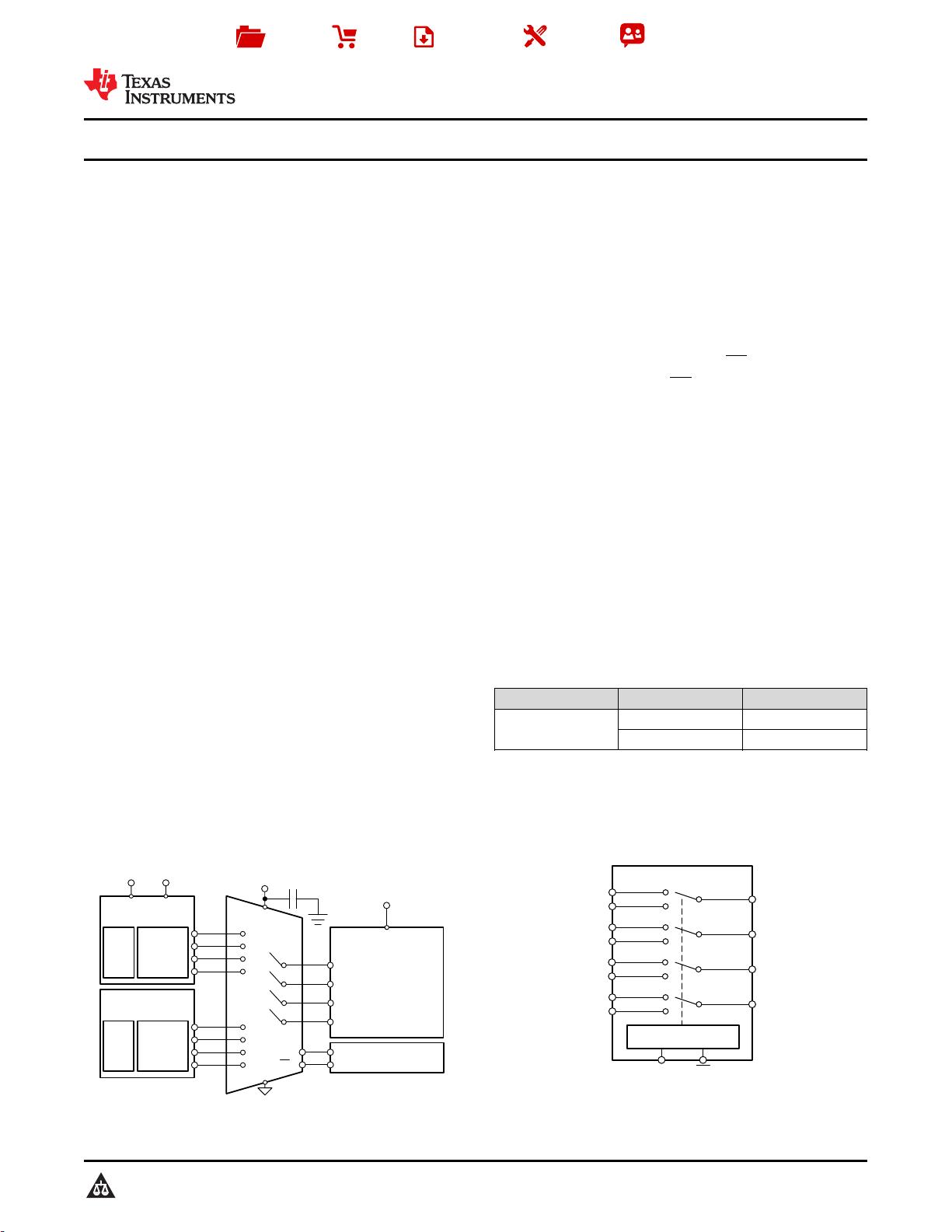

SPI / eSIM / eMMC

Device

GND

V

DD

1.8V Control Logic

From Processor / MCU

SEL

0.1µF

EN

S1B

S2B

S3B

S4B

Processor / MCU /

Ext ernal Hea der #2

S1A

S2A

S3A

S4A

Processor / MCU /

Ext ernal Hea der #1

MISO / CMD / GPIO

MOSI / CLK / GPIO

SCLK / DAT0 / GPIO

SS / DAT1 / GPIO

PORT

DEBUG,

SPI, GPIO

1.8V

Logic

I/O

PORT

DEBUG,

SPI, GPIO

1.8V

Logic

I/O

V

I/O

V

DD

D4

D3

D2

D1

V

DD

SN325 7-Q1

SEL

S1A

D1

S1B

S2A

S2B

S3A

S3B

S4A

S4B

EN

LOGIC CONTRO L*

D2

D3

D4

*Internal 6MOPull-Down on Logic Pins

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。 有关适用的官方英文版本的最新信息,请访问 www.ti.com,其内容始终优先。 TI 不保证翻译的准确

性和有效性。 在实际设计之前,请务必参考最新版本的英文版本。

English Data Sheet: SCDS411

SN3257-Q1

ZHCSK05B –JULY 2019–REVISED JANUARY 2020

具具有有 1.8V 逻逻辑辑的的 SN3257-Q1 5V 低低传传播播延延迟迟、、2:1 (SPDT) 4 通通道道开开关关

1

1 特特性性

1

• 符合汽车应用的 AEC-Q100

– 温度等级 1:-40°C 至 +125°C,T

A

• 宽电源范围:1.5V 至 5.5V

• 低传播延迟:78ps

• 低导通电阻:5Ω

• 高带宽:1.2GHz

• 双向信号路径

• 支持超出电源电压范围的输入电压

• 兼容 1.8V 逻辑

• 逻辑引脚上的集成下拉电阻器

• 失效防护逻辑

• 高达 3.6V 信号的关断保护

2 应应用用

• SPI 多路复用

• I2S 多路复用

• eSIM 多路复用

• eMMC 多路复用

• 闪存存储器共享

• 电池管理系统 (BMS)

• 远程信息处理控制单元 (TCU)

• 智能远程信息处理网关

• 后座娱乐系统

• 数字驾驶舱处理单元

• 汽车音响主机

• 汽车导航

• ADAS 域控制器

• 环视系统 ECU

• 板载充电器 (OBC) 和无线充电器

3 说说明明

SN3257-Q1 是一款汽车级互补金属氧化物半导体

(CMOS) 开关,支持高速信号,具有低传播延迟。

SN3257-Q1 提供具有 4 个通道的 2:1 (SPDT) 开关配

置,非常适合 SPI 和 I2S 等各通道协议。此器件可在

源极(SxA、SxB)和漏极 (Dx) 引脚上支持双向模拟

和数字信号,并且能够传递高于电源电压(最高 V

DD

x

2)的信号,最大输入和输出电压为 5.5V。

SN3257-Q1 具有一个低电平有效 EN 引脚,用于同时

启用和禁用所有通道。当 EN 引脚为低电平时,会根据

SEL 引脚的状态选择两个开关路径之一。

SN3257-Q1 的信号路径上高达 3.6V 的关断保护功能

可在移除电源电压 (V

DD

= 0V) 时提供隔离。如果没有

该保护功能,开关可通过内部 ESD 二极管为电源轨进

行反向供电,从而对系统造成潜在损坏。

失效防护逻辑电路允许在施加电源引脚上的电压之前,

先施加逻辑控制引脚上的电压,从而保护器件免受潜在

的损害。两个逻辑控制输入都具有兼容 1.8V 逻辑的阈

值,可确保 TTL 和 CMOS 逻辑兼容性。逻辑引脚上带

有集成下拉电阻器,无需外部组件,可减小系统尺寸、

降低系统成本。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

SN3257-Q1

TSSOP (16) 5.00mm × 4.40mm

SOT-23-THIN (16) 4.20mm x 2.00mm

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

应应用用示示例例 方方框框图图

2

SN3257-Q1

ZHCSK05B –JULY 2019–REVISED JANUARY 2020

www.ti.com.cn

Copyright © 2019–2020, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 4

6.1 Absolute Maximum Ratings ...................................... 4

6.2 ESD Ratings.............................................................. 4

6.3 Recommended Operating Conditions....................... 4

6.4 Thermal Information.................................................. 4

6.5 Electrical Characteristics........................................... 5

6.6 Dynamic Characteristics ........................................... 6

6.7 Timing Requirements................................................ 7

6.8 Typical Characteristics.............................................. 8

7 Parameter Measurement Information ................ 11

7.1 On-Resistance ........................................................ 11

7.2 Off-Leakage Current ............................................... 11

7.3 On-Leakage Current ............................................... 12

7.4 I

POFF

Leakage Current............................................ 12

7.5 Transition Time ....................................................... 13

7.6 t

ON (EN)

and t

OFF (EN)

Time....................................... 13

7.7 t

ON (VDD)

and t

OFF (VDD)

Time................................... 14

7.8 Break-Before-Make Delay....................................... 14

7.9 Propagation Delay................................................... 15

7.10 Skew ..................................................................... 15

7.11 Charge Injection.................................................... 16

7.12 Capacitance .......................................................... 16

7.13 Off Isolation........................................................... 17

7.14 Channel-to-Channel Crosstalk.............................. 17

7.15 Bandwidth ............................................................. 18

8 Detailed Description............................................ 19

8.1 Overview ................................................................. 19

8.2 Functional Block Diagram ....................................... 19

8.3 Feature Description................................................. 19

8.4 Device Functional Modes........................................ 21

9 Application and Implementation ........................ 22

9.1 Application Information............................................ 22

9.2 Typical Application ................................................. 22

10 Power Supply Recommendations ..................... 23

11 Layout................................................................... 24

11.1 Layout Guidelines ................................................. 24

11.2 Layout Example .................................................... 25

12 器器件件和和文文档档支支持持 ..................................................... 26

12.1 文档支持................................................................ 26

12.2 接收文档更新通知 ................................................. 26

12.3 社区资源................................................................ 26

12.4 商标 ....................................................................... 26

12.5 静电放电警告......................................................... 26

12.6 Glossary................................................................ 26

13 机机械械、、封封装装和和可可订订购购信信息息....................................... 26

4 修修订订历历史史记记录录

注:之前版本的页码可能与当前版本有所不同。

Changes from Revision A (August 2016) to Revision B Page

• 已更改 将文档状态从

预告信息

更改为

生产数据

...................................................................................................................... 1

1SEL 16 VDD

2S1A 15 EN

3S1B 14 S4A

4D1 13 S4B

5S2A 12 D4

6S2B 11 S3A

7D2 10 S3B

8GND 9 D3

Not to scale

1SEL 16 VDD

2S1A 15 EN

3S1B 14 S4A

4D1 13 S4B

5S2A 12 D4

6S2B 11 S3A

7D2 10 S3B

8GND 9 D3

Not to scale

3

SN3257-Q1

www.ti.com.cn

ZHCSK05B –JULY 2019–REVISED JANUARY 2020

Copyright © 2019–2020, Texas Instruments Incorporated

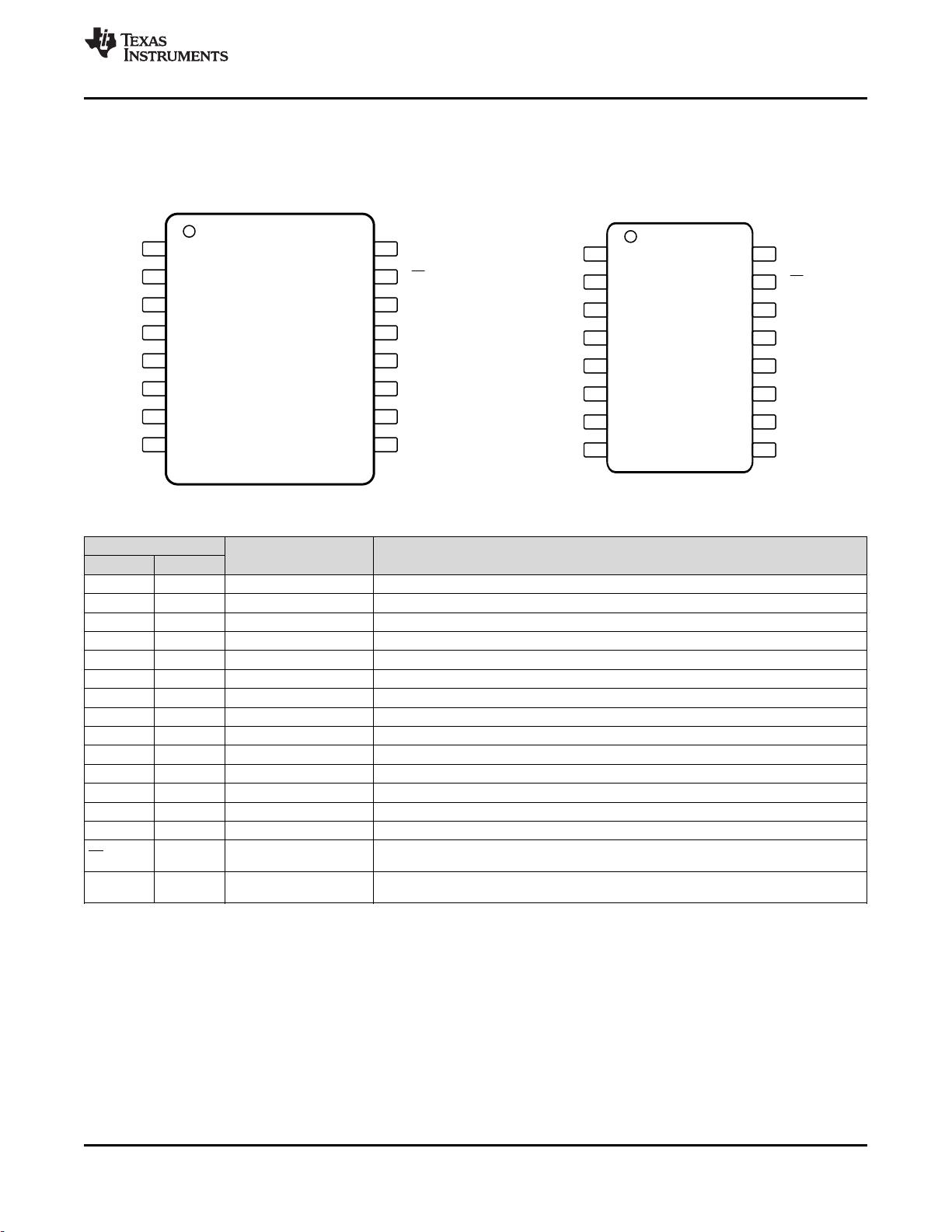

5 Pin Configuration and Functions

PW Package

16-Pin TSSOP

Top View

DYY Package

16-Pin SOT-23

Top View

(1) I = input, O = output, I/O = input and output, P = power

(2) Refer to Device Functional Modes for what to do with unused pins.

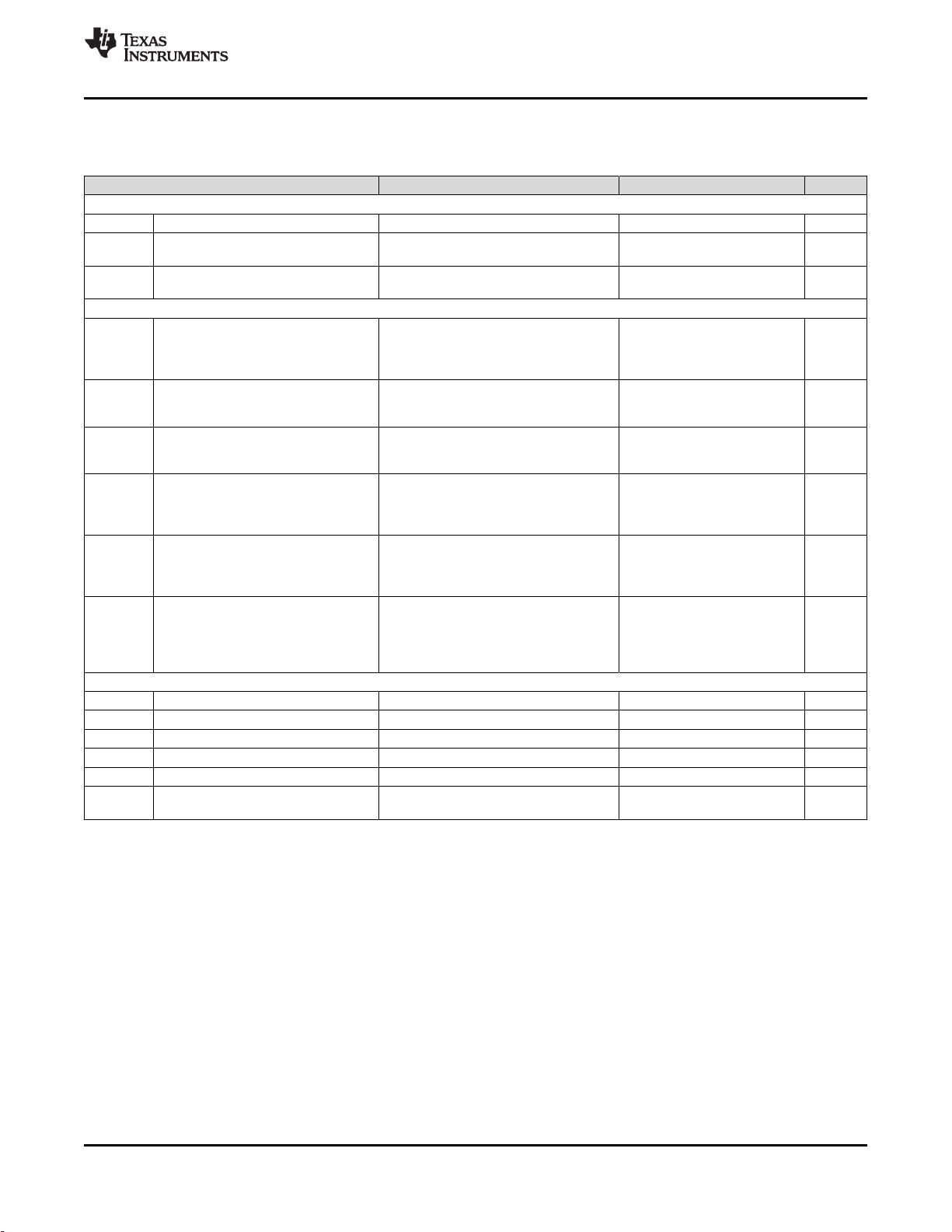

Pin Functions

PIN

TYPE

(1)

DESCRIPTION

(2)

NAME NO.

SEL 1 I Select pin: controls state of switches according to 表 1. Internal 6 MΩ pull-down to GND.

S1A 2 I/O Source pin 1A. Can be an input or output.

S1B 3 I/O Source pin 1B. Can be an input or output.

D1 4 I/O Drain pin 1. Can be an input or output.

S2A 5 I/O Source pin 2A. Can be an input or output.

S2B 6 I/O Source pin 2B. Can be an input or output.

D2 7 I/O Drain pin 2. Can be an input or output.

GND 8 P Ground (0 V) reference

D3 9 I/O Drain pin 3. Can be an input or output.

S3B 10 I/O Source pin 3B. Can be an input or output.

S3A 11 I/O Source pin 3A. Can be an input or output.

D4 12 I/O Drain pin 4. Can be an input or output.

S4B 13 I/O Source pin 4B. Can be an input or output.

S4A 14 I/O Source pin 4A. Can be an input or output.

EN 15 I

Active low enable: When this pin is high, all switches are turned off. When this pin is low, SEL pin

controls the signal path selection. Internal 6 MΩ pull-down to GND.

VDD 16 P

Positive power supply. This pin is the most positive power-supply potential. For reliable operation,

connect a decoupling capacitor ranging from 0.1 µF to 10 µF between V

DD

and GND.

4

SN3257-Q1

ZHCSK05B –JULY 2019–REVISED JANUARY 2020

www.ti.com.cn

Copyright © 2019–2020, Texas Instruments Incorporated

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

(3) All voltages are with respect to ground, unless otherwise specified.

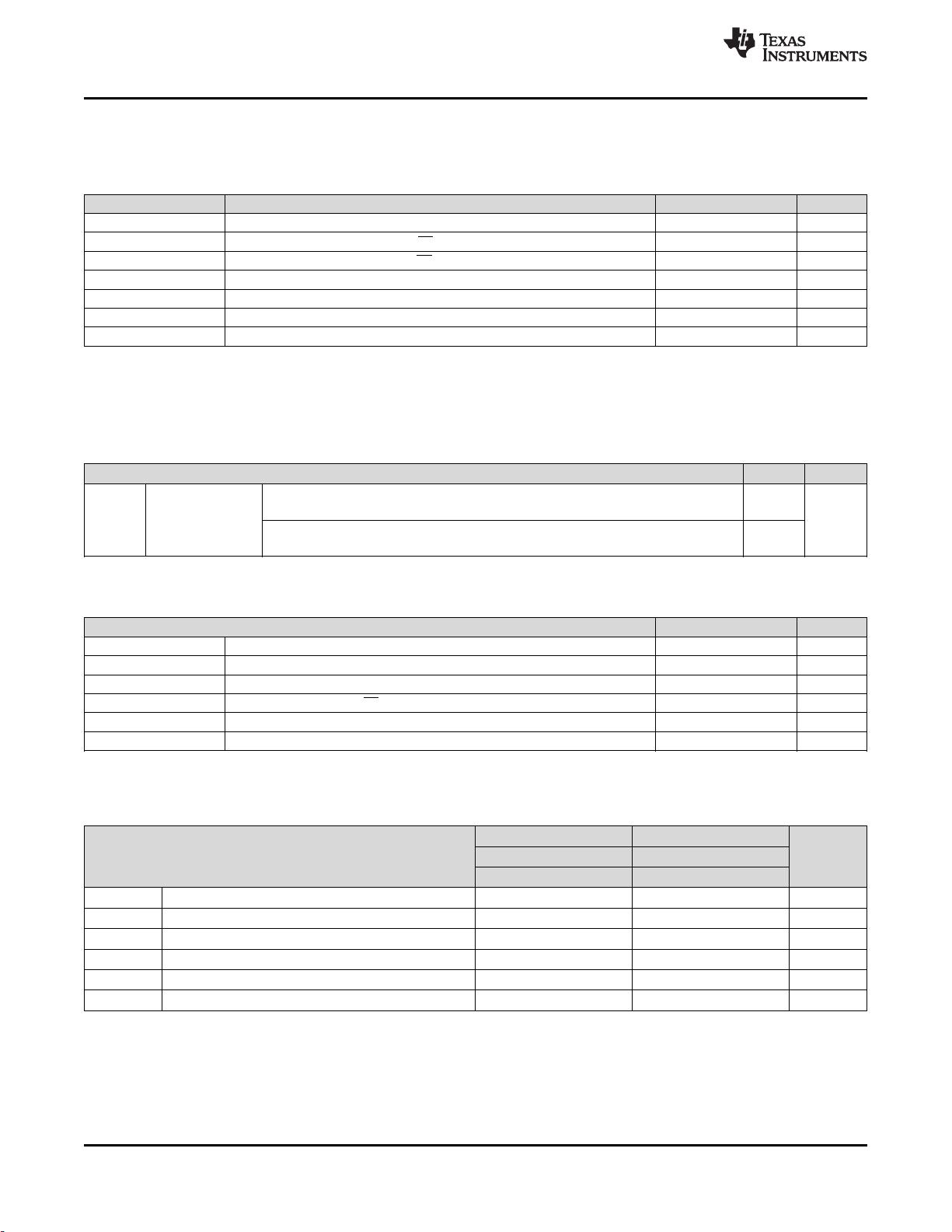

6 Specifications

6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)

(1)(2)(3)

MIN MAX UNIT

V

DD

Supply voltage –0.5 6 V

V

SEL

or V

EN

Logic control input pin voltage (SEL or EN) –0.5 6 V

I

SEL

or I

EN

Logic control input pin current (SEL or EN) –30 30 mA

V

S

or V

D

Source or drain pin voltage –0.5 6 V

I

S

or I

D (CONT)

Source and drain pin continuous current: (SxA, SxB, Dx) –25 25 mA

T

stg

Storage temperature –65 150 °C

T

J

Junction temperature 150 °C

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic

discharge

Human body model (HBM), per AEC Q100-002

(1)

HBM ESD Classification Level 2

±2000

V

Charged device model (CDM), per AEC Q100-011

CDM ESD Classification Level C4B

±750

(1) Device input/output can operate up to V

DD

x 2, with a maximum input/output voltage of 5.5 V.

(2) V

S_off

and V

D_off

refers to the voltage at the source or drain pins when supply is less than 1.5 V.

6.3 Recommended Operating Conditions

MIN MAX UNIT

V

DD

Supply voltage 1.5 5.5 V

V

S

or V

D

Signal path input or output voltage (source or drain pin), V

DD

≥ 1.5 V

(1)

0 V

DD

x 2 V

V

S_off

or V

D_off

Signal path input or output voltage (source or drain pin), V

DD

< 1.5 V

(2)

0 3.6 V

V

SEL

or V

EN

Logic control input voltage (EN, SEL) 0 5.5 V

I

S

or I

D (CONT)

Source and drain pin continuous current: (SxA, SxB, Dx) –25 25 mA

T

A

Ambient temperature –40 125 ºC

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

6.4 Thermal Information

THERMAL METRIC

(1)

DEVICE DEVICE

UNITPW (TSSOP) DYY (SOT-23)

16 PINS 16 PINS

R

θJA

Junction-to-ambient thermal resistance 117.4 123.0 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 47.9 70.5 °C/W

R

θJB

Junction-to-board thermal resistance 63.7 50.4 °C/W

Ψ

JT

Junction-to-top characterization parameter 6.9 5.0 °C/W

Ψ

JB

Junction-to-board characterization parameter 63.1 50.3 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance N/A N/A °C/W

5

SN3257-Q1

www.ti.com.cn

ZHCSK05B –JULY 2019–REVISED JANUARY 2020

Copyright © 2019–2020, Texas Instruments Incorporated

6.5 Electrical Characteristics

V

DD

= 1.5 V to 5.5 V, GND = 0V, T

A

= –40°C to +125°C

Typical values are at V

DD

= 3.3 V, T

A

= 25°C, (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

POWER SUPPLY

V

DD

Power supply voltage 1.5 5.5 V

I

DD

Active supply current

V

SEL

= 0 V, 1.4 V or V

DD

V

S

= 0 V to 5.5 V

40 68 μA

I

DD_STANDBY

Supply current when disabled

V

EN

= 1.4 V or V

DD

V

S

= 0 V to 5.5 V

7.5 15 µA

DC CHARACTERISTICS

R

ON

On-resistance

V

S

= 0 V to V

DD

×2

V

S(max)

= 5.5 V

I

SD

= 8 mA

Refer to ON-State Resistance Figure

2 5 Ω

ΔR

ON

On-resistance match between channels

V

S

= V

DD

I

SD

= 8 mA

Refer to ON-State Resistance Figure

0.07 0.8 Ω

R

ON (FLAT)

On-resistance flatness

V

S

= 0 V to V

DD

I

SD

= 8 mA

Refer to ON-State Resistance Figure

1 2.5 Ω

I

POFF

Powered-off I/O pin leakage current

V

DD

= 0 V

V

S

= 0 V to 3.6 V

V

D

= 0 V

Refer to Ipoff Leakage Figure

–8 0.01 8 µA

I

S(OFF)

I

D(OFF)

OFF leakage current

Switch Off

V

D

= 0.8×V

DD

/ 0.2×V

DD

V

S

= 0.2×V

DD

/ 0.8×V

DD

Refer to Off Leakage Figure

–900 0.03 900 nA

I

D(ON)

I

S(ON)

ON leakage current

Switch On

V

D

= 0.8×V

DD

/ 0.2×V

DD

, S pins floating

or

V

S

= 0.8×V

DD

/ 0.2×V

DD

, D pins floating

Refer to On Leakage Figure

–900 0.01 900 nA

LOGIC INPUTS

V

IH

Input logic high 1.2 5.5 V

V

IL

Input logic low 0 0.45 V

I

IH

Input high leakage current V

SEL

= 1.8 V, V

DD

1 ±2 μA

I

IL

Input low leakage current V

SEL

= 0 V 0.2 ±2 μA

R

PD

Internal pull-down resistor on logic pins 6 MΩ

C

I

Logic input capacitance

V

SEL

= 0 V, 1.8 V or V

DD

f = 1 MHz

3 pF

剩余36页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3100

- 资源: 5330

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功