Lecture-6-Import-Design-and-Floorplan.pdf

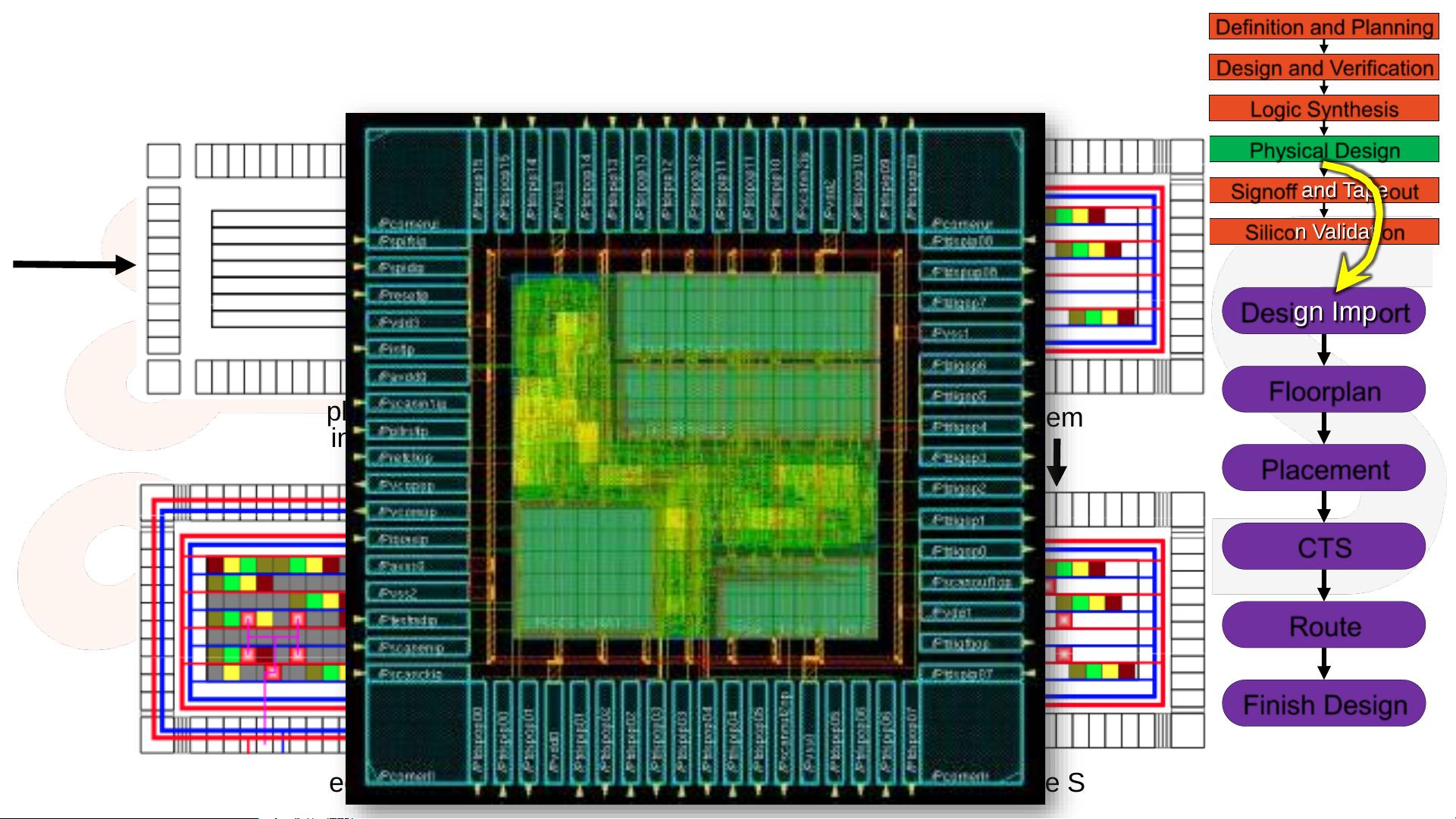

在数字集成电路设计中,"Lecture-6-Import-Design-and-Floorplan.pdf" 主要讲解了从逻辑设计转向物理设计的过程,这是芯片设计的重要环节,尤其适合初学者理解。这个讲座由Dr. Adam Teman主讲,内容涵盖了一系列从前端设计到后端实现的关键步骤。 前端设计阶段主要涉及定义、规划、设计验证和逻辑综合。在这个阶段,设计师会编写Verilog或VHDL等硬件描述语言(HDL)代码来描述电路的行为,然后通过约束定义(.sdc)设定设计目标和限制条件。多模式多电压多时钟(MMMC)定义了芯片在不同工作状态下的电源管理和时钟管理策略。 当前端设计完成后,我们进入后端设计,首先是设计导入(Design Import)。这个阶段是将前端的逻辑设计转换到物理设计工具中,为后续的物理实现做准备。设计导入通常涉及到将逻辑网表(.v)和设计约束(.sdc)导入到布局布线(Place & Route,P&R)工具中。 接下来是物理设计的基础——绘制 Floorplan。Floorplan 是一个高层次的布局规划,决定了芯片上关键模块如知识产权核(IP)、输入/输出(I/O)、电源网格(Power Grid)以及特殊路径的位置。这一步骤需要考虑到功能区的划分、面积优化、信号路由的便捷性以及热耗散等因素。 完成 Floorplan 后,进行门级放置(Placement)。这个阶段根据前面的规划和时序约束,将逻辑门级单元放置在芯片的不同区域,同时要考虑拥挤度(Congestion)和时序延迟。放置的目标是优化性能、面积和功耗。 放置完成后,紧接着是时钟树综合(Clock Tree Synthesis, CTS)。时钟树是确保整个系统同步的关键,它连接所有时钟信号,提供一致的时钟到达时间,以满足严格的时序要求。 最后是详细布线(Detailed Routing)。布线需要遵循设计规则检查(DRC)和确保满足电气性能,如信号完整性和电源完整性。此外,还需要考虑噪声、串扰和电磁干扰等问题,确保设计符合制造工艺的限制。 在签收(Signoff)和提交之前,还需要进行一系列的清理、验证和优化工作,确保设计无误,满足所有的规格要求。签收是设计过程的最后阶段,之后芯片将进入制造阶段,最终进行硅验证(Silicon Validation),确认实际芯片与设计规格的一致性。 从逻辑到物理的设计转换是一个复杂而系统的过程,包括设计导入、Floorplan、放置、时钟树综合和布线等多个步骤,每个步骤都对芯片的性能、面积和功耗有重大影响。对于初学者来说,理解并掌握这些流程是成为合格的集成电路设计师的基础。

剩余44页未读,继续阅读

- 粉丝: 1

- 资源: 9

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功