没有合适的资源?快使用搜索试试~ 我知道了~

计算机微结构-流水线的数据通路和逻辑控制

资源推荐

资源详情

资源评论

流水线数据通路和控制逻辑

流水线数据通路和控制逻辑流水线数据通路和控制逻辑

流水线数据通路和控制逻辑

Lecture 24: Instruction Pipeline

指令流水线

指令流水线指令流水线

指令流水线

流水线数据通路和控制

流水线数据通路和控制流水线数据通路和控制

流水线数据通路和控制

° 日常生活中的流水线处理例子

日常生活中的流水线处理例子日常生活中的流水线处理例子

日常生活中的流水线处理例子:

::

:洗衣服

洗衣服洗衣服

洗衣服

° 单周期处理器模型和流水线性能比较

单周期处理器模型和流水线性能比较单周期处理器模型和流水线性能比较

单周期处理器模型和流水线性能比较

° 什么样的指令集适合于流水线方式执行

什么样的指令集适合于流水线方式执行什么样的指令集适合于流水线方式执行

什么样的指令集适合于流水线方式执行

° 如何设计流水线数据通路

如何设计流水线数据通路如何设计流水线数据通路

如何设计流水线数据通路

• 以

以以

以MIPS

MIPSMIPS

MIPS指令子集来说明

指令子集来说明指令子集来说明

指令子集来说明

• 详细设计取指令部件

详细设计取指令部件详细设计取指令部件

详细设计取指令部件

• 详细设计执行部件

详细设计执行部件详细设计执行部件

详细设计执行部件

• 分析每条指令在流水线中的执行过程

分析每条指令在流水线中的执行过程分析每条指令在流水线中的执行过程

分析每条指令在流水线中的执行过程,

,,

,遇到各种问题

遇到各种问题遇到各种问题

遇到各种问题:

::

:

- 资源冲突

资源冲突资源冲突

资源冲突

- 寄存器和存储器的信号竞争

寄存器和存储器的信号竞争寄存器和存储器的信号竞争

寄存器和存储器的信号竞争

- 分支指令的延迟

分支指令的延迟分支指令的延迟

分支指令的延迟

- 指令间数据相关

指令间数据相关指令间数据相关

指令间数据相关

° 如何设计流水线控制逻辑

如何设计流水线控制逻辑如何设计流水线控制逻辑

如何设计流水线控制逻辑

• 分析每条指令执行过程中的控制信号

分析每条指令执行过程中的控制信号分析每条指令执行过程中的控制信号

分析每条指令执行过程中的控制信号

• 给出控制器设计过程

给出控制器设计过程给出控制器设计过程

给出控制器设计过程

° 流水线冒险的概念

流水线冒险的概念流水线冒险的概念

流水线冒险的概念

主

主主

主 要

要要

要 内

内内

内 容

容容

容

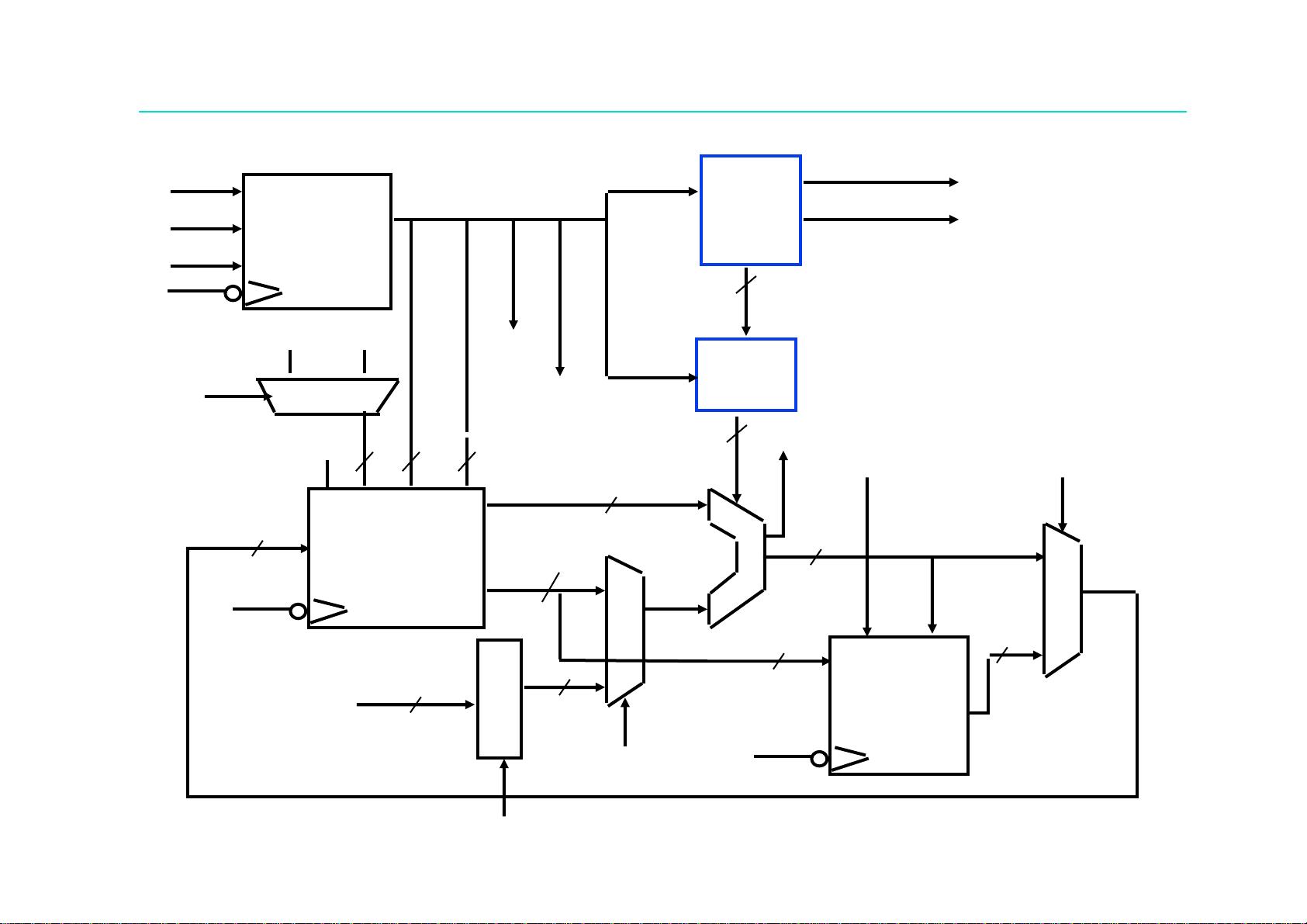

复习

复习复习

复习:

::

:

A Single Cycle Processor

32

ALUctr

Clk

busW

RegWr

32

32

busA

32

busB

55 5

Rw Ra Rb

32 32-bit

Registers

Rs

Rt

Rt

Rd

RegDst

Extender

Mux

Mux

32

16

imm16

ALUSrc

ExtOp

Mux

MemtoReg

Clk

Data In

WrEn

32

Adr

Data

Memory

32

MemWr

ALU

Zero

0

1

0

1

01

Instruction

Fetch Unit

Clk

Instruction<31:0>

Jump

Branch

<21:25>

<16:20>

<11:15>

<0:15>

Imm16

Rd

Main

Control

op

ALU

Control

func

ALUop

3

RegDst

ALUSrc

:

<5:0>

<31:26>

Instr<15:0>

Zero

3

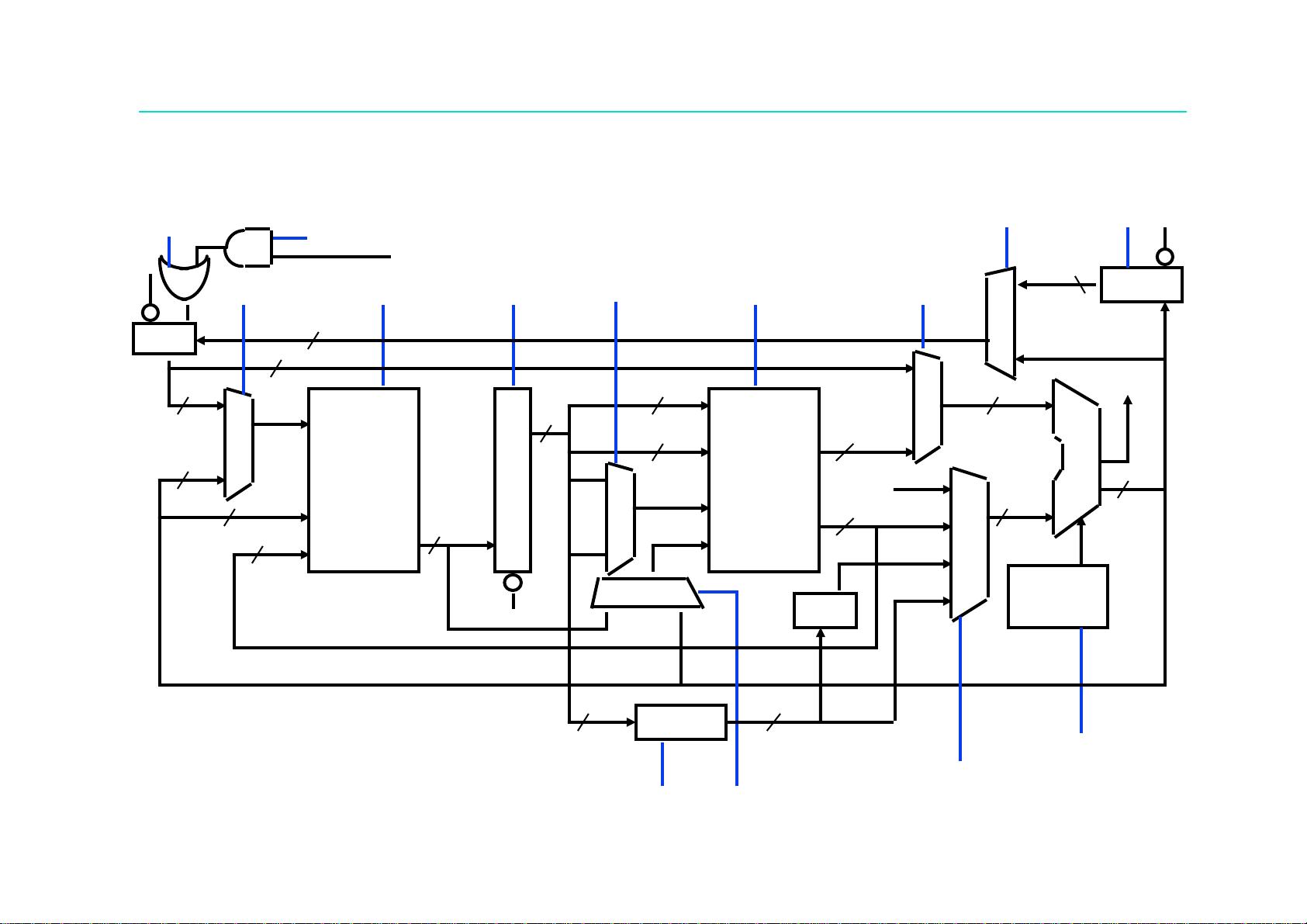

复习

复习复习

复习:

::

:

Multiple Cycle Processor

° MCP: 一个功能部件在一个指令周期中可以被使用多次

一个功能部件在一个指令周期中可以被使用多次一个功能部件在一个指令周期中可以被使用多次

一个功能部件在一个指令周期中可以被使用多次。

。。

。

Ideal

Memory

WrAdr

Din

RAdr

32

32

32

Dout

MemWr

32

ALU

32

32

ALUOp

ALU

Control

Instruction Reg

32

IRWr

32

Reg File

Ra

Rw

busW

Rb

5

5

32

busA

32

busB

RegWr

Rs

Rt

Mux

0

1

Rt

Rd

PCWr

ALUSelA

Mux

01

RegDst

Mux

0

1

32

PC

MemtoReg

Extend

ExtOp

Mux

0

1

32

0

1

2

3

4

16

Imm

32

<< 2

ALUSelB

Mux

1

0

Target

32

Zero

Zero

PCWrCond PCSrc BrWr

32

IorD

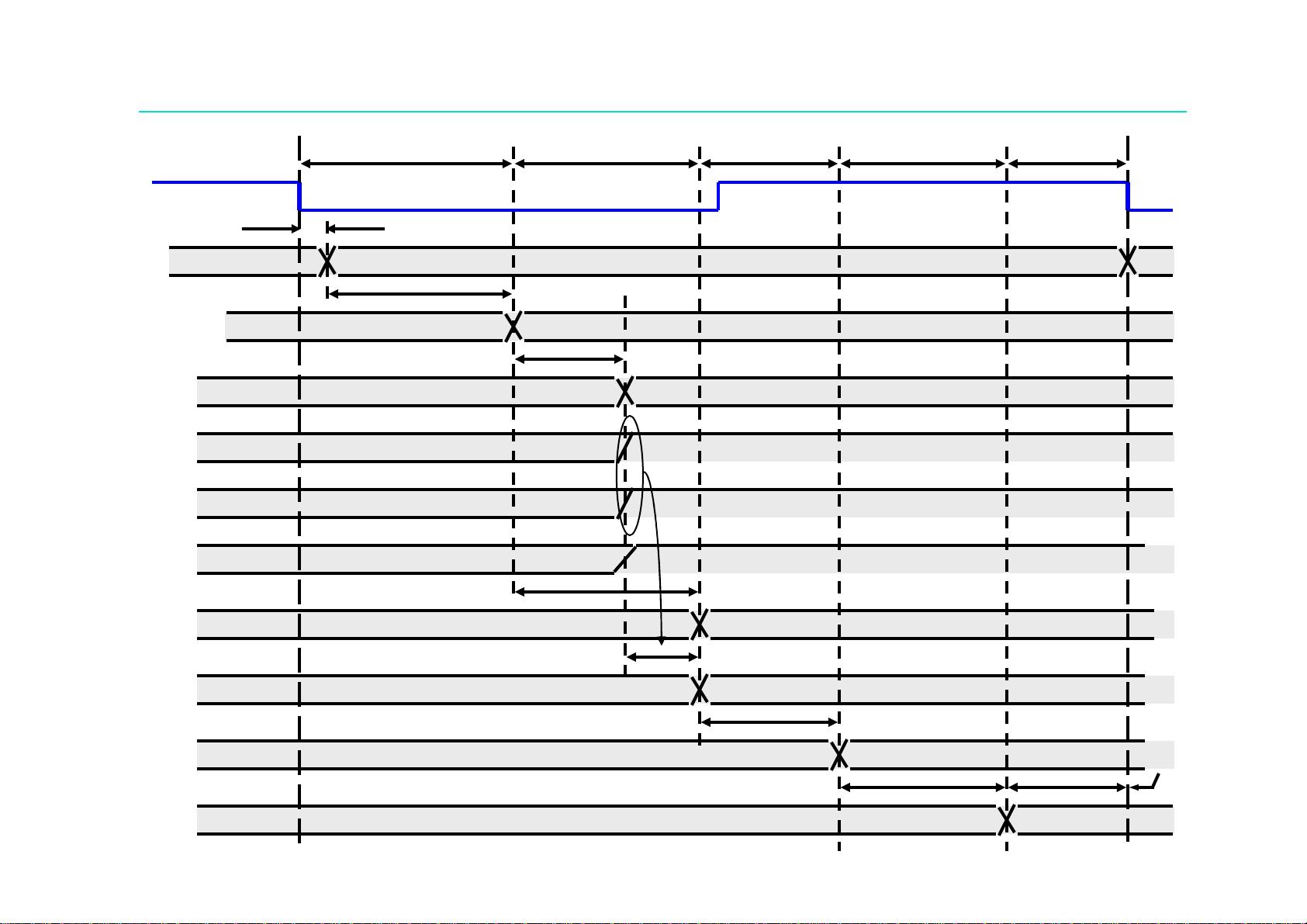

复习

复习复习

复习:

::

:

Timing Diagram of a Load Instruction

Clk

PC

Rs, Rt, Rd,

Op, Func

Clk-to-Q

ALUctr

Instruction Memory Access Time

Old Value New Value

RegWr Old Value New Value

Delay through Control Logic

busA

Register File Access Time

Old Value New Value

busB

ALU Delay

Old Value New Value

Old Value New Value

New ValueOld Value

ExtOp Old Value New Value

ALUSrc Old Value New Value

Address Old Value New Value

busW Old Value New

Delay through Extender & Mux

Data Memory Access Time

Instruction Fetch

Instr Decode /

Reg. Fetch

Address Reg Wr

Data Memory

Register File Write Time

1

3

2

剩余43页未读,继续阅读

资源评论

来杯清咖_

- 粉丝: 330

- 资源: 22

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功