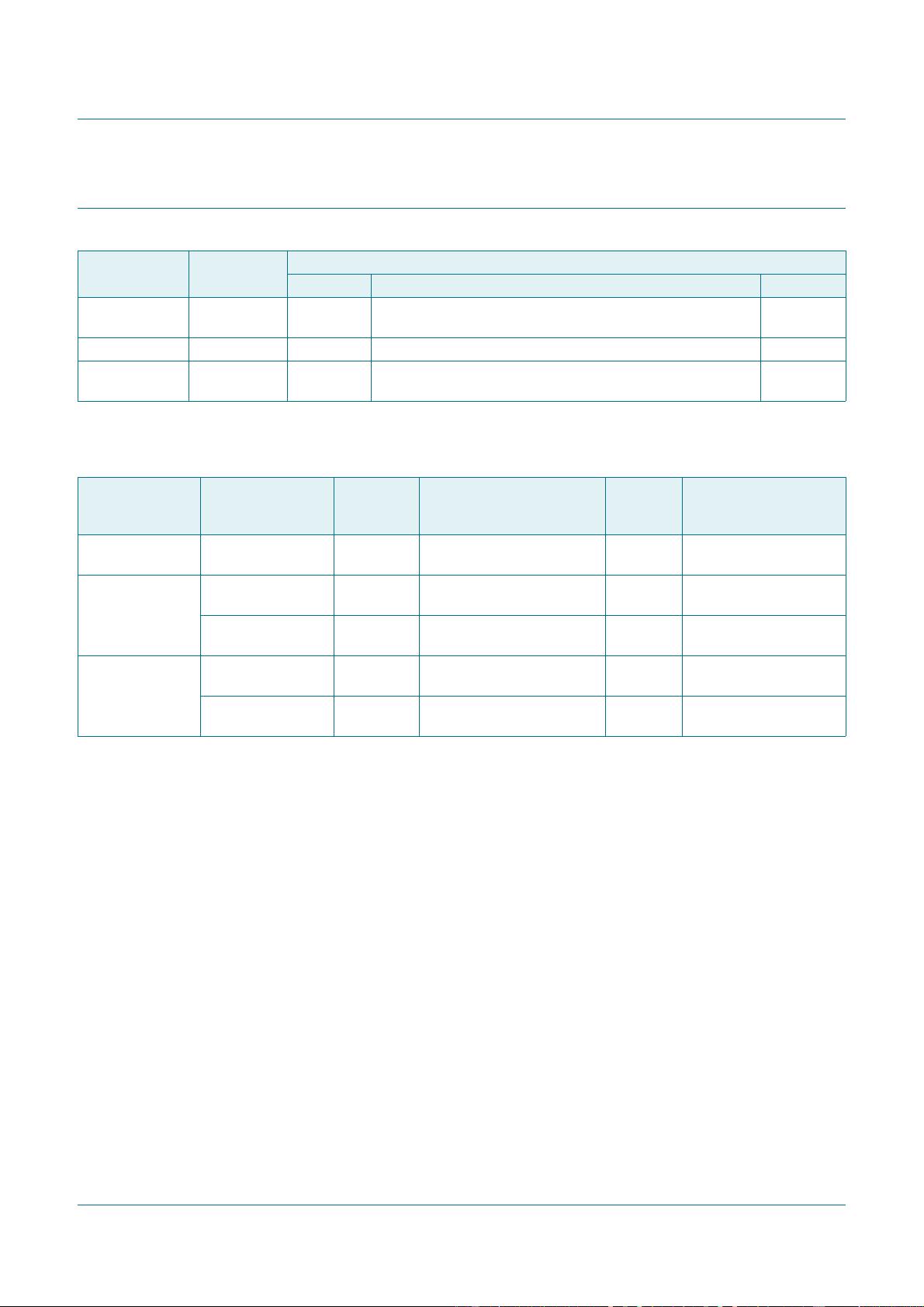

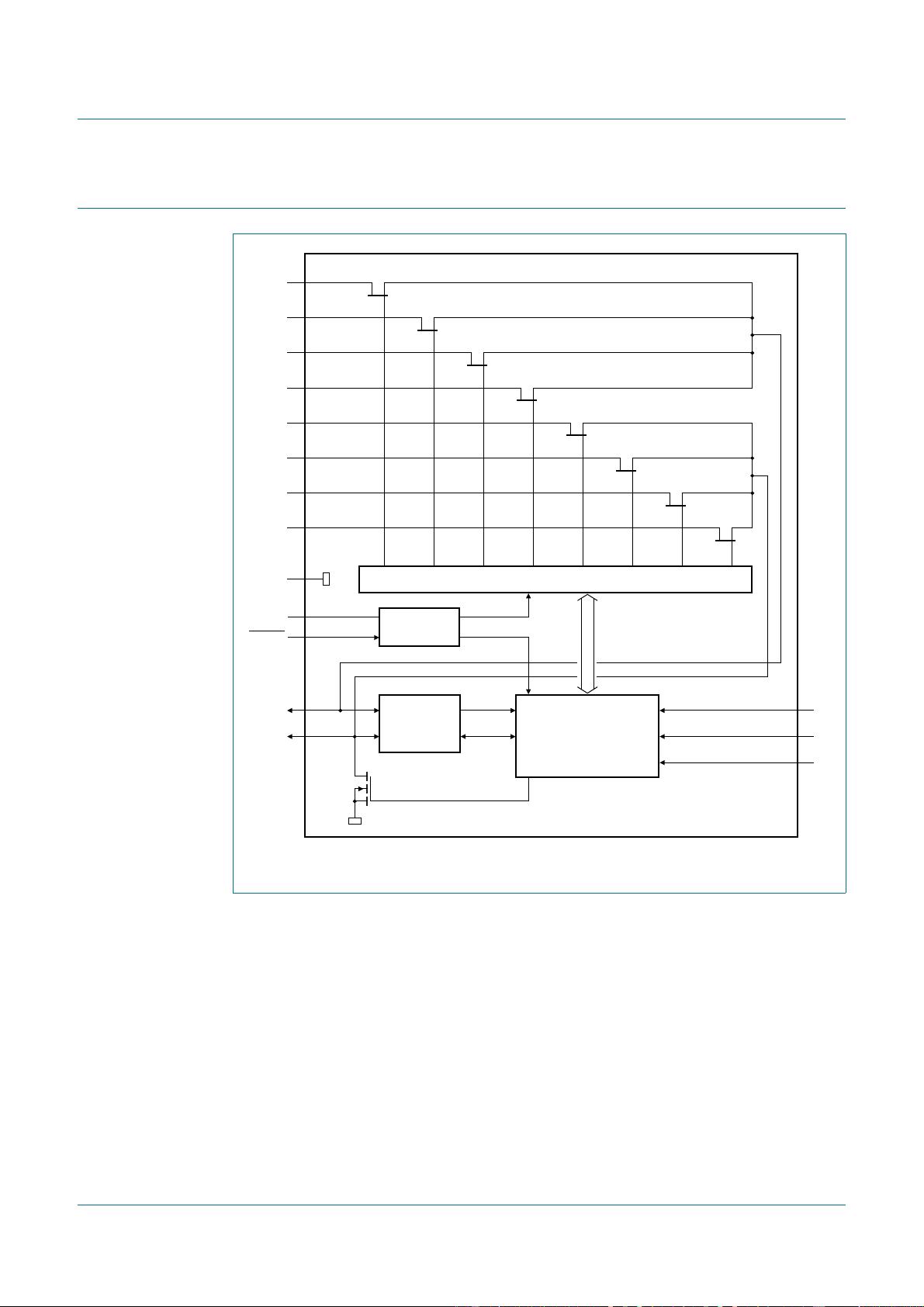

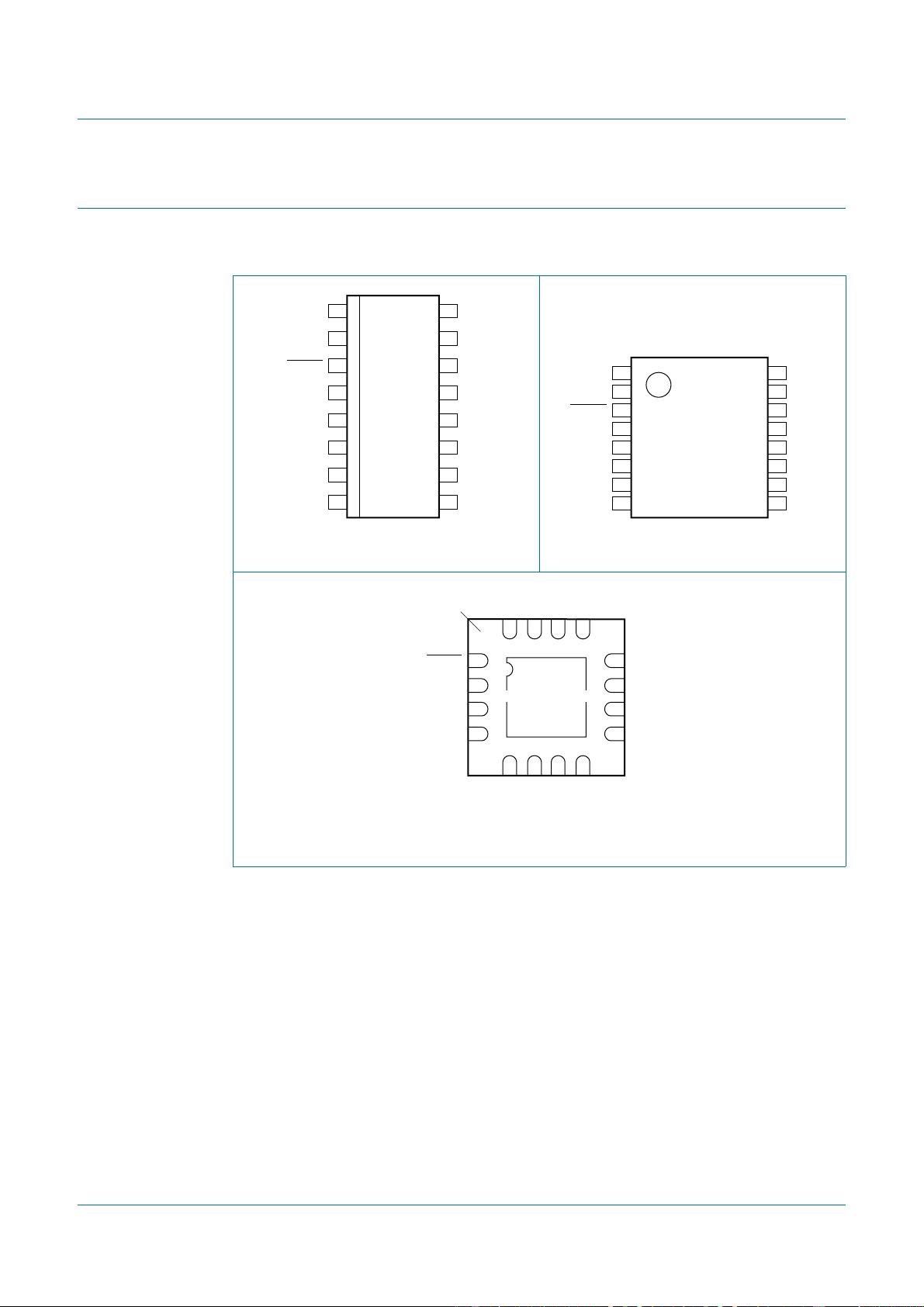

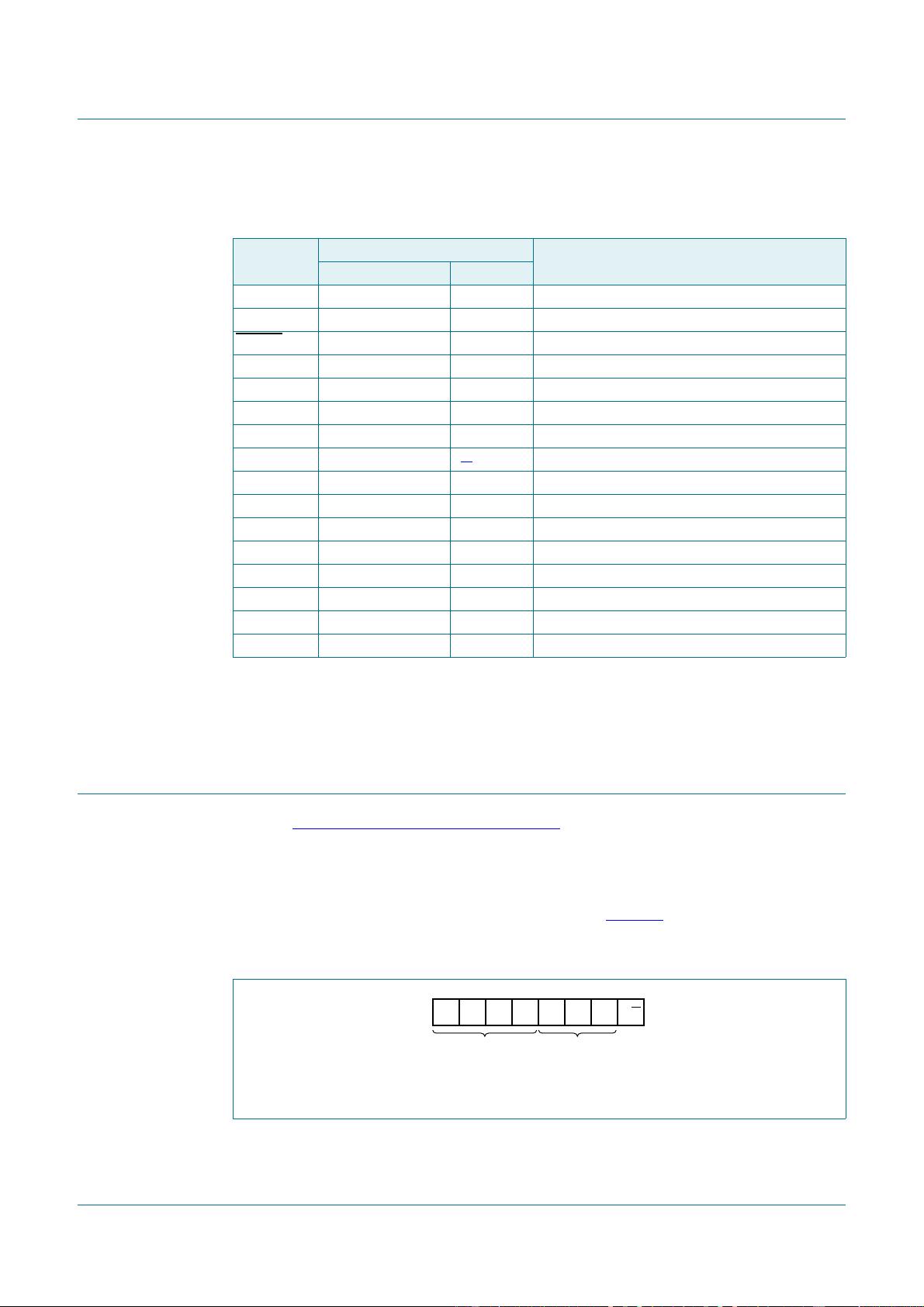

PCA9546A是一款由NXP半导体公司生产的四通道双向转换开关,专门设计用于I2C总线系统。这款芯片允许用户通过I2C总线控制四个独立的通道,每个通道都是一对SCx/SDx(SCL和SDA的下游对),可以单独或组合选择挂载到I2C总线上,极大地增强了系统中I2C设备的灵活性和可配置性。 1. 功能特性: - PCA9546A提供了1-of-4双向转换开关,能够根据需要开启或关闭各个通道。 - 它采用I2C总线接口逻辑,与SMBus标准兼容,使得与各种设备的通信变得更加简单。 - 该芯片具有一个活动低电平的复位输入,当其中一个下游I2C总线出现故障时,可以通过拉低RESET引脚进行恢复。 - 有3个地址引脚,最多允许在I2C总线上连接8个PCA9546A设备,扩展了系统的可扩展性。 - 通过I2C总线选择通道,可以任意组合,提供极大的灵活性。 - 在电源上电时,默认所有通道关闭,确保了安全的启动状态。 - PCA9546A采用低导通电阻开关,减少信号损失和功率消耗。 - 支持不同电压级别的总线(如1.8V、2.5V、3.3V和5V)之间的电压等级转换,允许不同电压的设备相互通信,无需额外的保护电路。 - 设计有无瞬变现象的电源启动,以及支持热插拔功能,使得在运行中添加或移除设备更加稳定。 - 待机电流低,有利于降低系统功耗。 - 工作电源电压范围为2.3V至5.5V,确保了宽泛的适用范围。 - 所有输入引脚均为5V容限,增强了抗干扰能力。 - 支持0Hz至400kHz的时钟频率,满足I2C总线的标准速度需求。 - 高度的静电放电(ESD)保护,超过2000V人体模型(HBM)和1000V接触放电模式(CDM)的JESD22标准。 - 按照JEDEC标准JESD78进行了Latch-up测试,确保了超过100mA的安全操作能力。 - 提供SO16、TSSOP16和HVQFN16三种封装形式,以适应不同的应用场合。 这款芯片的使用,不仅简化了系统设计,降低了硬件复杂性,还提升了系统的可靠性和兼容性。通过PCA9546A,用户可以轻松地管理多个I2C设备,并且能够在不同的电压环境中实现无缝通信。无论是嵌入式系统设计还是物联网设备开发,PCA9546A都是一个强大的I2C总线管理工具。

剩余29页未读,继续阅读

- 粉丝: 378

- 资源: 22

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 其实这就是历年摘出来的

- 前端分析-2023071100789

- 前端分析-2023071100789

- 基于卷积神经网络的AV1视频编码环路滤波技术

- 用vb语言编写一个抄底的源代码程序实例_抄底源码-CSDN博客.html

- 2023-04-06-项目笔记 - 第三百五十九阶段 - 4.4.2.357全局变量的作用域-357 -2025.12.26

- 地理遥感图像区域合并分割的大规模高效算法研究

- 2023-04-06-项目笔记 - 第三百五十九阶段 - 4.4.2.357全局变量的作用域-357 -2025.12.26

- EsptouchForAndroid-master.zip

- Javaweb大学专升本系统

- Neck Deep - In Bloom [mqms2].mgg2.flac

- Pyside6(3): 自动生成UI的Qt参数输入对话框demo

- ArcGIS教程(009)所需练习数据

- Hudi安装配置(容器环境)大数据技能竞赛平台搭建父模块pom.xml

- Dialogue System for Unity v2.2.50.1 (22 Nov 2024).unitypackage 对话系统

信息提交成功

信息提交成功

评论0