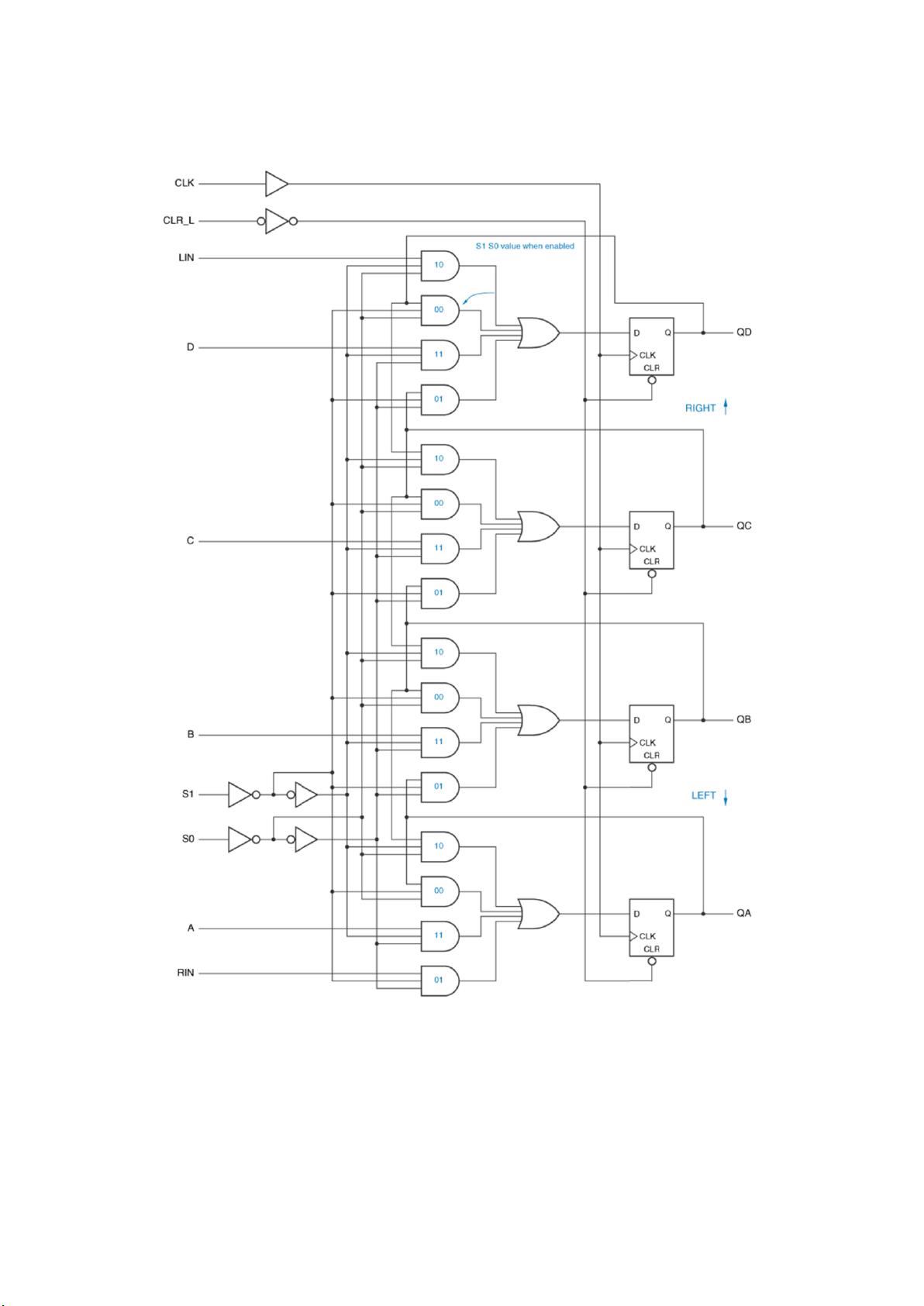

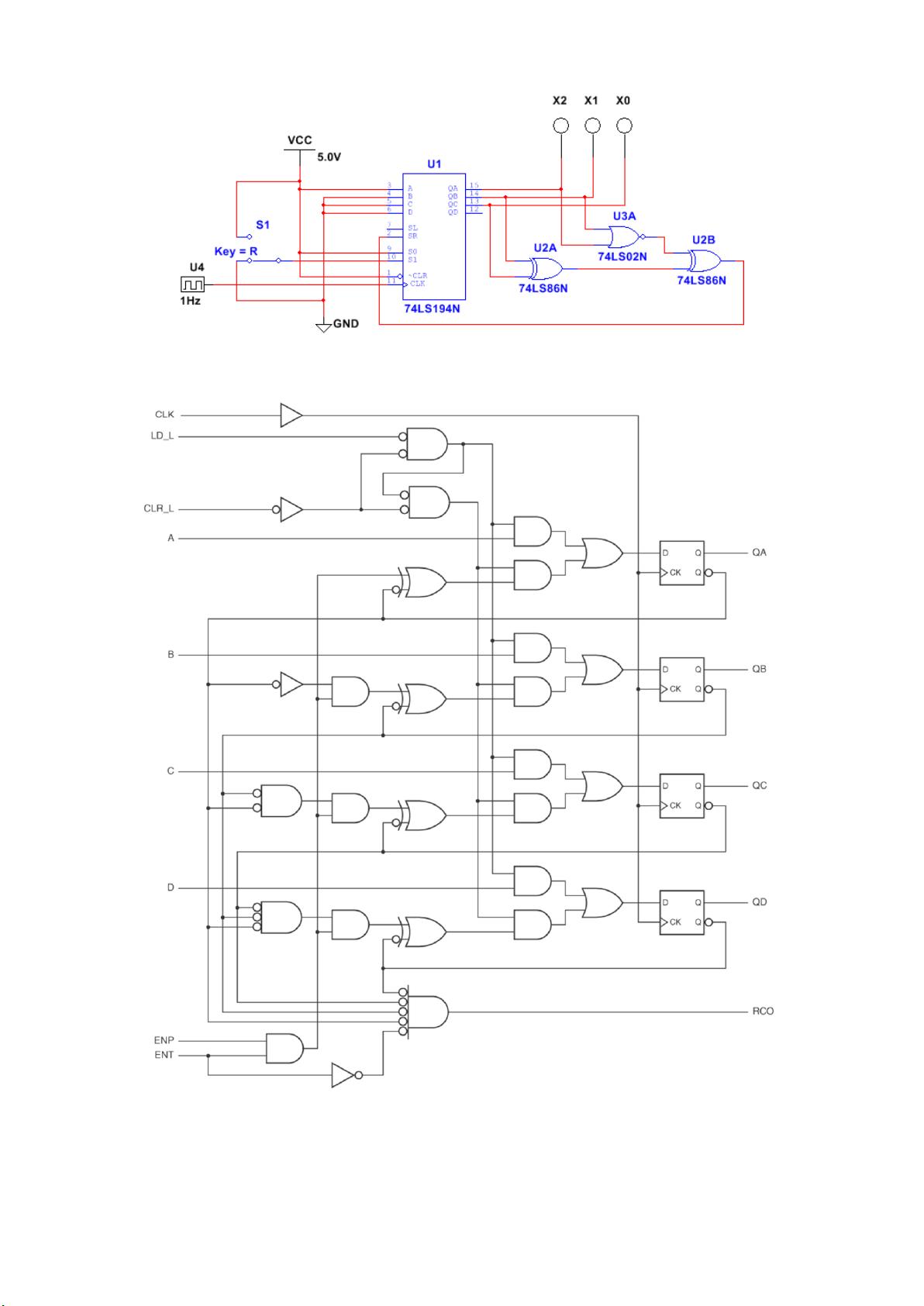

1.根据边沿D触发器74x74的原理图编写设计和仿真模块。 2.根据通用移位寄存器74x194的原理图编写设计和仿真模块。 3.采用1片74x194和其它小规模逻辑门设计3位LFSR计数器,编写设计和仿真模块。 4.根据4位同步计数器74x163的原理图编写设计和仿真模块。 5.输入为100MHz的系统时钟,采用7片74x163和其它小规模逻辑门设计1Hz的数字信号。 6.在FPGA开发板上调试3位LFSR计数器。 电子科技大学的这个数字逻辑综合实验主要关注Verilog语言在时序逻辑设计中的应用,涉及到的器件包括74x74边沿D触发器、74x194通用移位寄存器、74x163同步计数器,以及线性反馈移位寄存器(LFSR)。实验旨在让学生掌握这些基本逻辑器件的工作原理,通过Verilog进行硬件描述语言的设计和仿真,最终在FPGA开发板上实现和调试。 1. **边沿D触发器74x74**:这种触发器在时钟边沿(通常为上升沿)捕获数据D,并在下一个时钟周期保持该数据。在Verilog中,可以通过`always`块中的`posedge`关键字来描述上升沿触发,然后根据清零(CLR_L)和预置(PR_L)信号设置Q输出。 2. **通用移位寄存器74x194**:它可以实现数据的左移、右移、并行加载等功能。在Verilog中,设计时需要考虑时钟(CLK)、清零(CLR_L)、预置(SR_L)、数据输入(D)、移位控制(SH_L/SH_R)等信号。74x194的特性在于其内部包含多个D触发器,使得数据可以在时钟脉冲下按照特定方向移动。 3. **3位LFSR计数器**:LFSR是一种特殊的移位寄存器,通过线性反馈回路来产生特定序列。设计时需要根据74x194和其他逻辑门(如AND、OR、NOT门)构建反馈路径,以实现最大序列长度。LFSR常用于伪随机数生成和加密算法。 4. **同步计数器74x163**:4位同步计数器可以顺序计数,通常用于频率分频。设计时,根据74x163的特性(如计数输入、复位、预置、进位输出等),利用Verilog描述计数逻辑。例如,设计一个1Hz的信号发生器,输入100MHz的时钟,需要7个74x163级联并配合清零条件来达到1/100M的分频比。 5. **FPGA下载与调试**:设计完成后,使用Xilinx ISE开发工具进行编译、综合和实现,生成适配于Anvyl或Nexys3开发板的配置文件。通过Digilent Adept下载工具将设计代码下载到FPGA,然后在硬件平台上验证设计的功能正确性。 实验的步骤涵盖了Verilog代码编写、仿真验证、硬件实现的全过程,对于理解和应用数字逻辑设计原理,以及熟悉FPGA开发流程具有重要作用。通过这个实验,学生能够深入理解时序逻辑设计的核心概念,并具备将理论知识转化为实际硬件设计的能力。

剩余14页未读,继续阅读

- 粉丝: 66

- 资源: 13

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Qt的高仿酷狗音乐客户端 使用CMake进行模块化管理,参照酷狗酷狗客户端,高仿并且优化界面,QMediaPlayer和QAudioOutput来实现音频播放,提供更好的音乐播放体验

- 怒江市五险一金办事指南.docx

- 红河市五险一金办事指南.docx

- 杭州市五险一金办事指南.docx

- 嘉兴市五险一金办事指南.docx

- 数据分析-25-电商用户行为可视化分析

- 深度学习大作业基于Pytorch实现的人脸图像处理以及人脸识别项目源代码

- STM32 16字节加解密的AES算法程序源码

- 梧州市五险一金办事指南.docx

- 柳州市五险一金办事指南.docx

- 呼伦贝尔市五险一金办事指南.docx

- 锡林郭勒市五险一金办事指南.docx

- 吴忠市五险一金办事指南.docx

- 拉萨市五险一金办事指南.docx

- 那曲市五险一金办事指南.docx

- 数据分析-26-120年奥运会数据分析(包含代码数据)

信息提交成功

信息提交成功

- 1

- 2

前往页