没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

© 2011 Microchip Technology Inc. DS70330B_CN 第 19-1 页

I

2

C™

19

第 19 章 I

2

C™

目录

本章包括下列主题:

19.1 简介.............................................................................................................................. 19-2

19.2 I

2

C 总线特性 ................................................................................................................ 19-4

19.3 控制和状态寄存器 ........................................................................................................ 19-7

19.4 使能 I

2

C 操作.............................................................................................................. 19-13

19.5 在单主机环境中作为主器件进行通信 ......................................................................... 19-15

19.6 在多主机环境中作为主器件进行通信 ......................................................................... 19-28

19.7 作为从器件进行通信................................................................................................... 19-31

19.8 I

2

C 总线的连接注意事项 ............................................................................................ 19-46

19.9 PWRSAV 指令期间的模块操作 .................................................................................. 19-47

19.10 外设模块禁止 (PMD)寄存器 .................................................................................. 19-47

19.11 复位的影响 ................................................................................................................. 19-47

19.12 寄存器映射 ................................................................................................................. 19-48

19.13 设计技巧..................................................................................................................... 19-49

19.14 相关应用笔记 ............................................................................................................. 19-50

19.15 版本历史..................................................................................................................... 19-51

dsPIC33E/PIC24E 系列参考手册

DS70330B_CN 第 19-2 页 © 2011 Microchip Technology Inc.

19.1 简介

I

2

C™ 模块是用于同其他外设或单片机器件进行通信的串行接口。这些外设可以是串行 EEPROM、

显示驱动器和 A/D 转换器等。

I

2

C 模块可在以下任意 I

2

C 系统中工作:

• 作为从器件

• 在单主机系统中作为主器件 (从器件也可同时工作)

• 在多主机系统中作为主/从器件 (提供总线冲突检测和仲裁)

I

2

C 模块包含相互独立的 I

2

C 主器件逻辑和 I

2

C 从器件逻辑,它们根据各自的事件产生中断。在

多主机系统中,软件被简单地分为主器件控制程序和从器件控制程序。

当 I

2

C 主器件逻辑工作时,从器件逻辑也保持在工作状态,检测总线的状态,并可从其自身 (单

主机系统中)或从其他主器件 (多主机系统中)接收报文。在多主机总线仲裁期间,不会丢失任

何报文。

在多主机系统中,当检测到与系统中的其他主器件存在总线冲突时,模块提供了一种方法来终止

报文,然后重新发送报文。

I

2

C 模块中包含一个波特率发生器(Baud Rate Generator,BRG)。 I

2

C 波特率发生器并不耗用

器件中的其他定时器资源。

I

2

C 模块的主要特性有:

• 主器件和从器件逻辑相互独立

• 支持多主机系统,可以防止在仲裁时丢失报文

• 在从模式下可检测 7 位和 10 位器件地址,并可配置地址掩码

• 检测 I

2

C 协议中定义的广播呼叫地址

• 具有总线转发器模式,允许模块作为从器件接收所有报文,与地址无关

• 具有自动 SCLx 时钟延长功能,为处理器提供延时以响应从器件的数据请求

• 支持 100 kHz 和 400 kHz 总线规范

• 支持智能平台管理接口 (Intelligent Platform Management Interface, IPMI)标准

图 19-1 给出了 I

2

C 模块的框图。

注: 本系列参考手册章节旨在用作对器件数据手册的补充。根据不同的器件型号,本手

册章节可能并不适用于所有 dsPIC33E/PIC24E 器件。

请参见当前器件数据手册中 “I

2

C™”章节开头部分的注,以检查本文档是否支持

您所使用的器件。

器件数据手册和系列参考手册章节可从 Microchip 网站下载:

http://www.microchip.com

© 2011 Microchip Technology Inc. DS70330B_CN 第 19-3 页

第 19 章 I

2

C™

I

2

C™

19

图 19-1: I

2

C™ 框图

I2CxRCV

内部

数据总线

SCLx

SDAx

移位

匹配检测

I2CxADD

启动位和停止位

检测

时钟

地址匹配

时钟延长

I2CxTRN

LSB

移位时钟

BRG

重载控制

TCY/2

启动位和停止位

产生

应答产生

冲突检测

I2CxCON

I2CxSTAT

控制逻辑

读

LSB

写

读

I2CxBRG

I2CxRSR

写

读

写

读

写

读

写

读

写

读

I2CxMSK

递减计数器

dsPIC33E/PIC24E 系列参考手册

DS70330B_CN 第 19-4 页 © 2011 Microchip Technology Inc.

19.2 I

2

C 总线特性

I

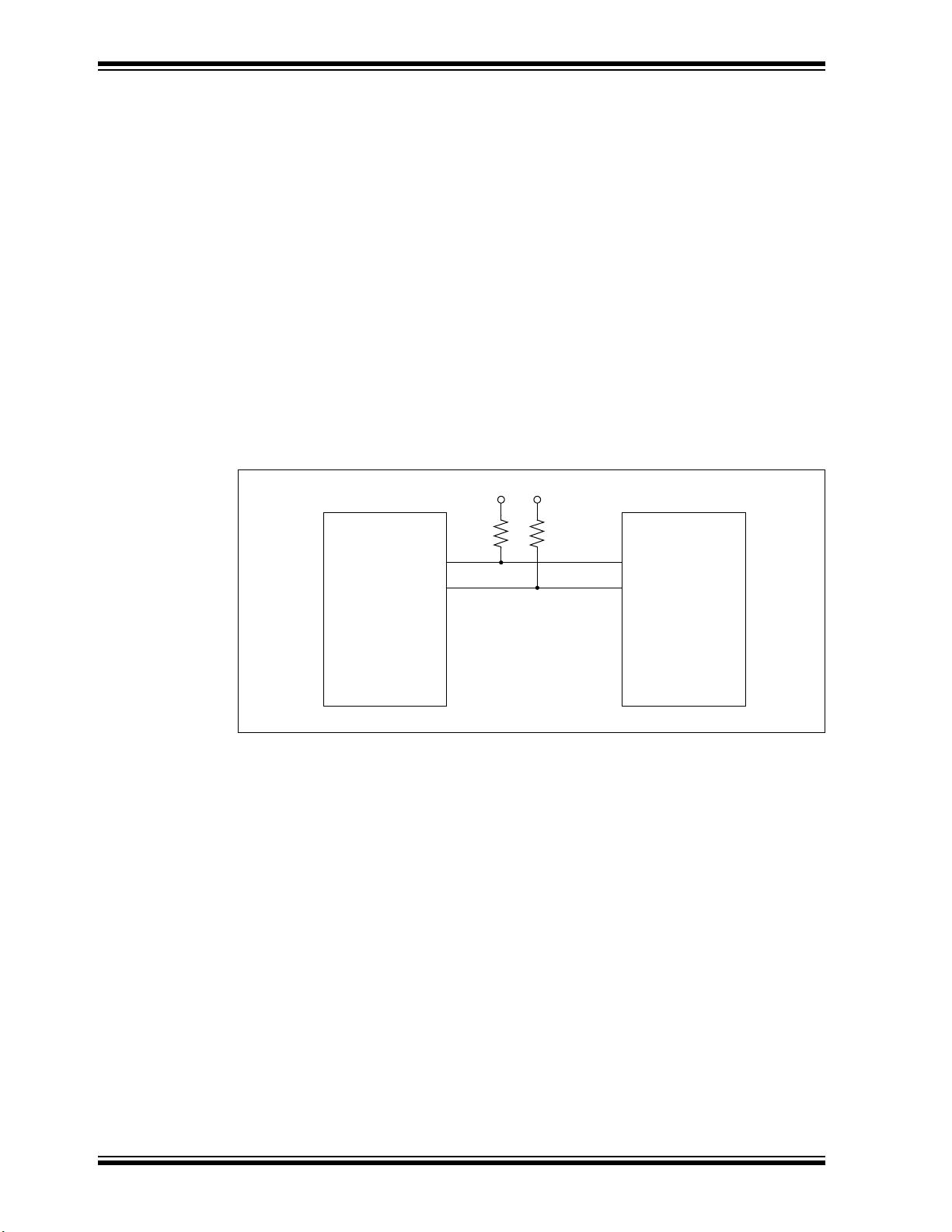

2

C总线是二线制串行接口。图19-2给出了dsPIC33E/PIC24E器件和24LC256 I

2

C串行EEPROM

之间的连接示意图,这是任何 I

2

C 接口的典型示例。

接口使用一个综合协议,以确保数据的可靠发送和接收。进行通信时,一个器件作为主器件启动

总线上的数据传输,并产生时钟信号以允许传输,而另一个 (几个)器件作为从器件对数据传输

作出响应。时钟线 SCLx 为主器件的输出和从器件的输入,不过从器件偶尔也可驱动 SCLx 线。

数据线 SDAx 可以是主器件和从器件的输出和输入。

因为 SDAx 和 SCLx 线是双向的,所以驱动 SDAx 和 SCLx 线的器件的输出级必须为漏极开路输

出,以便执行总线的线 “与”功能。使用外接上拉电阻以确保在没有器件将数据线拉低时线路能

保持高电平。

在 I

2

C 接口协议中,每个器件都有一个地址。当某个主器件要启动数据传输时,它首先发送它要

与之进行通信的器件地址。所有的器件均会监听,看是否是自己的地址。在该地址中,bit 0 指定

主器件是要自从器件读数据还是向从器件写数据。在数据传输期间,主器件和从器件始终处于相

反的工作模式 (发送器/接收器)。即,可以将它们看作是工作于以下两种关系之一:

• 主器件——发送器,从器件——接收器

• 从器件——发送器,主器件——接收器

在两种情况中,均由主器件产生 SCLx 时钟信号。

图 19-2:典型I

2

C™ 互连框图

19.2.1 I

2

C 总线协议

I

2

C 总线协议定义如下:

只有在总线不忙时才能启动数据传输。

在数据传输期间,只要 SCLx 时钟线为高电平,数据线就必须保持稳定。在 SCLx 时钟线为高电

平时,数据线的电平变化将被解析为启动或停止条件。

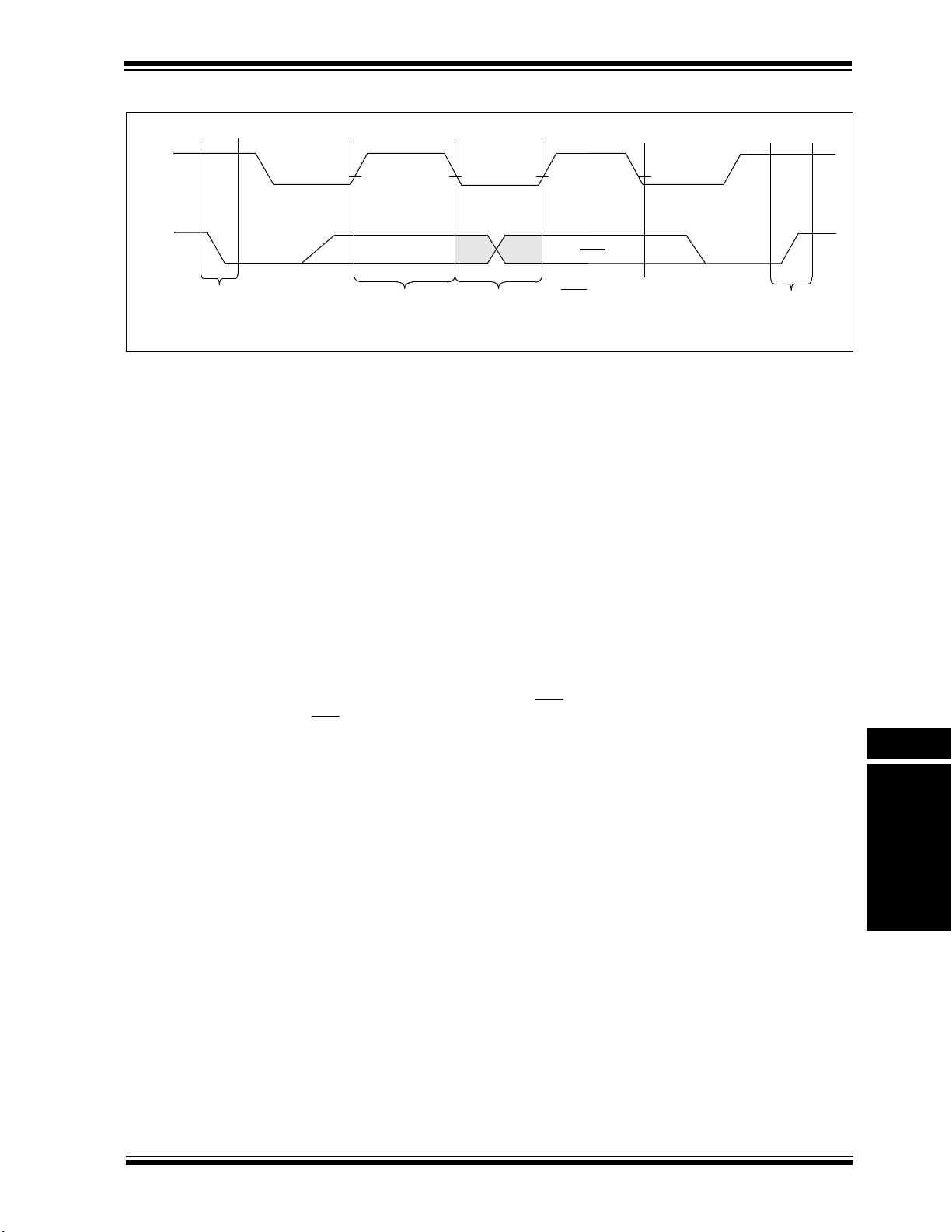

相应地,定义了如图 19-3 所示的总线条件。

SCLX

SDAX

dsPIC33E/PIC24E

SDA

SCL

VDD VDD

4.7 kΩ

24LC256

(典型值)

© 2011 Microchip Technology Inc. DS70330B_CN 第 19-5 页

第 19 章 I

2

C™

I

2

C™

19

图 19-3: I

2

C™ 总线协议状态

19.2.1.1 启动数据传输 (S)

在总线空闲状态之后,当时钟(SCLx)为高电平时,SDAx 线从高电平跳变到低电平产生启动条

件。所有数据传输都必须以启动条件开始。

19.2.1.2 停止数据传输 (P)

当时钟(SCLx)为高电平时,SDAx 线从低电平跳变到高电平产生停止条件。所有数据传输都必

须以停止条件结束。

19.2.1.3 重复启动 (R)

在等待状态之后,当时钟(SCLx)为高电平时,SDAx 线从高电平跳变到低电平产生重复启动条

件。重复启动条件使主器件可在不放弃总线控制的情况下更改总线方向或所寻址的从器件。

19.2.1.4 数据有效 (D)

在启动条件之后,如果 SDAx 线在时钟信号的高电平期间保持稳定,则 SDAx 线的状态代表有效

数据。每个 SCLx 时钟传送一位数据。

19.2.1.5 应答 (A)或不应答 (N)

所有的数据字节传输都必须由接收器应答 (ACK)或不应答 (NACK)。接收器将 SDAx 线拉低

则发出

ACK,释放 SDAx 线则发出 NACK。应答为一位周期,使用一个 SCLx 时钟。

19.2.1.6 等待/数据无效 (Q)

数据线上的数据必须在时钟信号的低电平期间改变。器件也可以通过在 SCLx 上驱动低电平来延

长时钟的低电平时间,使得总线处于等待状态。

19.2.1.7 总线空闲 (I)

在停止条件之后、启动条件之前的时间内,数据线和时钟线都保持高电平。

19.2.2 报文协议

图 19-4 所示为典型的 I

2

C 报文。在该示例中,报文将从 24LC256 I

2

C 串行 EEPROM 读取指定

字节。 dsPIC33E/PIC24E 器件将作为主器件,而 24LC256 器件作为从器件。

图 19-4 给出了由主器件驱动的数据和由从器件驱动的数据,要考虑到组合 SDAx 线上的数据是

将主器件数据和从器件数据线 “与”后的数据。主器件控制协议并产生协议序列。从器件仅在特

定的时间驱动总线。

有效

允许数据

改变

停止条件启动条件

SCLx

SDAx

(I)(S)(D)(A)或( N)(P)(I)

数据或地址

(Q)

ACK

/NACK

有效

NACK

ACK

剩余53页未读,继续阅读

资源评论

翻滚的雪球

- 粉丝: 103

- 资源: 44

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功