没有合适的资源?快使用搜索试试~ 我知道了~

详细介绍内存芯片的基本概念,工作原理,时序和时延以及芯片性能提升的方法。对SDR SDRAM和DDR SDRAM做了透彻的比较,并带入了内存模组的相关介绍。

资源推荐

资源详情

资源评论

SDRAM 内存模组的物理 Bank 与芯片位宽

我们平时看到的 SDRAM 都是以模组形式出现,为什么要做成这种形式呢?解释这一点首先要接触到两个概念:

物理 Bank 与芯片位宽。

1、 物理 Bank

内存系统为了保证与 CPU 的正常通信,必须一次传输完 CPU 在一个传输周期内所需要的数据。而 CPU 在一个

传输周期能接收的数据容量就是 CPU 数据总线的位宽,单位是 bit(位)。控制内存与 CPU 之间数据交换的北

桥芯片也因此将内存总线的数据位宽等同于 CPU 数据总线的位宽,而这个位宽就称之为内存物理 Bank

(Physical Bank,下文简称 P-Bank)的位宽。所以内存必须要组织成 P-Bank 来与 CPU 打交道。

2、 芯片位宽

上文已经讲到 SDRAM 内存系统必须要组成一个 P-Bank 的位宽,才能与 CPU 正常通信,那么这个 P-Bank

位宽怎么得到呢?这就涉及到内存芯片的结构。

每个内存芯片也有自己的位宽,即每个传输周期能提供的数据量。理论上,完全可以做出一个位宽为 64bit 的芯

片来满足 P-Bank 的需要,但这对技术的要求很高,在成本和实用性方面也都处于劣势。所以芯片的位宽一般都

较小。台式机市场所用的 SDRAM 芯片位宽最高也就是 16bit,常见的则是 8bit。这样,为了组成 P-Bank 所需

的位宽,就需要多颗芯片并联在一起工作。对于 16bit 芯片,组成一个 P-Bank 需要 4 颗(4×16bit=64bit)

SDRAM 芯片, 对于 8bit 芯片,组成一个 P-Bank 则需要 8 颗 SDRAM 芯片。

P-Bank 其实就是一组内存芯片的集合,这个集合的容量不限,但这个集合的总位宽必须与 CPU 位宽一致。随

着计算机应用的发展,一个系统只有一个 P-Bank 已经不能满足容量的需要。所以,芯片组开始可以支持多个

P-Bank,一次选择一个 P-Bank 工作, 这就有了芯片组支持多少(物理)Bank 的说法。

DIMM 是 SDRAM 集合形式的最终体现,每个 DIMM 至少包含一个 P-Bank 的芯片集合。在目前的 DIMM 标

准中,每个模组最多可以包含两个 P-Bank 的芯片集合,虽然理论上可以在一个 DIMM 上支持多个 P-Bank,

比如 SDRAM DIMM 有 4 个芯片选择信号(Chip Select,简称片选或 CS),理论上可以控制 4 个 P-Bank 的

芯片集合,只是由于种种原因而没有这么去做,比如设计难度、制造成本、芯片组的配合等。至于 DIMM 的面

数与 P-Bank 数量的关系,在之前的专题中已经明确了,面数≠P-Bank 数。

SDRAM 的逻辑 Bank 与芯片容量表示方法

1、逻辑 Bank 与芯片位宽

讲完 SDRAM 的外在形式,就该深入了解 SDRAM 的内部结构了。这里主要的概念就是逻辑 Bank。简单地说,

SDRAM 的内部是一个存储阵列,因为如果是管道式存储(就如排队买票),就很难做到随机访问了。

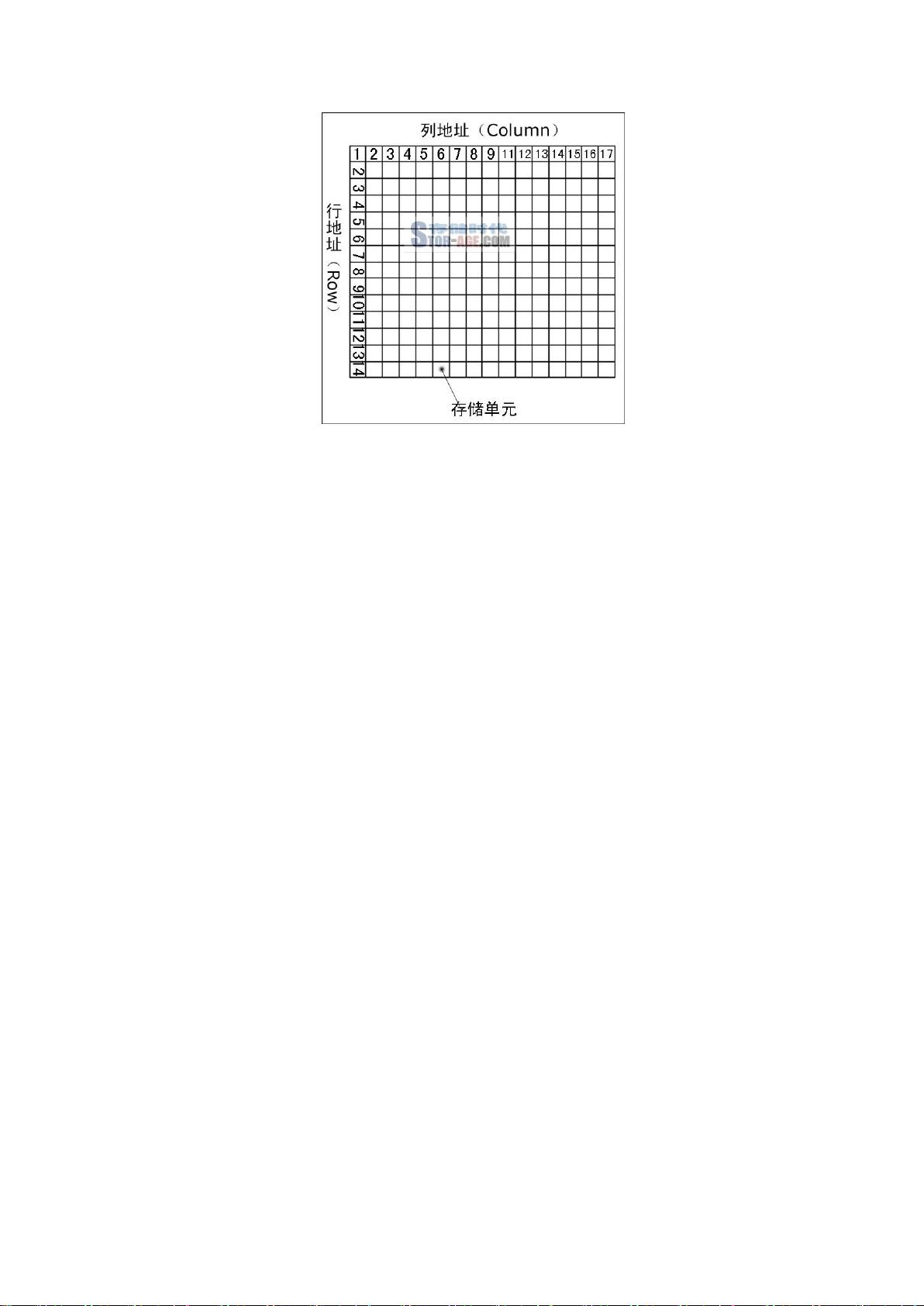

SDRAM 存储阵列就如同表格,和表格的检索原理一样,先指定一行(Row),再指定一列(Column),就可

以准确地找到所需要的单元格,这是内存芯片寻址的基本原理。对于内存,这个单元格称为存储单元,那么这个

表格(存储阵列)叫什么呢?它就是逻辑 Bank(Logical Bank,下文简称 L-Bank)。

L-Bank 存储阵列示意图

由于技术、成本等原因,不可能只做一个全容量的 L-Bank,而且最重要的是,由于 SDRAM 的工作原理限制,

单一的 L-Bank 将会造成非常严重的寻址冲突,大幅降低内存效率。所以人们将 SDRAM 内部分割成多个 L-

Bank,较早以前是两个,目前基本都是 4 个,这也是 SDRAM 规范中的最高 L-Bank 数量。在最新的 DDR-Ⅱ

的标准中,L-Bank 的数量提高到了 8 个。

这样,在进行寻址时就要先确定是哪个 L-Bank,然后再在这个选定的 L-Bank 中选择相应的行与列进行寻址。

可见对内存芯片的访问,一次只能是一个 L-Bank 工作。

从前文可知,SDRAM 内存芯片一次传输的数据量就是芯片的位宽,而这个数据量也是一次行&列寻址所对应的

存储单元的容量(也是 L-Bank 的位宽)。

2、内存芯片的容量

显然,内存芯片的容量就是内存芯片中所有 L-Bank 的存储单元的容量总和,即内存芯片中存储单元的数量 X 单

个存储单元的容量。

存储单元数量=行数×列数(得到一个 L-Bank 的存储单元数量)×L-Bank 的数量

单个存储单元的容量=内存芯片的位宽

我们通常用 M×W 的方式来表示芯片的容量, M 代表芯片中存储单元的总数,单位通常是兆,W 代表每个存

储单元的容量,也即是芯片的位宽(Width),单位是 bit,以此计算出来的芯片容量单位也是 bit。

上图是某公司对自己内存芯片容量的表示方法,我们计算一下后会发现这三个规格的容量都是 128Mbits,只是

由于位宽的变化引起了存储单元数量的变化。从这个例子可以看出,在相同的容量下,位宽可以采用多种不同的

设计。

3、与芯片位宽相关的 DIMM 设计

为什么在相同的容量下,芯片位宽会有多种不同的设计呢?这主要是为了满足不同领域的需要。我们已经知道

P-Bank 的位宽是固定的,当芯片位宽确定下来后,一个 P-Bank 中芯片的个数也就确定了,而前文讲过 P-

Bank 对芯片集合的位宽有要求,对芯片集合的容量则没有限制。高位宽的芯片可以让 DIMM 的设计简单一些

(因为所用的芯片少),而当芯片容量相同时,采用低位宽芯片的模组则可以获得更大的模组容量,因为芯片位

宽越低,在一个 P-Bank 中可以容纳的芯片就越多。比如上文中那个内存芯片容量标识图,容量都是 128Mbit,

合 16MB。如果 DIMM 采用双 P-Bank & 16bit 设计,那么模组只能容纳 8 颗芯片,容量总计 128MB。但如

果采用双 P-Bank & 4bit 设计,则模组可容纳 32 颗芯片,容量总计 512MB。DIMM 容量前后相差 4 倍,可

见芯片位宽对 DIMM 设计的影响。8bit 位宽芯片是桌面台式机内存容量与成本之间平衡性较好的选择,所以在

市场上也最为普及,而高于 16bit 位宽的芯片一般用在需要更大位宽的场合,如显卡等,至于 4bit 位宽芯片很

明显非常适用于大容量内存应用领域,如服务器等。

SDRAM 的引脚与封装

内存芯片要想工作,必须要与内存控制器有所联系,同时对于一个电气元件,电源供应也是必不可少的,而且数

据的传输要有一个时钟作为触发参考。因此,SDRAM 在封装时就要留出相应的引脚以供使用。 电源与时钟的

引脚就不必多说了,那么至少应该有哪些控制引脚呢?我们从内存寻址的步骤捋下来就基本可以明白了。

这里需要说明的是,与 DIMM 一样,SDRAM 有着自己的业界设计规范,在一个容量标准下,SDRAM 的引脚/

信号标准不能只考虑一种位宽的设计,而是要顾及多种位宽,然后尽量给出一个通用的标准,小位宽的芯片也许

会空出一些引脚,高位宽的芯片可能就全部用上了。不过容量不同时,设计标准也会有所不同,一般容量越小的

芯片所需要的引脚也就越少。

剩余44页未读,继续阅读

资源评论

JoneCheng2018

- 粉丝: 8

- 资源: 10

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功