www.latticesemi.com 1 rd1174_01.1

March 2014 Reference Design RD1174

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Introduction

The Synchronous dynamic random access memory (SDRAM) is dynamic random access memory (DRAM) that

has a synchronous interface. SDR (Single Data Rate) SDRAM can accept one command and transfer one word of

data per clock cycle. Typical SDR SDRAM clock rates are 66, 100, and 133 MHz (periods of 15, 10, and 7.5 ns). It

is a mainstream memory of choice due to speed, burst access and pipeline features.

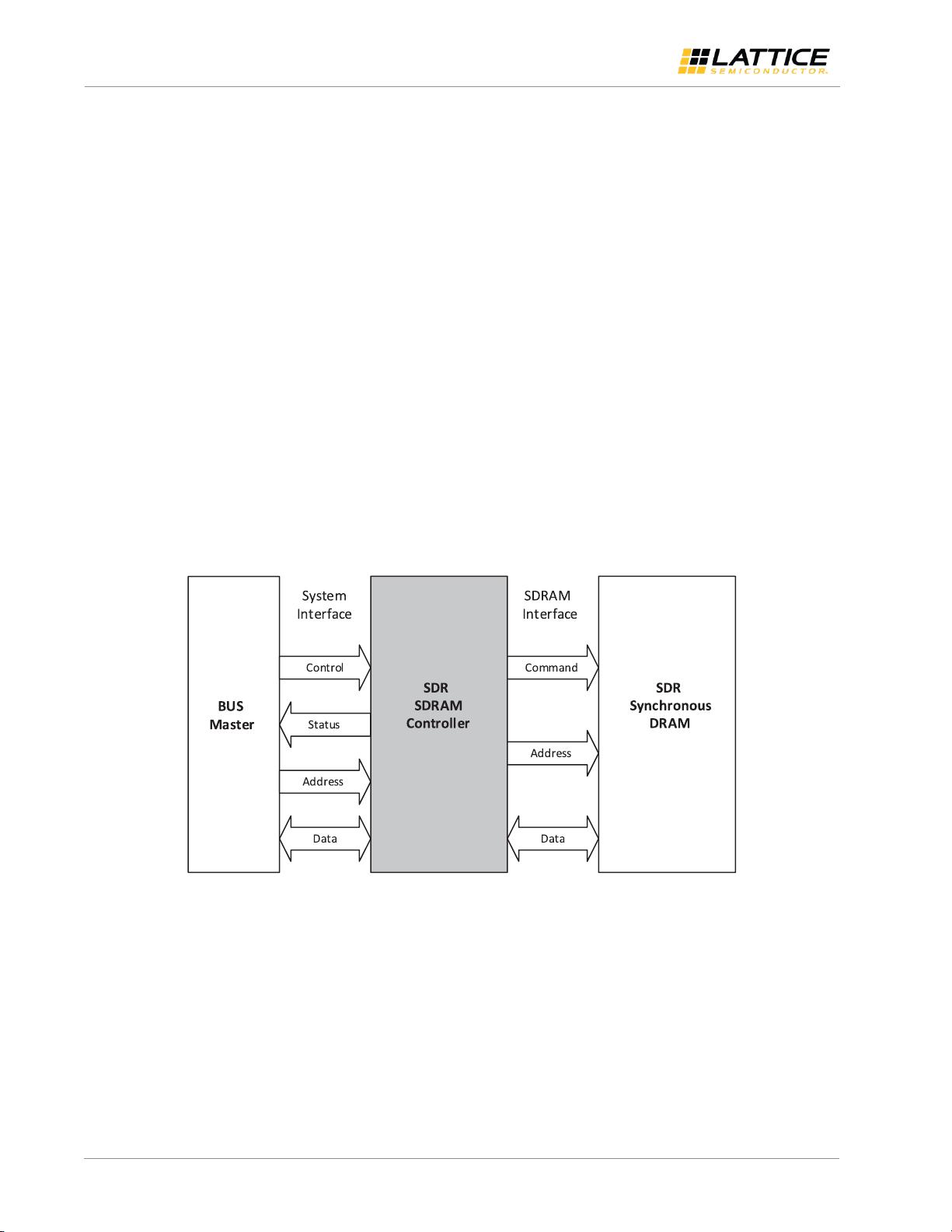

This SDRAM Controller reference design, located between the SDRAM and the bus master, reduces the user’s

effort to deal with the SDRAM command interface by providing a simple generic system interface to the bus master.

The design is implemented in Verilog language. The Lattice Diamond

®

for MachXO3L device and Lattice

iCEcube2™ for iCE40™ device Place and Route tool integrated with the Synopsys Synplify Pro

®

synthesis tool are

used for the implementation of the design. The design can be targeted to other iCE40 FPGA product family

devices.

Features

• Supports up to 27 address space, up to 4 banks

• Compile time configurable timing parameters like (CAS latency, tRP, tRCD, tREFC, tMRD …)

• Simplifies SDRAM command interface to standard system read/write interface

• Supports Auto Refresh and Self Refresh

• Supports flexible Row and Column addressing

• Supports CAS latencies of 2 and 3

• Run time configurable Refresh rate

• Automatically generates initialization and refresh sequences

• Flexible user controlled burst length of 1, 2, 4, 8 and page as well as stop signal

• User friendly control and status signals like busy, command acknowledge, data valid and request, indications for

completion of write and read data

• User controlled operation modes by configuring load mode register

• Provision for disable auto refresh

• Power down mode

SDR SDRAM Controller