Silicon Image Confidential for

Jincan Electronic Technology Co., Ltd.

Internal Use Only

Programmer’s Reference

SiI9022A and SiI9024A Transmitter

Programming Interface (TPI)

Programmer‘s Reference

Document # SiI-PR-1064-A

Silicon Image Confidential for

Jincan Electronic Technology Co., Ltd.

Internal Use Only

SiI9022A and SiI9024A Transmitter Programming Interface (TPI)

Programmer’s Reference

Silicon Image, Inc.

ii © 2009-2011 Silicon Image, Inc. All rights reserved. SiI-PR-1064-A

CONFIDENTIAL

September 2011

Copyright Notice

Copyright © 2009-2011 Silicon Image, Inc. All rights reserved. The contents of these materials contain proprietary and

confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Silicon Image,

Inc. or its affiliates. All rights are reserved and contents, (in whole or in part) may not be reproduced, downloaded,

disseminated, published, or transferred in any form or by any means, except with the prior written permission of Silicon

Image, Inc. or its affiliates. You may not use these materials except only for your bona fide non-commercial evaluation of

your potential purchase of products and/or services from Silicon Image or its affiliates; and only in connection with your

purchase of products or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions

stipulated. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right

to copy, modify, transfer, sublicense, publicly display, create derivative works of, distribute these materials, or otherwise

make these materials available, in whole or in part, to any third party.

Patents

The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by

Silicon Image, Inc. or its affiliates.

Trademark Acknowledgment

Silicon Image

®

, the Silicon Image logo, SteelVine

®

, Simplay

®

, Simplay HD

®

, the Simplay HD logo, Satalink

®

,

InstaPort

®

, the InstaPort Logo, and TMDS

®

are trademarks or registered trademarks of Silicon Image, Inc. in the United

States or other countries. HDMI

®

and the HDMI logo with High-Definition Multimedia Interface are trademarks or

registered trademarks of, and are used under license from, HDMI Licensing, LLC. in the United States or other countries.

MHL

®

and the MHL Logo are trademarks or registered trademarks of, and are used under license from, MHL, LLC. in

the United States or other countries. All other trademarks and registered trademarks are the property of their respective

owners in the United States or other countries. The absence of a trademark symbol does not constitute a waiver of Silicon

Image‘s trademark or other intellectual property rights with regard to a product name, logo or slogan.

Export Controlled Document

This document contains information subject to the Export Administration Regulations (EAR) and has a classification of

EAR99 or is controlled for Anti-Terrorism (AT) purposes. Transfer of this information by any means to an EAR Country

Group E:1 or foreign national thereof (whether in the U.S. or abroad) may require an export license or other approval

from the U.S. Department of Commerce. For more information, contact the Silicon Image Director of Global Trade

Compliance.

Further Information

To request other materials, documentation, and information, contact your local Silicon Image, Inc. sales office or visit the

Silicon Image, Inc. web site at www.siliconimage.com.

Revision History

Revision

Date

Comment

A

9/28/2011

First release; content extracted from PR-1032.

© 2009-2011 Silicon Image, Inc. All rights reserved.

Silicon Image Confidential for

Jincan Electronic Technology Co., Ltd.

Internal Use Only

SiI9022A and SiI9024A Transmitter Programming Interface (TPI)

Programmer’s Reference

Silicon Image, Inc.

SiI-PR-1064-A © 2009-2011 Silicon Image, Inc. All rights reserved. iii

CONFIDENTIAL

Contents

Overview ......................................................................................................................................................................... 1

Register Group Summary............................................................................................................................................. 2

Transmitter Programming Interface (TPI) ............................................................................................................... 2

Internal (Indexed) Registers ..................................................................................................................................... 3

Device-Specific Information ........................................................................................................................................ 3

SiI9022A and SiI9024A Transmitters ...................................................................................................................... 3

I

2

C Requirements ......................................................................................................................................................... 4

Summary of Host Software Tasks .................................................................................................................................... 5

Detailed Sequences ...................................................................................................................................................... 6

Initialization ............................................................................................................................................................. 6

Servicing a Hot Plug Event ...................................................................................................................................... 7

Changing Video Modes ........................................................................................................................................... 8

HDCP Authentication and Encryption ..................................................................................................................... 8

HDCP Revocation Check ........................................................................................................................................ 8

General Programming Registers ...................................................................................................................................... 9

Identification ................................................................................................................................................................ 9

Video Configuration .................................................................................................................................................. 10

Video Mode ........................................................................................................................................................... 10

Input Setup Operations .............................................................................................................................................. 13

DE Generator Register Set ......................................................................................................................................... 16

InfoFrame Data ...................................................................................................................................................... 18

Using xvYCC ......................................................................................................................................................... 20

System Control ...................................................................................................................................................... 22

Audio Configuration .................................................................................................................................................. 23

Configuring Audio using S/PDIF ........................................................................................................................... 23

Configuring Audio using I

2

S .................................................................................................................................. 25

Configuring Audio for DSD Format ...................................................................................................................... 28

Interrupt Service ............................................................................................................................................................ 29

Interrupt Enable Register ........................................................................................................................................... 29

Interrupt Status Register ............................................................................................................................................ 29

Interrupt Operation .................................................................................................................................................... 30

TPI System .................................................................................................................................................................... 32

Power State Control and Hot Plug Management ........................................................................................................... 33

Transmitter Power State Register ............................................................................................................................... 33

Hot vs Cold Wakeup Modes .................................................................................................................................. 34

Hot Plug Management ............................................................................................................................................... 34

Hot Plug Service Loop........................................................................................................................................... 34

Operating Sequences ............................................................................................................................................. 35

HDCP Implementation ................................................................................................................................................... 37

Control for HDCP ...................................................................................................................................................... 37

HDCP Operation .................................................................................................................................................... 38

HDCP Data Structure ............................................................................................................................................. 38

Auxiliary HDCP Registers ..................................................................................................................................... 40

Silicon Image Confidential for

Jincan Electronic Technology Co., Ltd.

Internal Use Only

SiI9022A and SiI9024A Transmitter Programming Interface (TPI)

Programmer’s Reference

Silicon Image, Inc.

iv © 2009-2011 Silicon Image, Inc. All rights reserved. SiI-PR-1064-A

CONFIDENTIAL

List of Figures

Figure 1. Transmitter Data Flow Paths ............................................................................................................................ 1

Figure 2. Transmitter TPI Register Interface to Host ....................................................................................................... 9

Figure 3. Input Bus Diagram for Different Formats....................................................................................................... 12

Figure 4. Transmitter Video Data with Sync Decoding ................................................................................................. 14

Figure 5. DE Generator Measurements .......................................................................................................................... 16

Figure 6. INT Pulse on Event other than HTPLG .......................................................................................................... 31

Figure 7. Setup Events ................................................................................................................................................... 35

Figure 8. Hot Plug and Interrupt Timing........................................................................................................................ 36

List of Tables

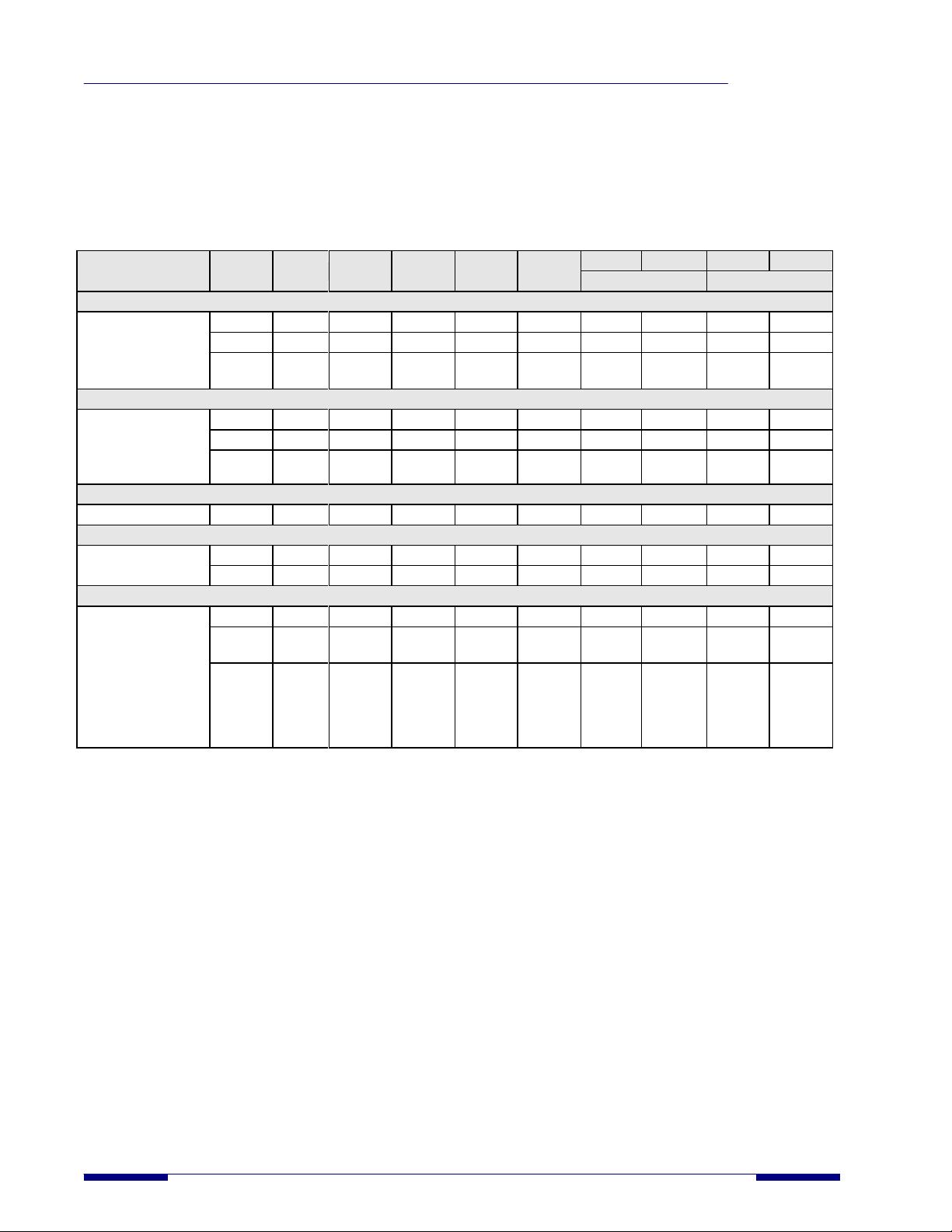

Table 1. Register Group Summary ................................................................................................................................... 2

Table 2. TPI Identification Registers (RO) ...................................................................................................................... 9

Table 3. Device ID Information ..................................................................................................................................... 10

Table 4. TPI Video Mode Data (R/W) ........................................................................................................................... 10

Table 5. TPI Input Bus and Pixel Repetition Data (R/W) .............................................................................................. 11

Table 6. 480p Mode Format Matching Example ........................................................................................................... 11

Table 7. TPI AVI Input and Output Format Data (R/W) ................................................................................................ 13

Table 8. Sync Register Configuration and Sync Monitoring Registers .......................................................................... 15

Table 9. TPI YC Input Mode Select (R/W) ................................................................................................................... 15

Table 10. Explicit Sync DE Generator Registers (TPI 0x60[7] = 0) ............................................................................. 17

Table 11. Embedded Sync Extraction Registers (TPI 0x60[7] = 1) ............................................................................... 18

Table 12. TPI AVI InfoFrame Data (R/W) ..................................................................................................................... 19

Table 13. TPI Miscellaneous InfoFrame Data (R/W) .................................................................................................... 21

Table 14. TPI System Control (R/W) ............................................................................................................................ 22

Table 15. TPI Audio Configuration Write Data (RW) ................................................................................................... 24

Table 16. Configuration of I

2

S Interface (RW) .............................................................................................................. 26

Table 17. Mapping of I

2

S Interface (RW) ...................................................................................................................... 26

Table 18. Stream Header Settings for I

2

S (RW) ............................................................................................................. 27

Table 19. TPI Interrupt Enable (R/W) ........................................................................................................................... 29

Table 20. TPI Interrupt Status (R/W) ............................................................................................................................. 29

Table 21. TPI Device Power State Control Data (R/W) ................................................................................................ 34

Table 22. Hot Plug Timing Requirements ...................................................................................................................... 36

Table 23. HPD to INT Delays ........................................................................................................................................ 36

Table 24. Mapping of HDCP Data to TPI Register Bits ................................................................................................ 37

Table 25. TPI Security Registers ................................................................................................................................... 39

Table 26. TPI HDCP Revision Data (RO) ..................................................................................................................... 40

Table 27. TPI KSV and V* Value Data (R/W) .............................................................................................................. 41

Table 28. TPI V* Value Readback Data (RO) ............................................................................................................... 41

Table 29. TPI Aksv Readback Data (RO) ...................................................................................................................... 41

Silicon Image Confidential for

Jincan Electronic Technology Co., Ltd.

Internal Use Only

SiI9022A and SiI9024A Transmitter Programming Interface (TPI)

Programmer’s Reference

.

SiI-PR-1064-A © 2009-2011 Silicon Image, Inc. All rights reserved. 1

CONFIDENTIAL

Overview

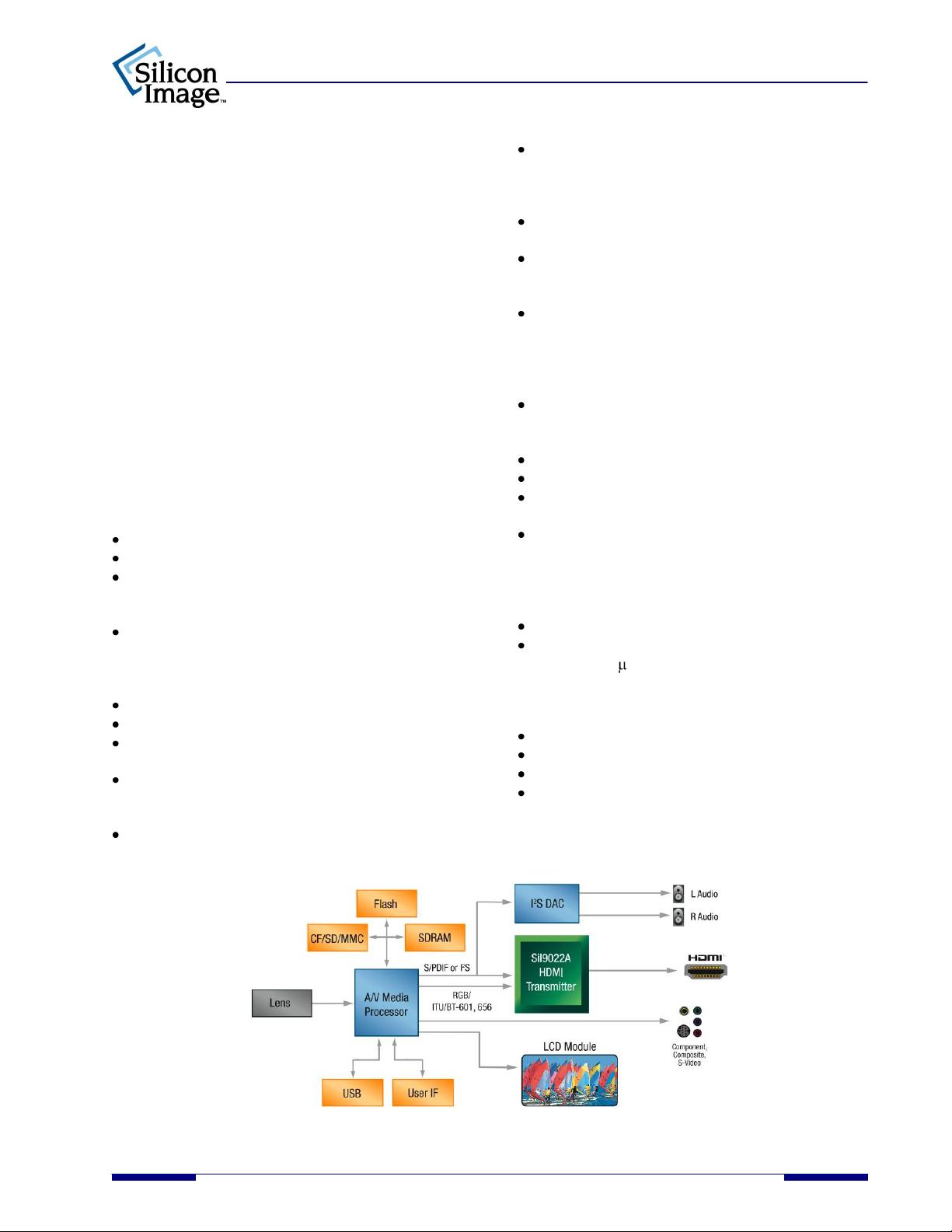

Silicon Image HDMI transmitter solutions merge independent video and audio streams for transmission over HDMI. To

do this, the transmitter employs a unique mechanism that allows host graphics and audio software to interact with the

HDMI transmitter.

All new devices implement a simplified interface and special logic that automates most HDMI functions. This

Transmitter Programming Interface (TPI) maps a concise set of registers into I

2

C address space that the host can readily

access.

TPI offers a significantly simplified operating scheme, using built-in hardware to handle tasks such as the following.

Secure operation is fully automatic on devices equipped with HDCP. With only a single-bit write, the device

establishes and maintains link security, interrupting the host only if the secure link is lost.

DDC arbitration is handled cleanly, allowing the host to simply request the bus and then fetch EDID information

directly – no need to program transfers into or out of a FIFO. Arbitration is handled even when link security is

enabled.

Complex audio setup is nearly eliminated. Hardware calculates N/CTS values and automatically sends out the

appropriate packet information with no setup needed.

All frequency-dependent internal settings, such as for PLLs, are derived automatically in hardware from the video

mode information that has been programmed.

In addition:

Devices still implement the standard Silicon Image register set used by legacy transmitters, for backwards

compatibility with special functions in existing code.

All devices implement an automated CEC controller, using the Silicon Image standard CEC Programming Interface

(CPI).

Many versions additionally support HDCP, implemented as part of the automated solution and requiring no host

intervention for normal operation.

This document describes the TPI programming solution for the following devices.

HDCP-enabled

Version

Non HDCP-enabled

Version

Upgrade to this existing

product

Application

SiI9024A Tx

SiI9022A Tx

SiI9022/24 Tx

HDMI Mobile

Figure 1 illustrates the major functional blocks for a typical TPI-based transmitter solution.

Video

Video/Audio

Host

HDMI TV

SiI HDMI Tx

Intr

TMDS

-- CEC --

-- DDC --

TPI-based

Logic Core

Host I

2

C bus

S/PDIF

EDID

Hot

Plug

HDCP

Engine

HDCP

Engine

I

2

S

-- TPI --

-- CPI --

-- DDC --

CEC

Engine

DDC

pass-

thru

Arbiter

Programming Subsystem

Figure 1. Transmitter Data Flow Paths

评论7