1300 Henley Court

Pullman, WA 99163

509.334.6306

www.digilentinc.com

RGB-to-DVI (Source) 1.2 IP Core User Guide

Revised April 23, 2015; Author Elod Gyorgy

DOC#: 506-031

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 1 of 4

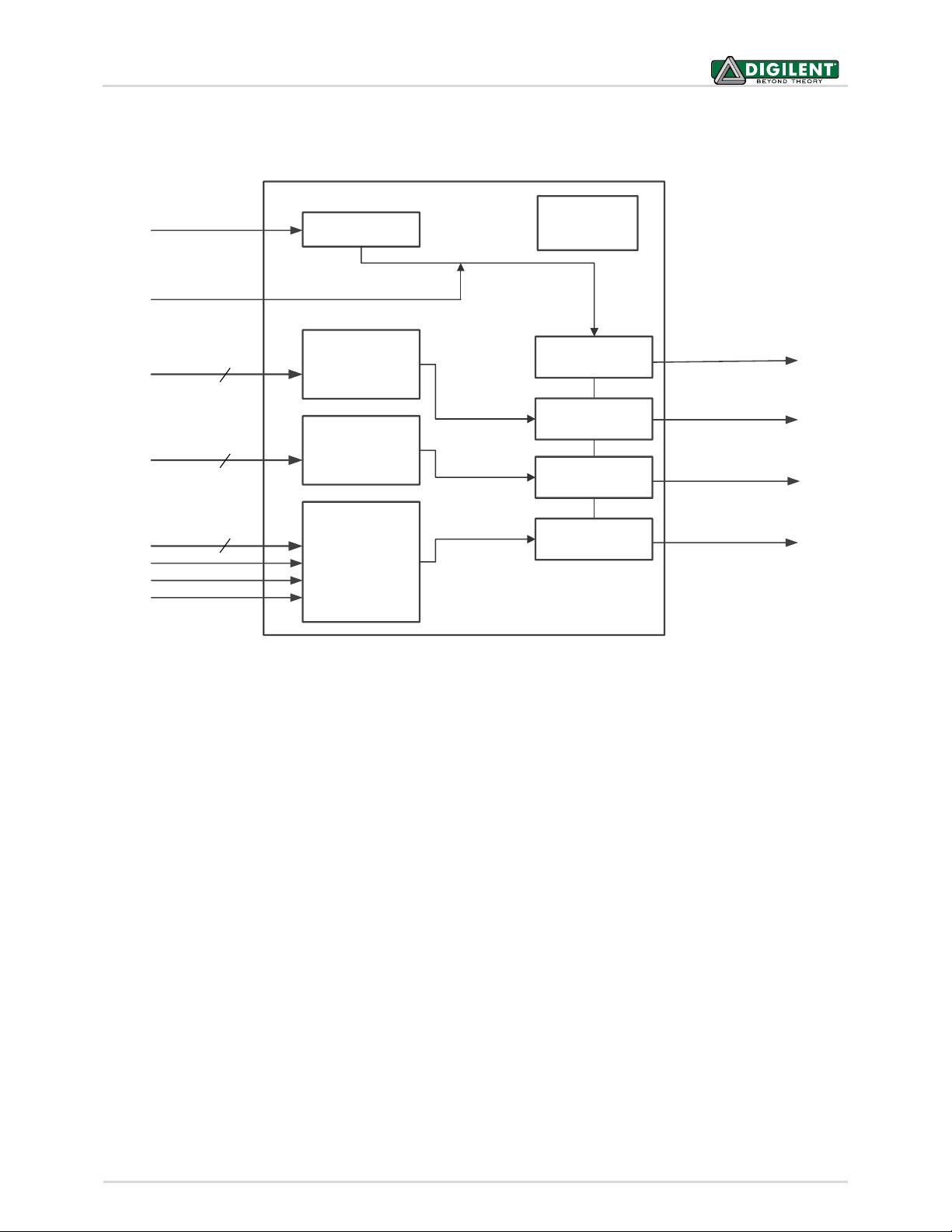

1 Introduction

This user guide describes the Digilent RGB-to-DVI Video

Encoder Intellectual Property. This IP interfaces directly to

raw transition-minimized differential signaling (TMDS) clock

and data channel outputs as defined in DVI 1.0 specs for

Source devices. It encodes 24-bit RGB video data along with

the pixel clock and synchronization signals.

2 Features

Connects directly to top-level digital visual

interface (DVI) port

24-bit video (clocked parallel video data with

synchronization signals) input

Resolutions supported: 1920x1080/60Hz down to

800x600/60Hz (148.5 MHz – 40 MHz)

Digilent interfaces used: TMDS

3 Performance

The IP does not constrain the clocks it requires as inputs. The exception is out-of-context synthesis,

when the rgb2dvi_ooc.xdc contains the necessary constraints. However, this file is not used in top-level

synthesis. Therefore, clocks need to be constrained in the top-level design either manually or by relying

on the auto-derived constraints, if using clock modifying blocks. For more information see [1].

Although the IP itself supports the maximum frequency outlined in DVI 1.0 specifications (165 MHz) for

pixel clock, the actual maximum frequency might be lower depending on the actual FPGA part or speed

grade. Check the part datasheet for F

MAX_BUFIO

, which is the most likely reason for failed timing.

RGB_PixelClk should be constrained for F

MAX_BUFIO

/5. Consequently, this is the maximum pixel clock

frequency supported on that FPGA family and speed grade.

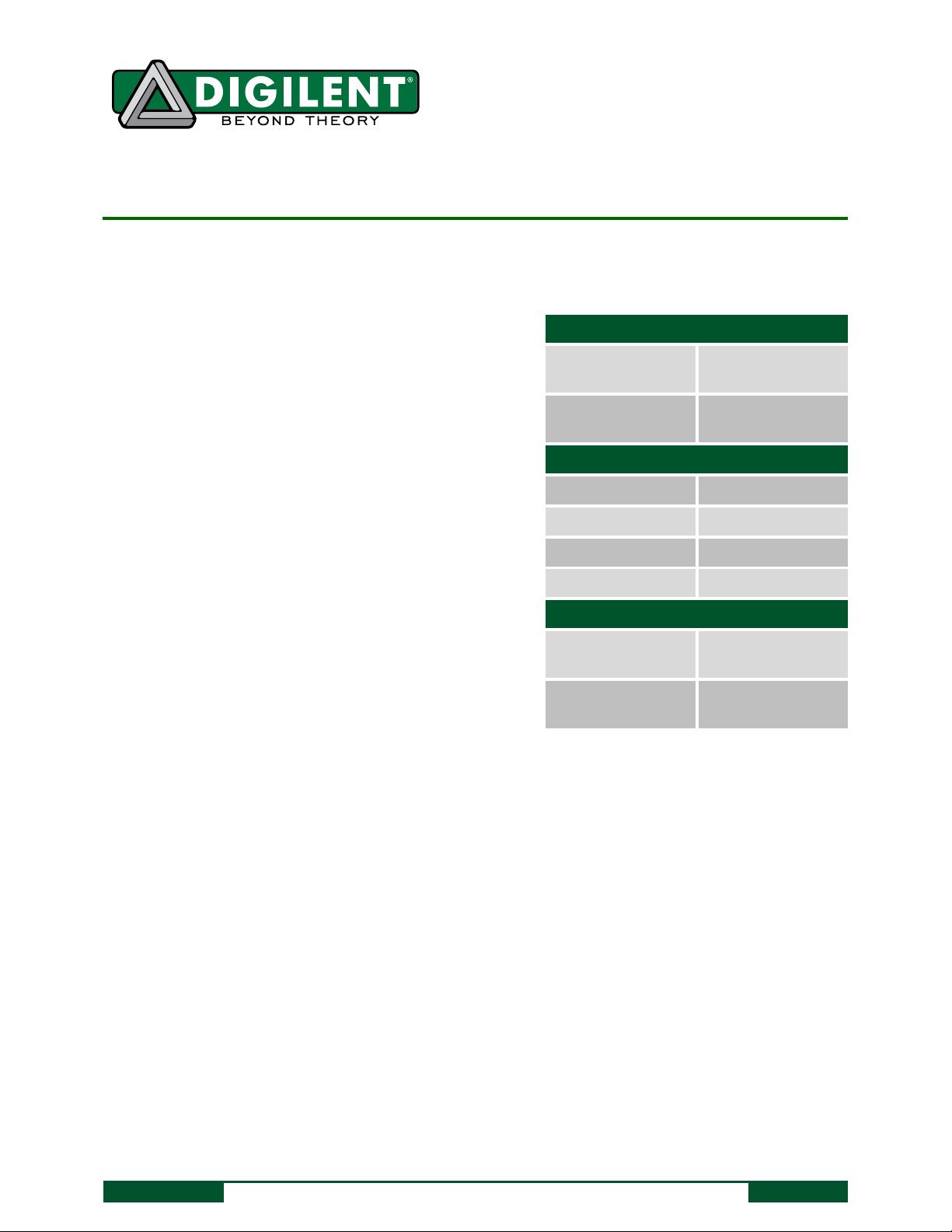

IP quick facts

Supported device

families

Zynq®-7000, 7 series

Supported user

interfaces

Xilinx: vid_io

Digilent: TMDS

Provided with core

Design files

VHDL

Simulation model

VHDL Behavioral

Constraints file

XDC

Software driver

N/A

Tested design flows

Design entry

Vivado™ Design

Suite 2014.3

Synthesis

Vivado Synthesis

2014.3