SNUG Boston,2002 Clock Dividers Made Easy

Clock Dividers Made Easy

Mohit Arora

Design Flow and Reuse (CR&D)

ST Microelectronics Ltd

Plot No. 2 & 3, Sector 16A

Noida-201301, India

(www.st.com

)

ABSTRACT

Dividing a clock by an even number always generates 50% duty cycle output. Sometimes it is

necessary to generate a 50% duty cycle frequency even when the input clock is divided by an

odd or non-integer number. This paper talks about implementation of unusual clock dividers.

The paper starts up with simple dividers where the clock is divided by an odd number (Divide by

3, 5 etc) and then later expands it into non-integer dividers (Divide by 1.5, 2.5 etc). The circuits

are simple, efficient and are cheaper and faster than any external PLL alternatives. This paper

also covers Verilog code implementation for a non-integer divider.

ST Microelectronics Ltd.

______________________________________________________________________________

SNUG Boston,2002 Page 2 Clock Dividers Made Easy

INDEX

1. Introduction................................................................................................................................4

2. Simple clock divider where the input clock is divided by an odd integer ................................4

3. Odd integer division with 50% duty cycle..................................................................................4

4. Non-integer division (duty cycle not 50%).................................................................................6

4.1 Divide by 1.5 with duty cycle not exactly 50%...........................................................................6

4.2 Divide by 4.5 with duty cycle not exactly 50% (counter implementation).....................................7

4.2.1 Verilog code for Divide by 4.5 ...........................................................................................8

5 Alternative approach for divide by-N ..........................................................................................9

5.1 Divide by 1.5 (LUT implementation).........................................................................................9

5.2 Divide by 2.5 (LUT Implementation).......................................................................................11

5.3 Divide by 3 with 50% duty cycle output...................................................................................14

5.4 Divide by 5 with 50% duty cycle output...................................................................................16

6. Conclusions...............................................................................................................................18

7. Acknowledgements...................................................................................................................18

8. References .................................................................................................................................18

9. Author & Contact information..................................................................................................19

ST Microelectronics Ltd.

______________________________________________________________________________

SNUG Boston,2002 Page 3 Clock Dividers Made Easy

List of Figures

Figure 1: Divide by 7 using a Moore Machine ...............................................................................4

Figure 2: Timing diagram for Divide by 3 (N=2) with 50% duty cycle output..............................5

Figure 3: Divide by 3 using T flip-flop with 50 % duty cycle output.............................................6

Figure 4: Divide by 1.5 using T flip-flop(Duty cycle not 50%) .....................................................6

Figure 5: Timing diagram for Divide by 1.5 using T flip-flop (Duty Cycle not 50%)...................7

Figure 6:Timing diagram for counter implementation of Divide by 4.5 (duty cycle not 50%)......8

Figure 7: Divide by 3 (duty cycle not 50%)....................................................................................9

Figure 8:Timing diagram for Divide by 3 (duty cycle not 50%) ....................................................9

Figure 9: LUT Implementation for Divide by 1.5 (duty cycle output not 50%)...........................10

Figure 10: Timing diagram for Divide by 1.5 (LUT implementation) .........................................10

Figure 11: Timing diagram for Divide by 1.5 where input B is delayed with respect to CLK.....11

Figure 12: Divide by 5 (Duty cycle not 50%)...............................................................................12

Figure 13: Timing diagram for Divide by 5 (duty cycle not 50%) ...............................................12

Figure 14: LUT Implementation for Divide by 2.5 (duty cycle output not 50%).........................12

Figure 15: Timing diagram for Divide by 2.5 (LUT implementation) .........................................13

Figure 16: LUT Implementation for Divide by 3 (50% duty cycle output)..................................15

Figure 17: Timing diagram for Divide by 3 (LUT implementation) ............................................15

Figure 18: LUT Implementation for Divide by 5 (50% duty cycle output)..................................17

Figure 19: Timing diagram for Divide by 5 (LUT implementation) ............................................17

List of Tables

Table 1: LUT and the Output table for Divide by 1.5 circuit........................................................11

Table 2: LUT and the Output table for Divide by 2.5 circuit........................................................14

Table 3: LUT table output for Divide by 3 circuit........................................................................16

Table 4: LUT output table for Divide by 5 circuit........................................................................18

ST Microelectronics Ltd.

______________________________________________________________________________

SNUG Boston,2002 Page 4 Clock Dividers Made Easy

1. Introduction

In some designs, you need to provide a number of phase-related clocks to various components.

In most cases, you generate the needed clocks by dividing a master clock by a power of two

(synchronous division). However, sometimes, it is desirable to divide a frequency by an odd or

even fractional divisor. In these cases, no synchronous method exists without generating a higher

frequency master clock.

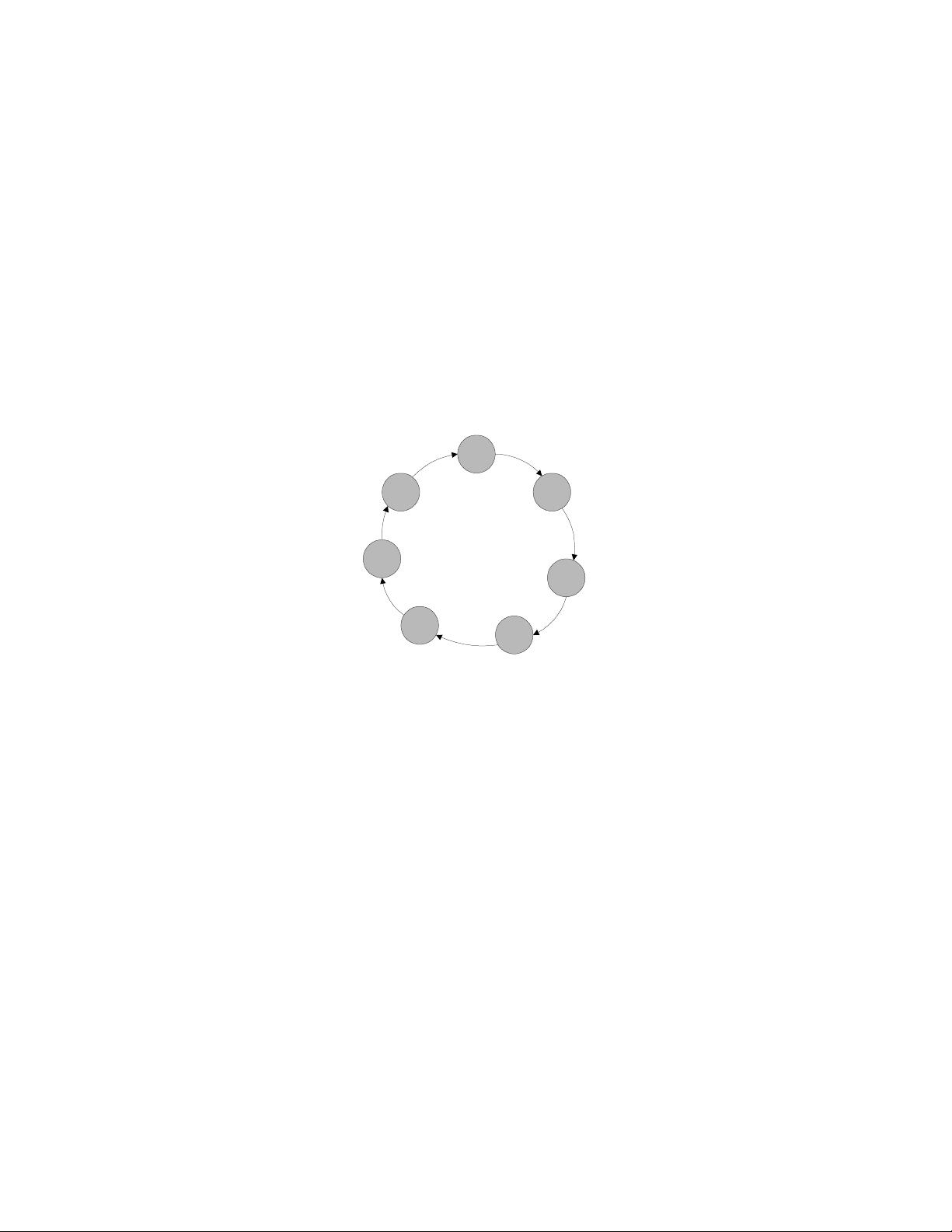

2. Simple clock divider where the input clock is divided by an odd integer

A synchronous divide by integer can be easily specified using a Moore machine. For example,

Divide by 7.

0/0

1/0

2/0

3/0

4/1

5/1

6/1

Figure 1: Divide by 7 using a Moore Machine

The above does not generate a 50% duty cycle.

3. Odd integer division with 50% duty cycle

Conceptually, the easiest way to create an odd divider with a 50% duty cycle is to generate two

clocks at half the desired output frequency with a quadrature-phase relationship (constant 90°

phase difference between the two clocks).

You can then generate the output frequency by exclusive-ORing the two waveforms together.

Because of the constant 90° phase offset, only one transition occurs at a time on the input of the

exclusive-OR gate, effectively eliminating any glitches on the output waveform.

Let’s see how it works by taking an example where the reference clock is divided by 3.

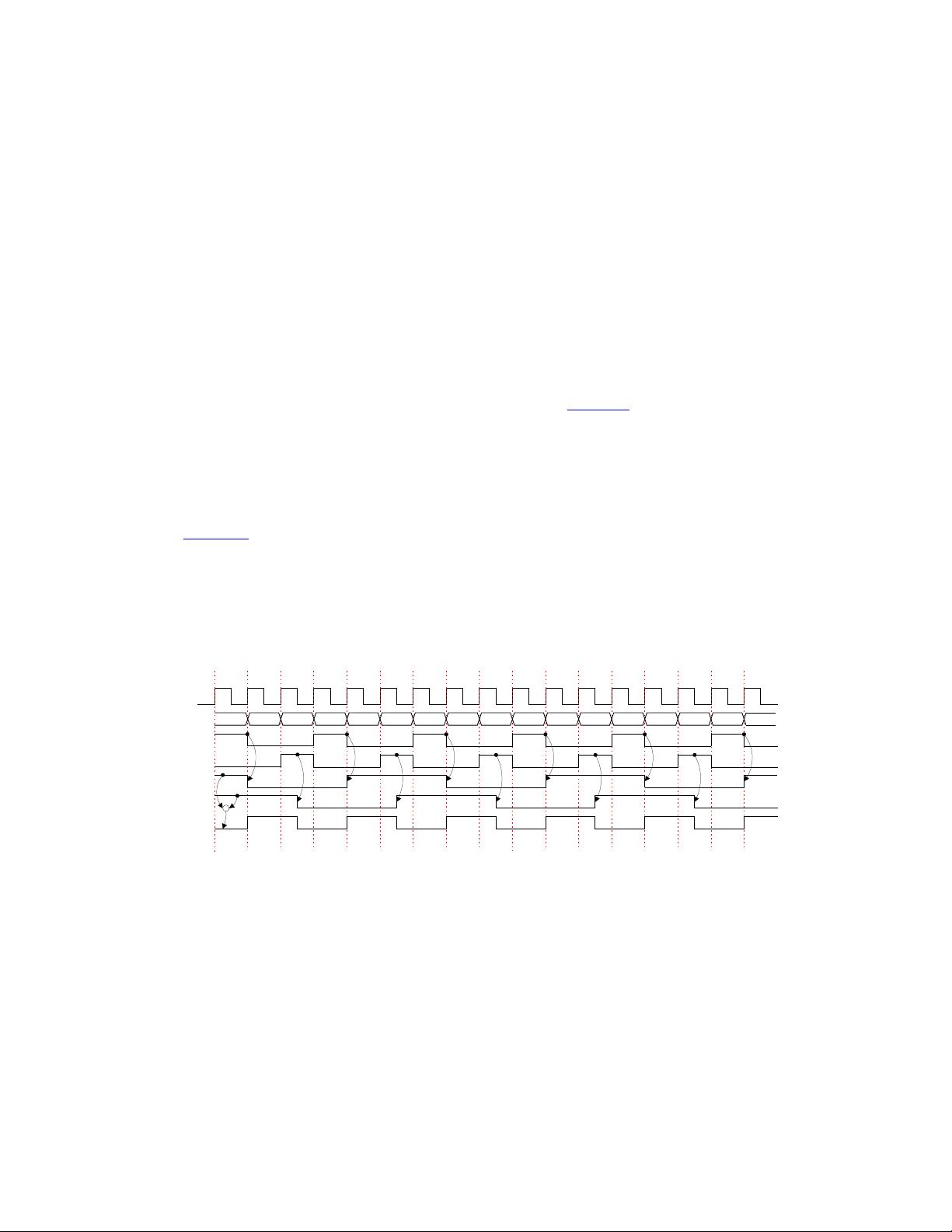

Below are the sequential steps listed for division by an odd integer:

STEP I:

Create a counter that counts from 0 to (N –1) and always clocks on the rising edge of

the input clock where N is the natural number by which the input reference clock is supposed to

be divided (N != Even)

ST Microelectronics Ltd.

______________________________________________________________________________

SNUG Boston,2002 Page 5 Clock Dividers Made Easy

For Divide by 3 : i.e. counts from 0 to 2 …N = 3

For Divide by 5 : i.e. counts from 0 to 4 …N = 5

For Divide by 7 : i.e. counts from 0 to 6 …N = 7

Note: The counter is incremented on every rising edge of the input clock (ref_clk) and the

counter is reset to ZERO when the terminal count of counter reaches to (N-1).

STEP II: Take two toggle flip-flops and generate their enables as follows:

tff1_en : T FF1 enabled when the counter value = 0

tff2_en : T FF2 enabled when the counter value = (2 for Divide by 3 counter , 3 for Divide by 5

counter, 4 for Divide by 7 counter and likewise) as shown in Figure 2

STEP III : div1 : output of T FF1 à triggered on rising edge of input clock (ref_clk)

div2 : output of T FF2 à triggered on falling edge of input clock (ref_clk)

Note: The output div1 and div2 of two T Flip flops generate the divide-by-2N waveforms as

shown in Figure 2.

STEP IV :

Final output clock: clkout (Divide by N) is generated by XORing the div1 and div2

waveforms.

012012012 10212001

ref_clk

count[1:0]

tff_1en

tff_2en

div1

div2

clkout

+

Figure 2: Timing diagram for Divide by 3 (N=2) with 50% duty cycle output

Complete circuit for Divide by 3 is shown on the next page.