vhdl.rar_full

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

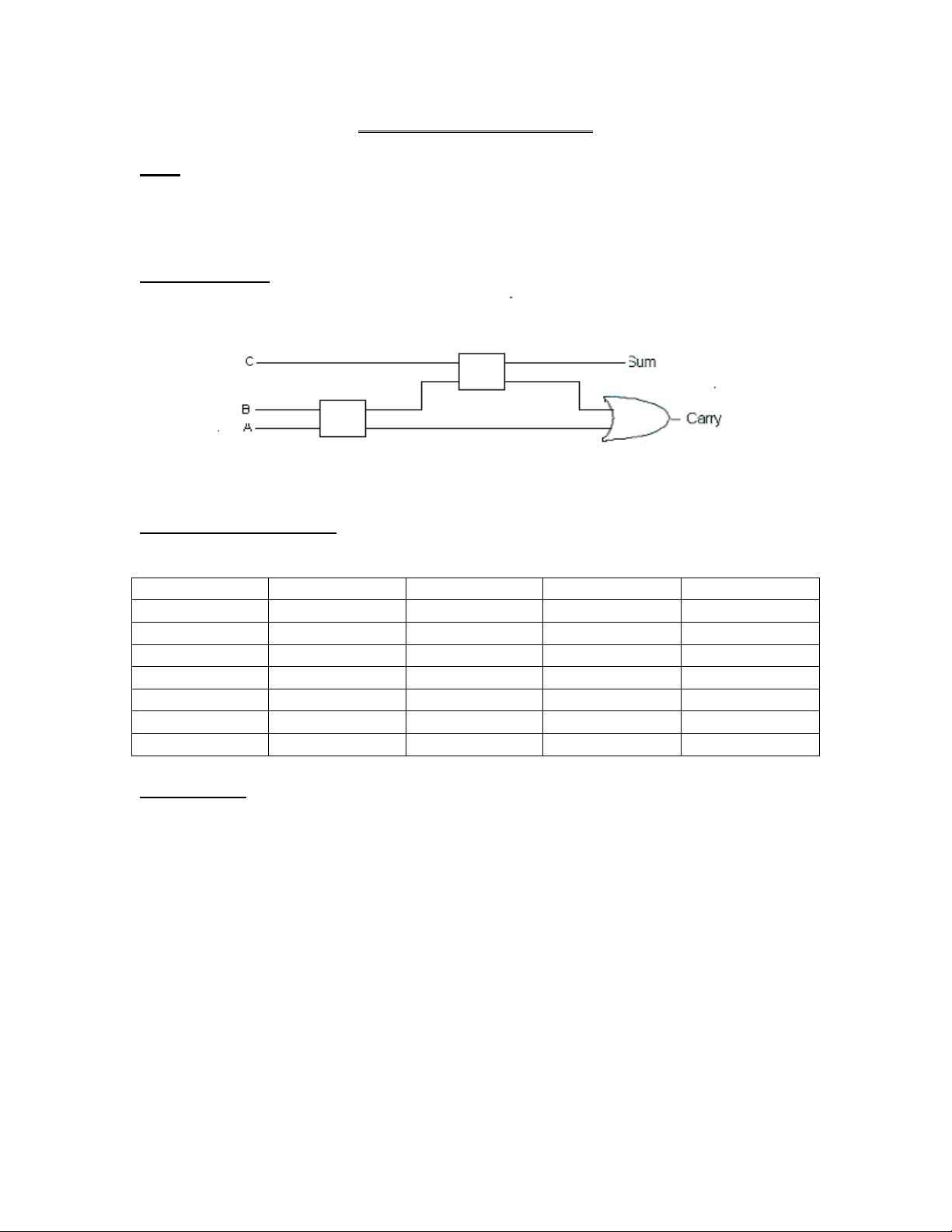

VHDL,全称是VHSIC(Very High Speed Integrated Circuit)硬件描述语言,是一种用于电子设计自动化领域的编程语言,广泛应用于数字逻辑系统的建模、仿真和综合。它允许工程师用高级抽象的方式描述数字系统的行为和结构,这些系统可以是微处理器、FPGA(现场可编程门阵列)或ASIC(专用集成电路)。 标题"vhdl.rar_full"暗示了这个压缩包包含了一个完整的VHDL项目,可能是一个关于VHDL实现的全加器设计。全加器是数字电路中的基本组件,它可以处理两个二进制位的加法以及一个进位输入,产生一个和输出和一个进位输出。在计算机科学和电子工程中,全加器是构建更复杂算术逻辑单元(如加法器和乘法器)的基础。 描述提到"full adder is implemented using VHDL",这意味着在这个项目中,设计者使用VHDL语言编写代码来实现了一个全加器的功能。全加器的VHDL实现通常包括两个部分:结构描述和行为描述。结构描述定义了逻辑门的物理连接,而行为描述则关注于系统的输入和输出如何随时间变化。 标签"full"可能指的是全加器,也可能代表完整或全面的VHDL设计示例。 压缩包内的文件名称列表中,“Full Adder using Half Adder.doc”可能是文档形式的说明,详细解释了如何通过两个半加器来构建全加器。半加器只能处理两个二进制位的加法,没有考虑进位,而在全加器中,需要将两个半加器的结果和进位信号组合起来。 “full.vhd”文件很可能就是VHDL源代码文件,其中包含了全加器的实体声明、结构体定义和过程描述。实体声明定义了接口,即输入和输出信号;结构体定义描述了逻辑门的连接;而过程描述则用时序语句(如IF-THEN-ELSE或CASE语句)表示计算过程。 在学习这个VHDL全加器实现时,可以了解到以下关键概念: 1. **VHDL语法**:包括数据类型、实体、结构体、过程、库和包的使用。 2. **逻辑门**:AND、OR、NOT等基本逻辑门的VHDL表示。 3. **并行和顺序语句**:如何在VHDL中表示并行和串行操作。 4. **组合逻辑和时序逻辑**:全加器的设计涉及到组合逻辑(无记忆元件的电路),因为它根据当前输入立即产生输出。 5. **半加器和全加器**:理解半加器的原理和其与全加器的区别。 6. **模拟和验证**:使用VHDL代码进行逻辑仿真,检查设计是否符合预期。 这个压缩包提供了一个学习和实践VHDL设计的好机会,特别是对于那些对数字逻辑和FPGA设计感兴趣的人来说。通过分析和理解这个全加器的VHDL实现,可以深入掌握VHDL语言,并为设计更复杂的数字系统打下基础。

vhdl.rar (2个子文件)

vhdl.rar (2个子文件)  full.vhd 425B

full.vhd 425B Full Adder using Half Adder.doc 256KB

Full Adder using Half Adder.doc 256KB- 1

- 粉丝: 85

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功