VHDL.zip_vhdl

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

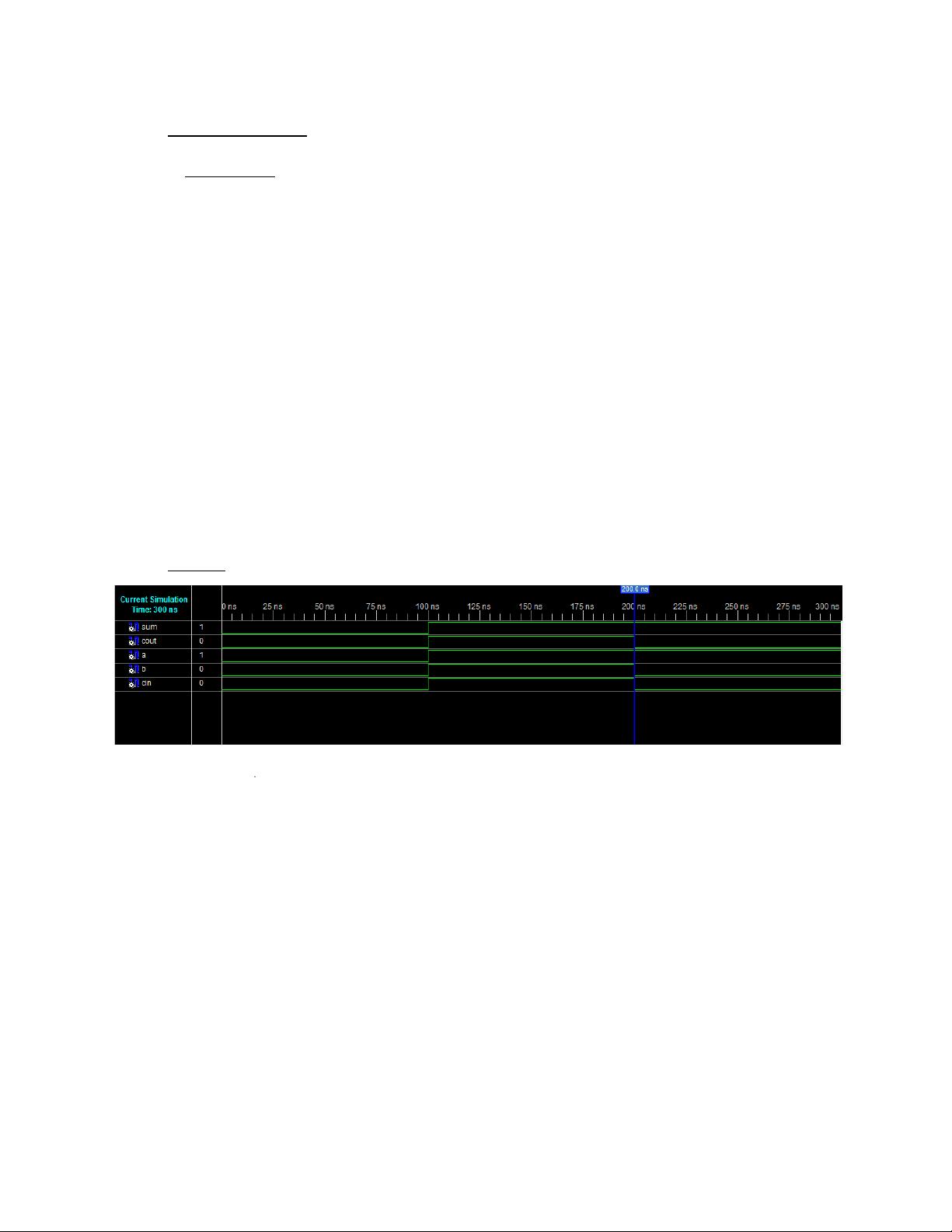

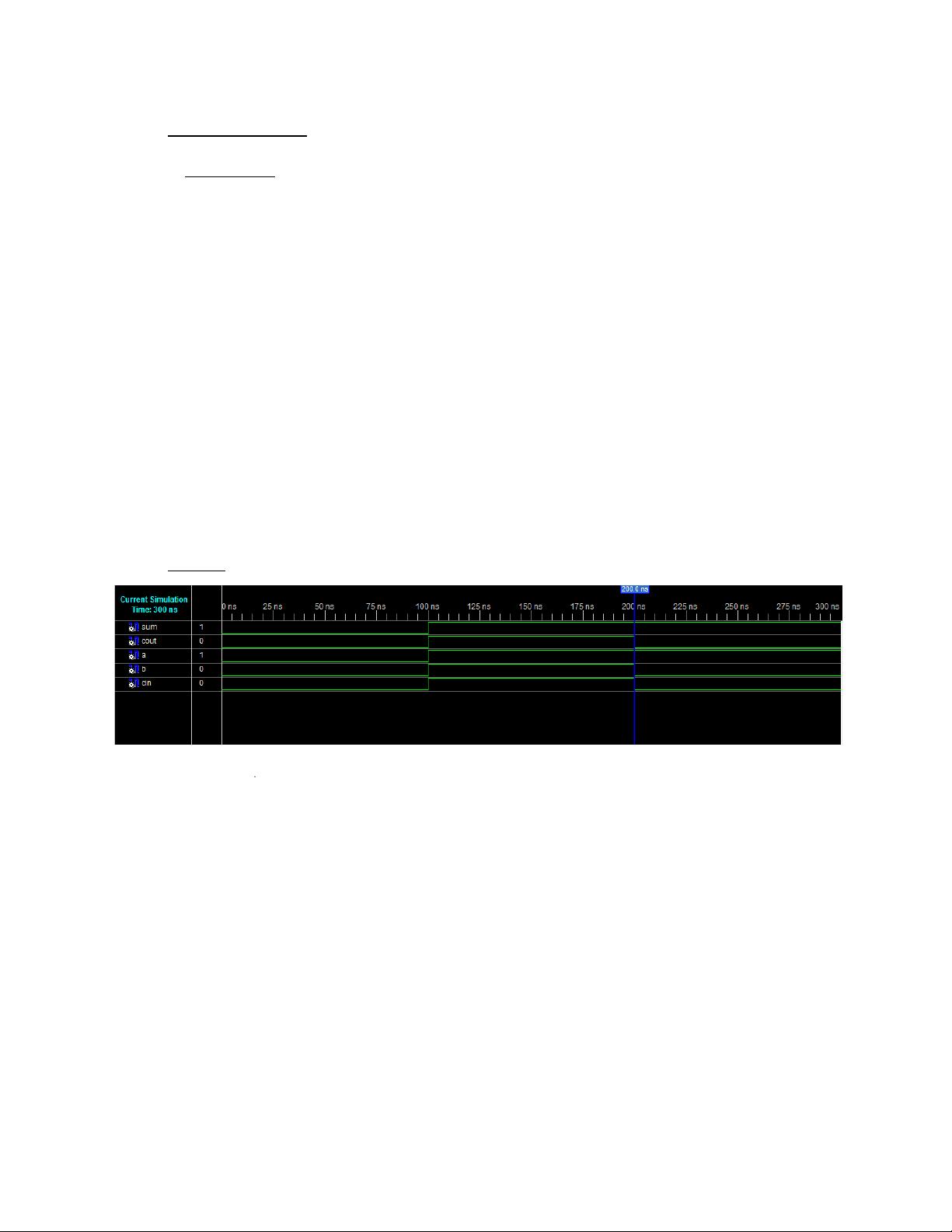

VHDL,全称Very High Density Integrated Circuit Hardware Description Language,是一种用于数字电子系统设计的硬件描述语言。它允许工程师以一种接近于自然语言的方式描述电路的行为和结构,从而实现数字系统的建模、仿真、综合和验证。VHDL在集成电路设计、FPGA(现场可编程门阵列)和ASIC(应用专用集成电路)设计中广泛应用。 标题“VHDL.zip_vhdl”表明这是一个关于VHDL的资料压缩包,可能包含了一系列与VHDL编程相关的文档。压缩包内的文件以数字命名,可能是按照一定的顺序排列,比如教程的章节或者问题的难度等级。 在描述中提到,“These are some vhdl program...”,意味着这些文档可能包含了VHDL的代码实例,可能包括基本的逻辑门、触发器、计数器、移位寄存器等基本数字逻辑组件的设计,也可能涵盖了更复杂的系统如微处理器、存储器接口、通信协议等。 标签“vhdl”进一步确认了这个压缩包的内容专注于VHDL学习和实践。通常,这样的资源可能包括以下几方面的知识点: 1. **VHDL语法**:学习VHDL的基础,包括实体(Entity)、结构体(Architecture)、库(Library)、过程(Process)、信号(Signal)等概念。 2. **数据类型和运算符**:了解VHDL中的不同类型,如BIT、INTEGER、std_logic_vector等,以及如何进行算术、比较和逻辑运算。 3. **组件实例化**:如何在设计中使用已有的IP核或模块,通过实例化语句将它们集成到自己的设计中。 4. **行为和结构描述**:理解VHDL可以同时支持行为和结构描述,行为描述关注系统行为,而结构描述关注硬件实现细节。 5. **仿真和综合**:学习如何使用VHDL进行仿真验证,确保设计的正确性,以及如何将VHDL代码转换为具体的硬件逻辑,即综合过程。 6. **测试平台**:创建和使用测试平台(Testbench)来验证设计的功能,包括时钟信号、激励信号和预期输出的定义。 7. **错误调试**:了解如何解读编译和综合错误,以及如何修复这些问题。 8. **FPGA和ASIC设计流程**:理解从VHDL设计到硬件实现的整个流程,包括约束设置、布局布线、下载和硬件验证。 9. **高级主题**:如并行处理、时序分析、状态机设计、接口协议实现等。 压缩包中的5个.docx文件可能分别涵盖了这些主题的一个或多个方面,每个文件可能代表一个独立的课题或教程步骤。例如,第一份文档可能介绍VHDL的基本语法,第二份可能是数据类型的深入讲解,第三、四、五份可能依次递进,讨论更复杂的设计方法和实际案例。 这个“VHDL.zip_vhdl”压缩包是一个全面学习VHDL的好资源,适合初学者逐步掌握VHDL语言,并进行实际的数字系统设计。通过阅读和实践这些文档,读者可以加深对数字电路的理解,提升硬件设计能力。

VHDL.zip (5个子文件)

VHDL.zip (5个子文件)  1.docx 64KB

1.docx 64KB 3.docx 27KB

3.docx 27KB 2.docx 57KB

2.docx 57KB 4.docx 28KB

4.docx 28KB 5.docx 36KB

5.docx 36KB- 1

- 粉丝: 102

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 图像处理中的White Patch算法来实现白平衡,MATLAB实现

- Python 爬虫:把廖雪峰的教程转换成 PDF 电子书

- 2024 年 Java 开发人员路线图.zip

- matplotlib-3.7.5-cp38-cp38-win-amd64.whl

- Android TV 开发框架: 包含 移动的边框,键盘,标题栏

- 图像处理中白平衡算法之一的灰度世界算法的MATLAB实现

- Cython-3.0.10-cp38-cp38-win-amd64.whl

- zotero安卓版"Zotero Beta"版本1.0.0-118

- Web应用项目开发的三层架构

- 基于QT和OpenCV的Mask编辑工具(python源码)

信息提交成功

信息提交成功