external-SRAM.zip_SRAM

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

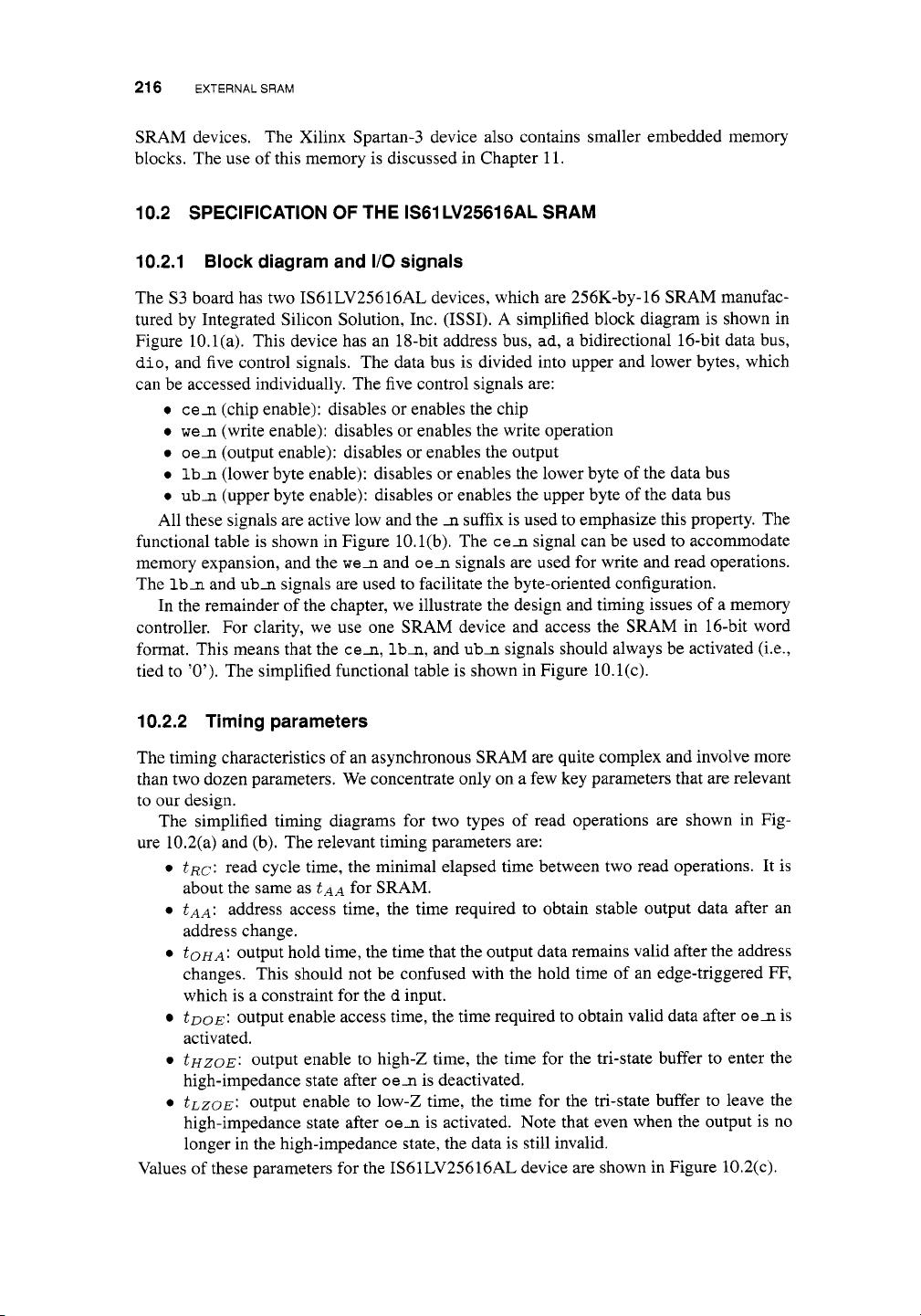

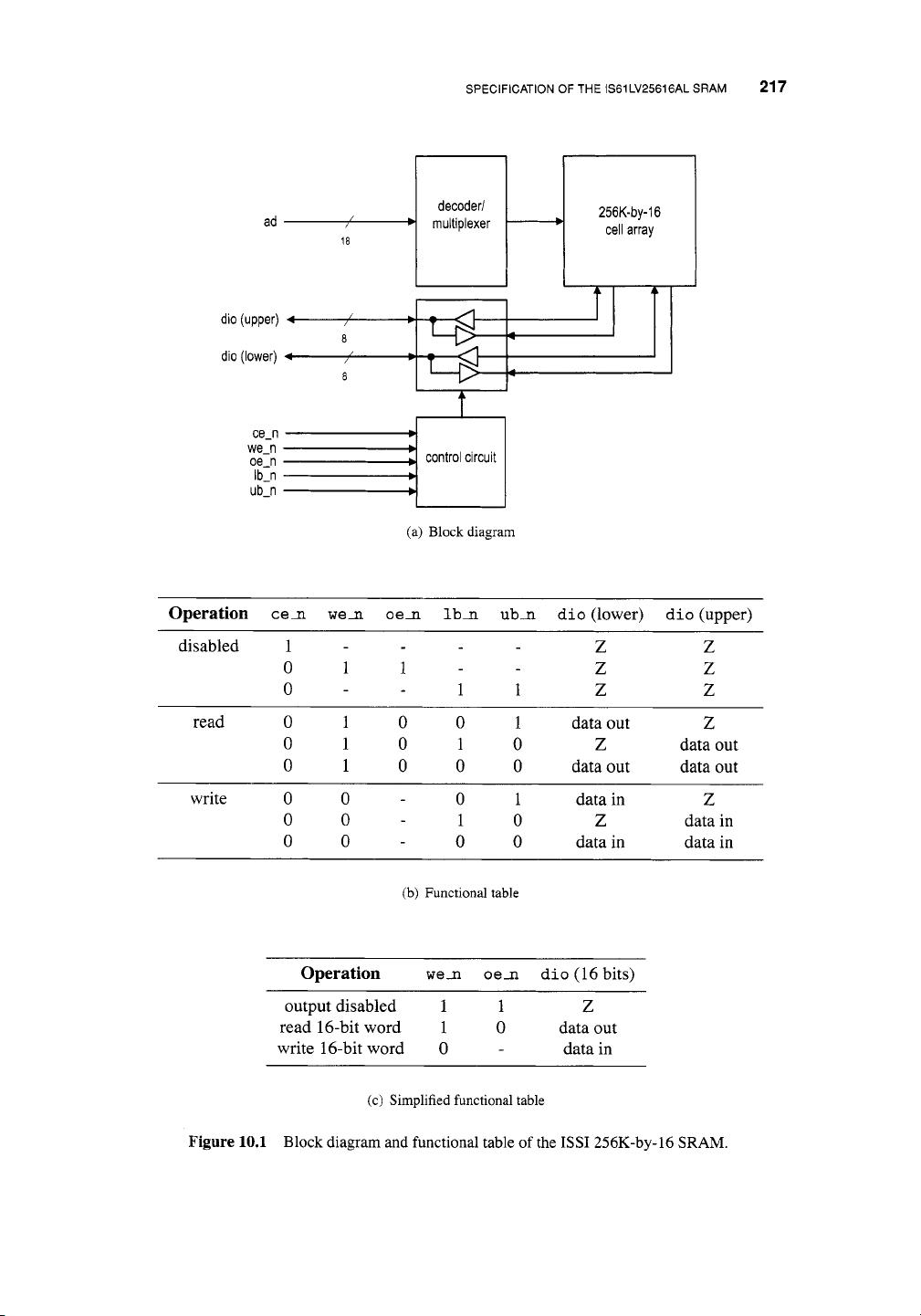

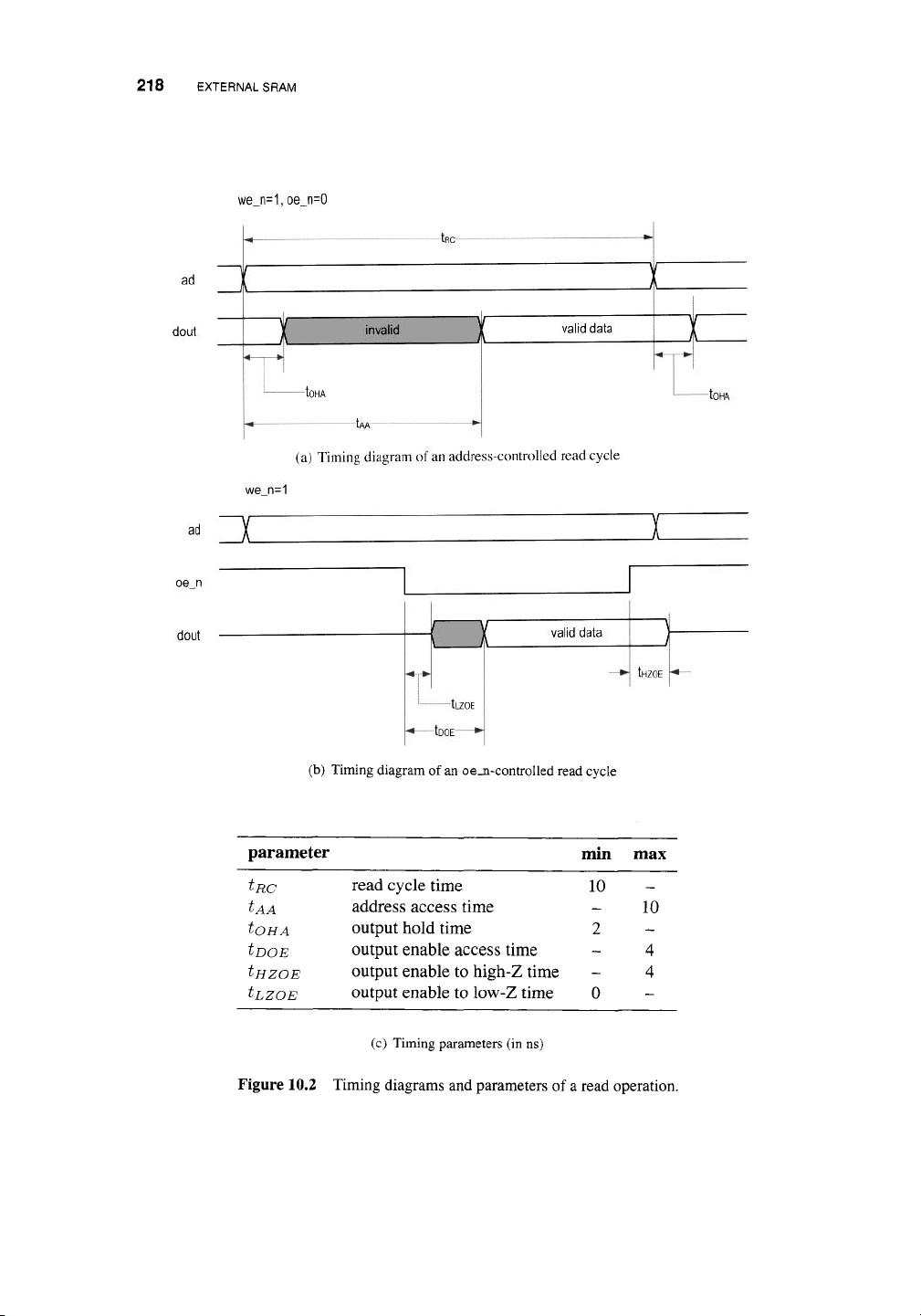

外部SRAM(External Static Random-Access Memory)是嵌入式系统和数字电路设计中的一个重要组成部分,主要用于扩展系统内存,提供比内部RAM更大的存储空间。在本资料包"external-SRAM.zip_SRAM"中,主要探讨了如何在硬件描述语言(HDL)中实现外部SRAM接口,以便在FPGA(Field-Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit)设计中有效利用这种存储器。 外部SRAM通常采用并行接口,它由多个数据线、地址线和控制线组成,例如读/写使能信号、片选信号以及时钟信号等。在HDL实现过程中,我们需要关注以下几个关键知识点: 1. **接口设计**:设计有效的外部SRAM接口,包括确定合适的地址宽度、数据宽度以及控制信号的逻辑。例如,地址线数量决定了可访问的存储单元数量,而数据线数量则决定了每次传输的数据量。 2. **时序控制**:理解和掌握SRAM的读写时序是至关重要的。这涉及到对时钟边沿的精确控制,以确保在正确的时间点进行数据传输,避免数据丢失或冲突。 3. **同步与异步设计**:同步设计中,所有操作都基于同一时钟信号,确保了操作的一致性;而异步设计则允许不同模块有各自的时钟域,需要考虑时钟域间的同步问题,如使用三态缓冲器或电平转换器。 4. **读写操作**:理解SRAM的读写操作流程,包括预充电、行地址选择、列地址选择和数据传输等步骤。在HDL中,这些操作需要通过控制逻辑来实现。 5. **错误检测与处理**:在实际应用中,可能会遇到诸如地址越界、数据错误等问题,因此需要在设计中加入适当的错误检测机制,如奇偶校验、CRC校验等。 6. **IP核集成**:现代FPGA设计中,经常使用预先封装好的SRAM IP核,如Xilinx的Block RAM或Intel的Memory Interface Generator。了解如何在HDL中调用和配置这些IP核,可以简化设计流程。 7. **性能优化**:为了提高系统性能,可能需要进行带宽优化、减少访问延迟或提高并行处理能力。这可能涉及地址解码优化、多端口访问策略等。 8. **仿真与验证**:使用HDL仿真工具进行功能和时序验证,确保SRAM接口设计的正确性和可靠性。 压缩包中的"external SRAM.pdf"文件可能详细阐述了以上各个知识点,并提供了一些具体的代码实例和设计技巧。通过深入学习这份资料,你可以掌握在实际项目中实现外部SRAM接口的技能,提升你的数字系统设计能力。

external-SRAM.zip (1个子文件)

external-SRAM.zip (1个子文件)  external SRAM.pdf 1.21MB

external SRAM.pdf 1.21MB- 1

- 粉丝: 106

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功