N-0.5fenpinqi.rar_vhdl 分频_分频

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

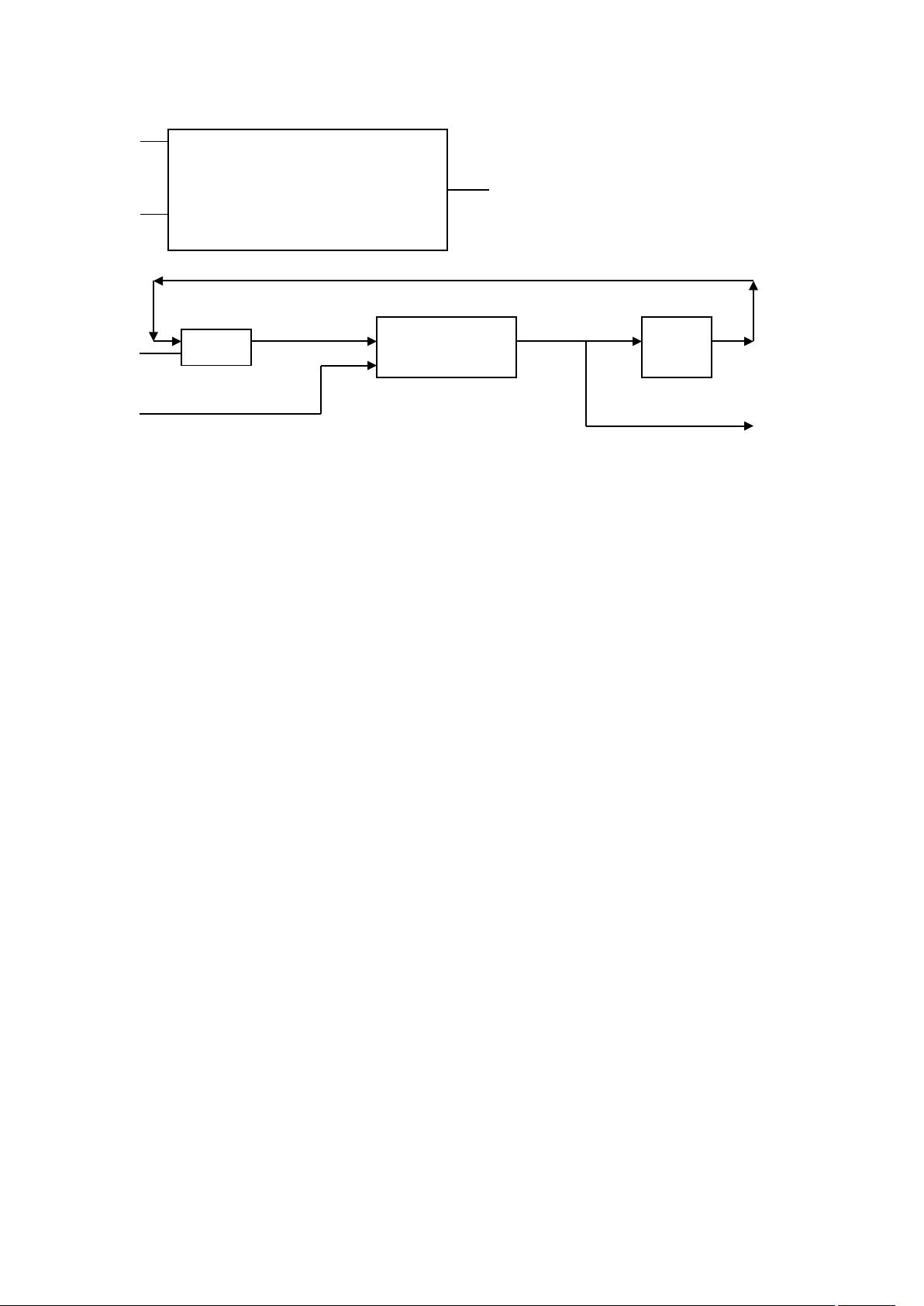

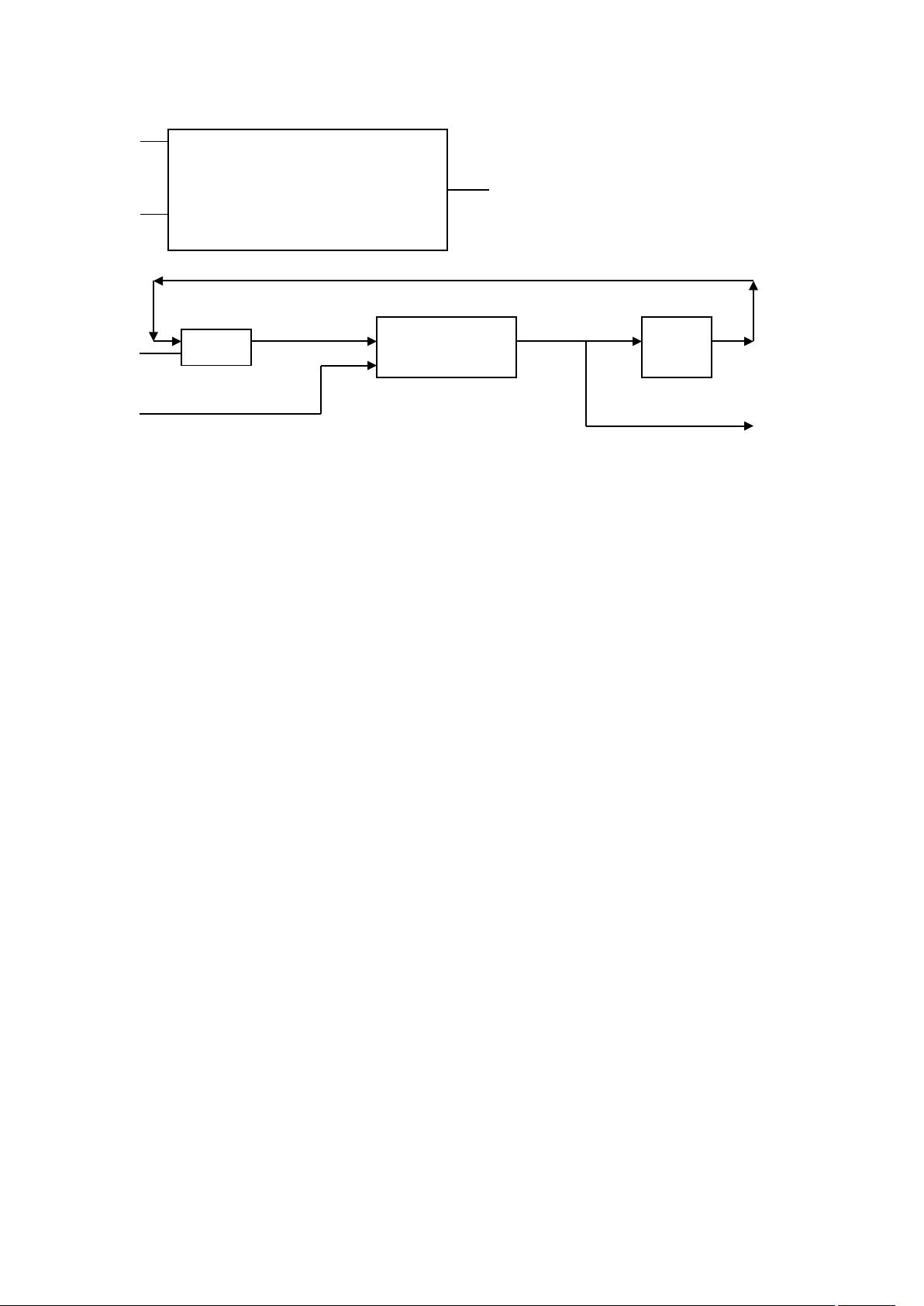

在数字信号处理领域,分频是常见的操作,用于降低信号的频率。VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于 FPGA(Field-Programmable Gate Array)和 ASIC(Application-Specific Integrated Circuit)的设计。本案例中,"N-0.5fenpinqi.rar_vhdl 分频_分频" 是一个关于使用VHDL实现分频器的设计,特别是针对N-0.5分频方法。 N-0.5分频意味着输出频率是输入频率的1/(2N)。这种分频方式在某些应用中是必需的,比如在通信系统、定时生成器或者频率合成器中。传统的分频器通常设计为整数分频,例如N分频,但N-0.5分频提供了一种更精确的频率控制手段。 VHDL代码中,分频器通常由计数器和比较器组成。计数器会累积输入时钟的脉冲,当达到预设的分频值N时,比较器会触发一个输出脉冲。在N-0.5分频器中,计数器需要计数到N-0.5,这涉及到浮点数的概念,这在硬件描述语言中并不常见。设计者可能需要将N-0.5转换为二进制小数表示,然后用二进制计数来模拟浮点数的效果。 压缩包内的文件 "N-0.5半整分频器.doc" 很可能是设计文档,详细阐述了分频器的设计原理、步骤以及VHDL代码实现。它可能会包括计数器的结构,如使用同步或异步清零,上升沿或下降沿触发,以及如何处理溢出问题。同时,文档也可能讨论了如何处理非整数分频产生的时序问题,确保输出信号的准确性和稳定性。 "www.pudn.com.txt" 文件可能是一个引用来源或资源链接,指向了更多关于VHDL分频器设计的相关资料或者论坛讨论,帮助读者深入理解或找到其他相关设计实例。 在实际设计中,为了确保设计的可综合性和效率,VHDL代码需要遵循良好的编程实践,如模块化设计,清晰的接口定义,以及避免使用不易硬件实现的复杂逻辑。此外,还需要进行仿真验证,确保设计满足功能需求,无错误和漏洞。 "N-0.5fenpinqi.rar_vhdl 分频_分频" 提供了一个使用VHDL设计的非整数分频器示例,这对于理解和掌握高级分频技术,特别是在FPGA和ASIC设计中的应用,是非常有价值的。通过学习和分析这个设计,工程师能够提升其在数字系统设计中的技能,特别是在频率控制和信号处理方面。

N-0.5fenpinqi.rar (2个子文件)

N-0.5fenpinqi.rar (2个子文件)  www.pudn.com.txt 218B

www.pudn.com.txt 218B N-0.5半整分频器.doc 30KB

N-0.5半整分频器.doc 30KB- 1

- 粉丝: 78

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功