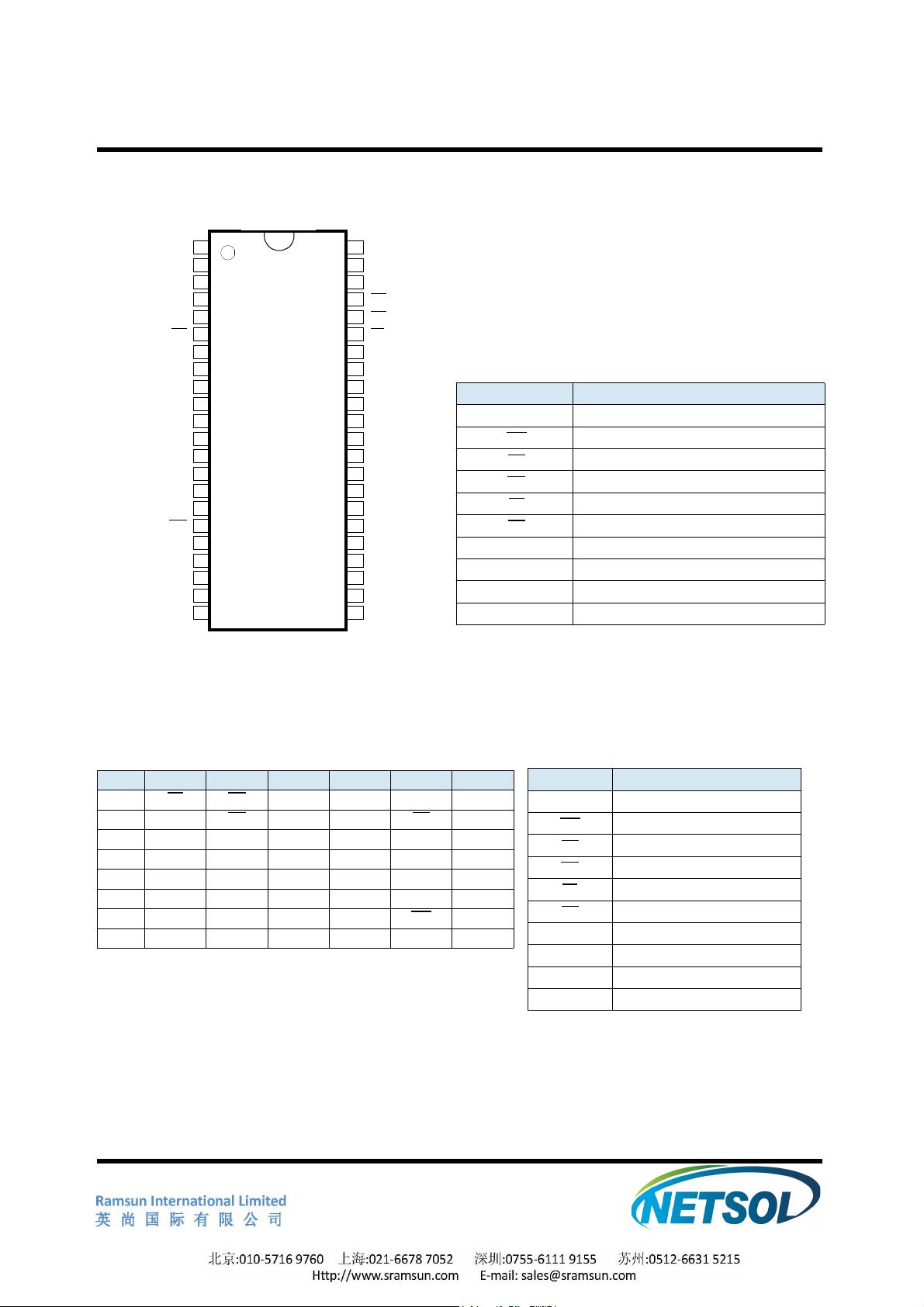

在电子设计领域,FPGA(Field-Programmable Gate Array)是一种广泛应用的可编程逻辑器件,它可以被配置为实现各种不同的数字逻辑功能。在许多FPGA设计中,SRAM(Static Random-Access Memory)是不可或缺的组成部分,因为它提供了快速的读写访问能力,常用于数据缓存或状态存储。本文将深入探讨FPGA中的SRAM存储块以及如何使用Verilog进行设计。 让我们了解什么是SRAM。SRAM是一种非易失性内存,它的特点是数据在电源关闭后不会丢失,与DRAM(Dynamic RAM)相比,它具有更快的访问速度,但功耗和集成度相对较低。在FPGA中,SRAM存储块可以被配置为用户指定的任何逻辑功能,例如作为简单的寄存器或者复杂的存储阵列。 标题提到的“sram.zip”可能包含了一个FPGA SRAM存储块的Verilog实现。Verilog是一种硬件描述语言,常用于FPGA和ASIC设计,它允许设计师以类似于软件编程的方式描述数字系统的行为和结构。在“sram_ctl.zip”中,很可能包含了SRAM控制器的源代码,这个控制器负责管理和控制SRAM的读写操作。 在设计FPGA中的SRAM时,我们需要关注以下几个关键知识点: 1. **接口设计**:定义SRAM的输入和输出信号,如读写使能(WR_EN, RD_EN)、地址总线(ADDR)、数据输入/输出(DATA_IN, DATA_OUT)等。 2. **读写操作**:Verilog代码中需要实现读取和写入操作的逻辑,这通常涉及到对地址和数据信号的处理,并根据读写使能信号进行操作。 3. **同步与异步设计**:同步设计使用时钟信号来同步所有操作,而异步设计则不依赖单一时钟。在FPGA中,同步设计更常见,因为它提供了更好的时序控制和可靠性。 4. **初始化**:如果需要SRAM在上电时具有特定的初始值,可以使用初始化块(initial begin ... end)来实现。 5. **错误检测与校验**:为了提高系统的鲁棒性,可以添加ECC(Error Correction Code)或其他错误检测机制。 6. **资源优化**:在FPGA中,SRAM占用大量的逻辑资源。通过精心的逻辑设计和布局布线,可以优化资源使用并提高性能。 7. **仿真与验证**:使用工具如ModelSim或Vivado Simulator进行仿真,确保Verilog代码符合预期行为。 8. **综合与实现**:将Verilog代码转换为具体的逻辑门电路,然后映射到FPGA的物理资源上,这通常由Synopsys的VHDL/Verilog Synthesis工具或Xilinx的Vivado完成。 9. **时序分析**:检查设计满足时序约束,如最大时钟周期和建立时间,以确保其在实际运行中正确无误。 10. **硬件调试**:使用JTAG或其它调试接口,可以对运行在FPGA上的SRAM逻辑进行实时观察和调试。 "sram.zip"和"sram_ctl.zip"文件包可能包含了实现FPGA中SRAM存储块及其控制器的Verilog代码。通过理解上述关键知识点,开发者可以有效地设计和优化自己的FPGA SRAM模块。"S6R80xxx1A_rev1.0.pdf"可能是SRAM芯片的数据手册,提供具体的电气特性、引脚配置和操作指南,这对于硬件设计和集成至关重要。

sram.zip (2个子文件)

sram.zip (2个子文件)  S6R80xxx1A_rev1.0.pdf 1.69MB

S6R80xxx1A_rev1.0.pdf 1.69MB sram_ctl.zip 6KB

sram_ctl.zip 6KB- 1

- 粉丝: 131

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论1