256

256

256

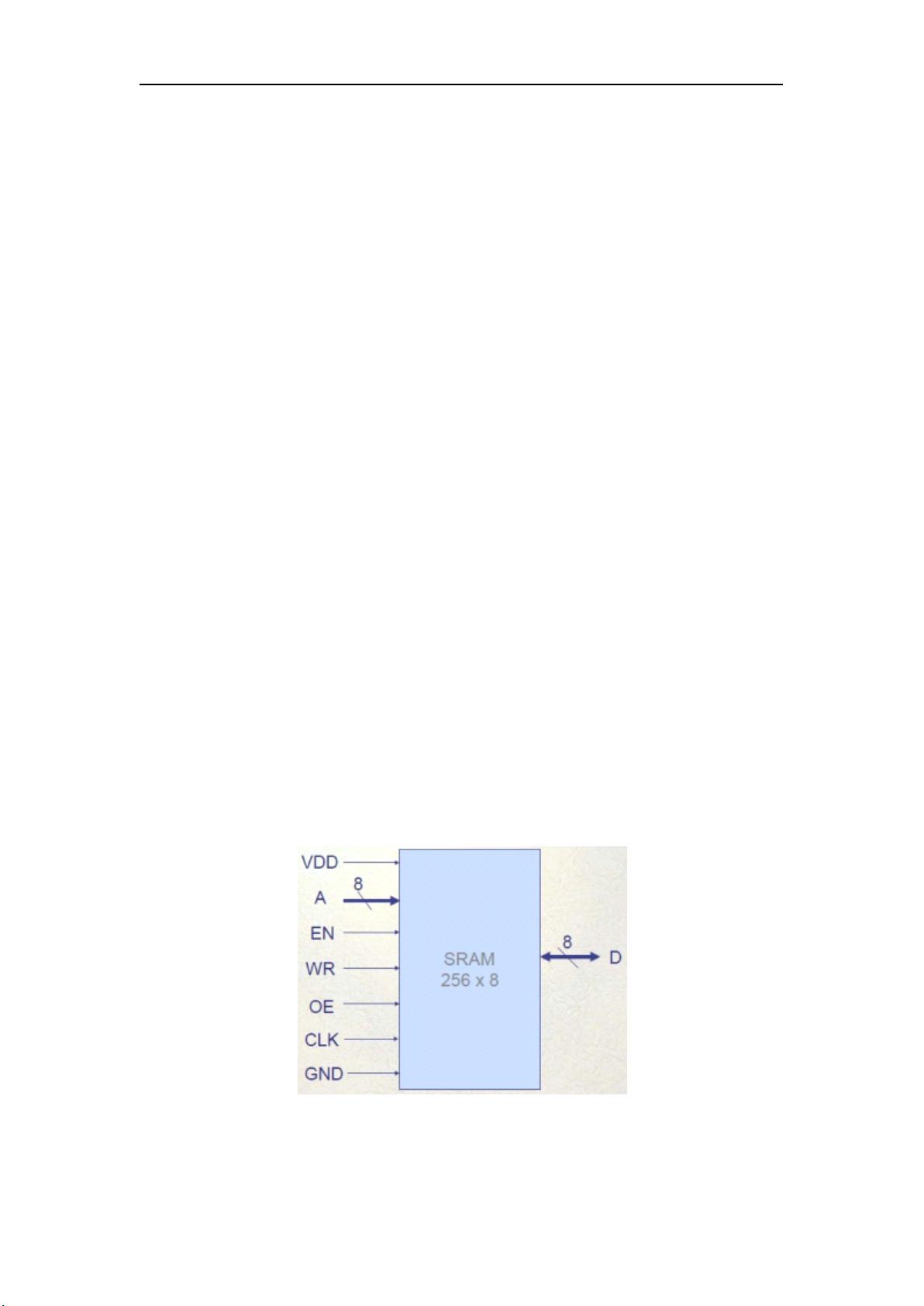

256 × 8

8

8

8 SSRAM

SSRAM

SSRAM

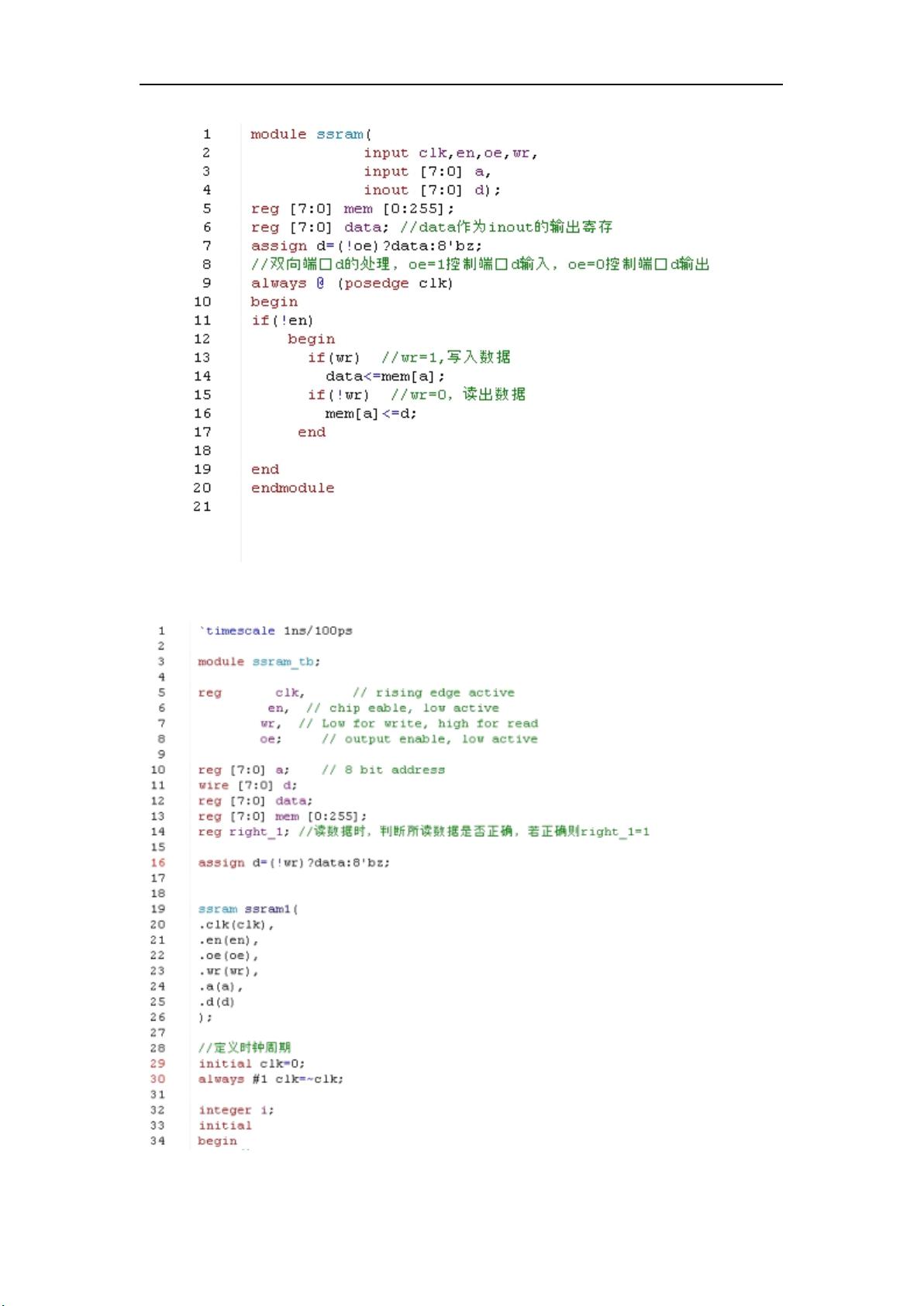

SSRAM 的 设计、仿真与综合

一、摘要

用 Verilog HDL 语言描述 一个 256 ×

8

的 SSRAM ,在 modesim 中仿

真,最后在

D

esign Vision 中综合。

二、概叙

SSRAM 是 synchronous static random access memory 的缩

写 , 即同步静态随机存取存储器 。 同步是指 Memory 工作需要步时钟

,

内部的命令的发送与数据的传输都以它为基准 ; 随机是指数据不是线

性依次存储,而是由指定地址进行数据读写。

对于 SSRAM 的所有访问都在时钟的上升 / 下降沿启动 。 地址 、 数据

输入和其它控制信号均和时钟信号相关。这一点与异步 SRAM 不同 , 异

步 SRAM 的访问独立于时钟,数据输入和输出都由地址的变化控制。

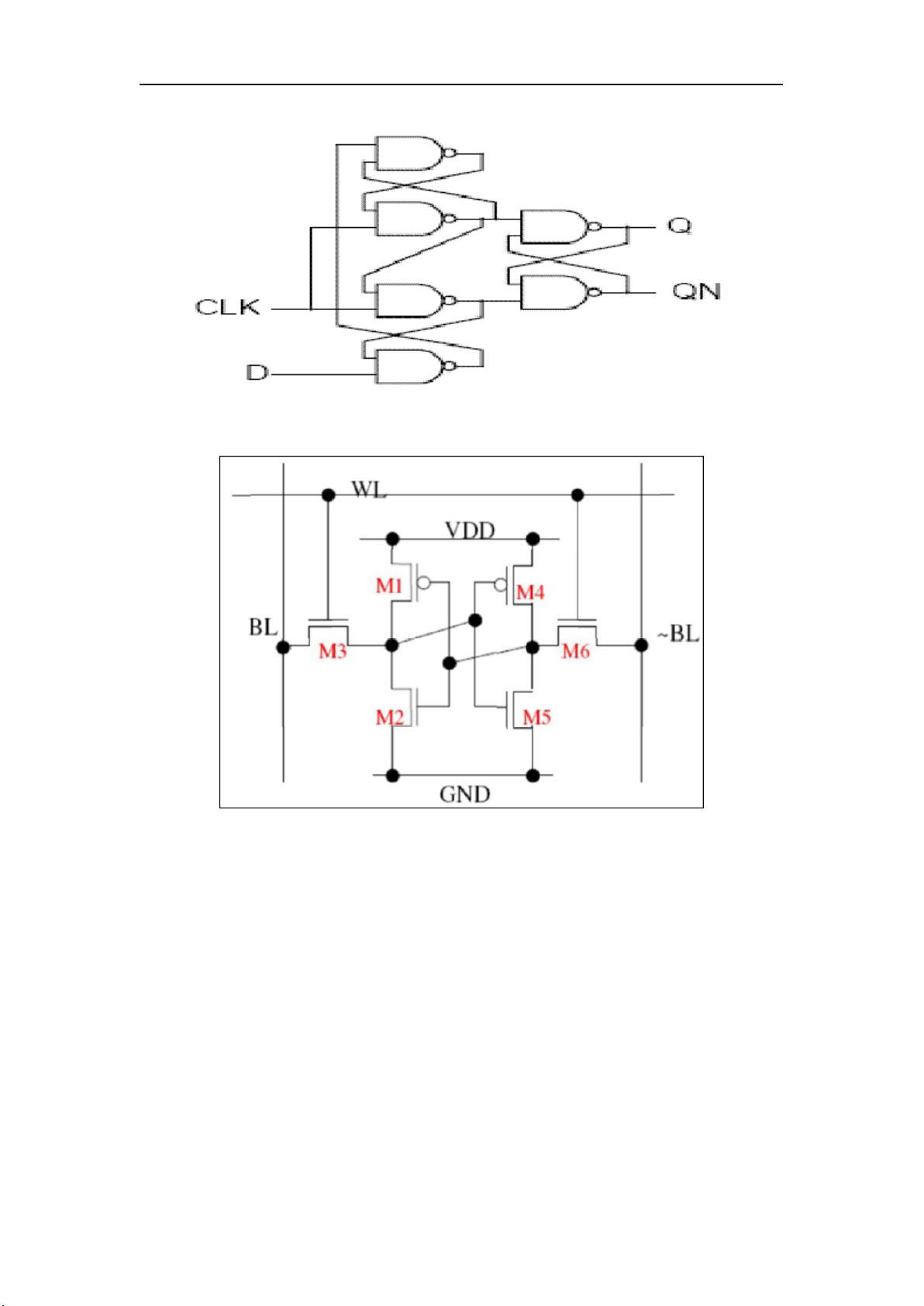

SSRAM 一般采用 4T 或 6T 结构 , 用锁存器存储数据 , SSRAM 的外观

引脚以及内部结构如下图所示:

图一 SSRAM 外观