UART.rar_uart_uart transmitter

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

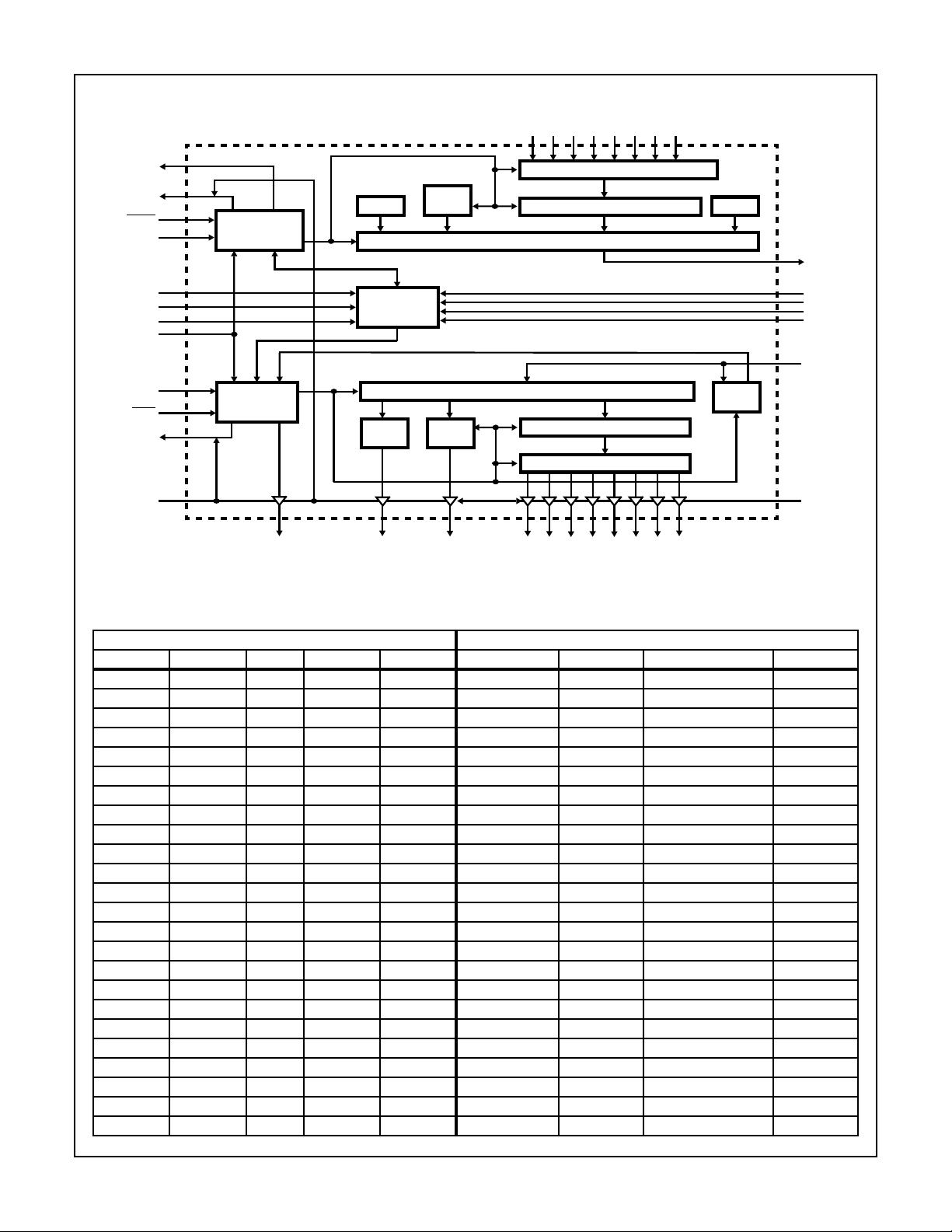

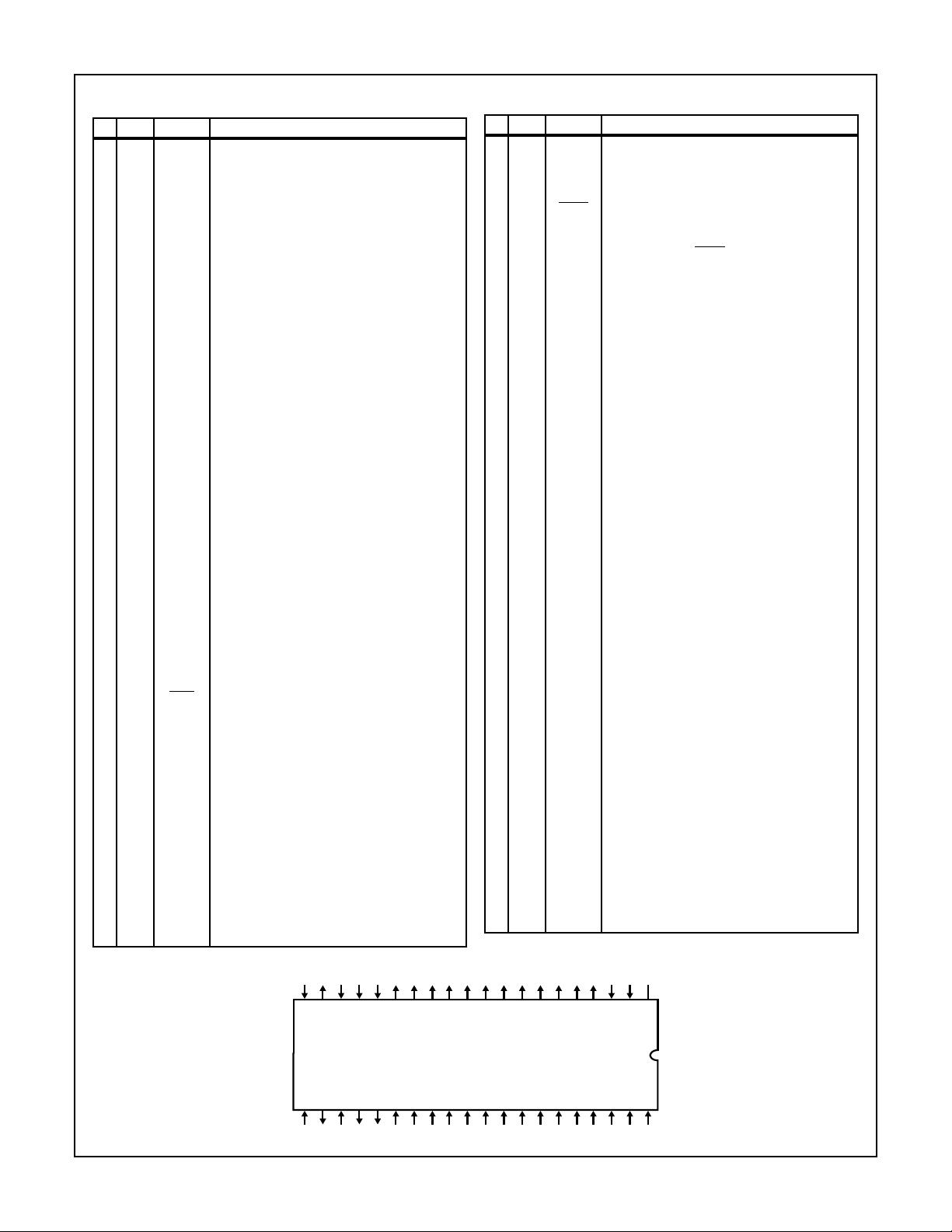

UART(通用异步收发传输器)是一种广泛用于嵌入式系统和计算机硬件中的串行通信接口,允许设备之间以单向或双向方式进行数据传输。UART接口在许多电子设备中都发挥着重要作用,如微控制器、传感器、PC扩展卡等。在本教程中,我们将深入探讨UART的工作原理、配置以及如何实现UART接收器和发射器。 UART的基本工作原理: UART通过串行通信方式传输数据,一次传输一个比特位。它包含两个主要部分:发送器和接收器。发送器将并行数据转换为串行流,而接收器则执行相反的操作。UART传输数据时通常使用起始位、数据位、奇偶校验位和停止位的格式,确保正确接收。例如,常见的8N1配置表示8位数据位、无校验位和1位停止位。 UART配置: 配置UART涉及以下几个关键参数: 1. 波特率:决定数据传输速率,即每秒传输的比特位数。可以通过调整内部分频器来设定。 2. 数据位:通常为7位、8位或9位,决定每次传输的数据量。 3. 奇偶校验:可选设置,用于检测传输错误。奇偶校验位使数据位中的“1”数量为奇数或偶数。 4. 停止位:在数据传输结束时添加的静默位,通常为1位或2位,用于提供接收器的同步。 UART接收器和发射器: 在UART接收器中,设备监听串行线路上的信号,一旦检测到起始位,就开始收集数据位。接收到所有数据位后,根据配置检查奇偶校验,然后等待下一个起始位。如果检测到错误,接收器可能触发中断,通知处理器进行处理。 UART发射器的工作则相反,它会将待发送的数据按顺序排列,并根据配置添加起始位、奇偶校验位和停止位。然后,这些串行数据会被发送到UART接口的TX引脚,通过连接的线路传送到接收端。 在实际项目中,通常使用微控制器的内置UART模块,通过编程设置上述参数,并实现数据的发送和接收。"Complete Projects"这个文件可能包含了一些示例代码或完整的UART通信项目,可以帮助你理解和实践UART接口的使用。 为了实现UART通信,你需要编写以下步骤的代码: 1. 初始化UART:设置波特率、数据位、奇偶校验和停止位。 2. 编写发送函数:将要发送的数据转换为串行格式,并通过UART发射器发送。 3. 编写接收中断服务程序:当接收到数据时,处理数据并存储到适当的位置。 4. 错误检测与处理:检查接收到的数据是否正确,如发现错误,采取相应措施。 通过学习和实践,你将能够熟练地在你的项目中集成和利用UART通信,提高设备之间的数据交换效率和可靠性。

UART.rar (20个子文件)

UART.rar (20个子文件)  Complete Projects

Complete Projects  T3_syn.gif 17KB

T3_syn.gif 17KB TB3_transmitter.vhd 2KB

TB3_transmitter.vhd 2KB T2_syn.gif 17KB

T2_syn.gif 17KB UART_sim.gif 29KB

UART_sim.gif 29KB R3_syn.gif 23KB

R3_syn.gif 23KB Recei_model.vhd 9KB

Recei_model.vhd 9KB TB2_transmitter.vhd 2KB

TB2_transmitter.vhd 2KB TB2_receiver.vhd 2KB

TB2_receiver.vhd 2KB TB1_receiver.vhd 2KB

TB1_receiver.vhd 2KB R1_syn.gif 21KB

R1_syn.gif 21KB T1_syn.gif 15KB

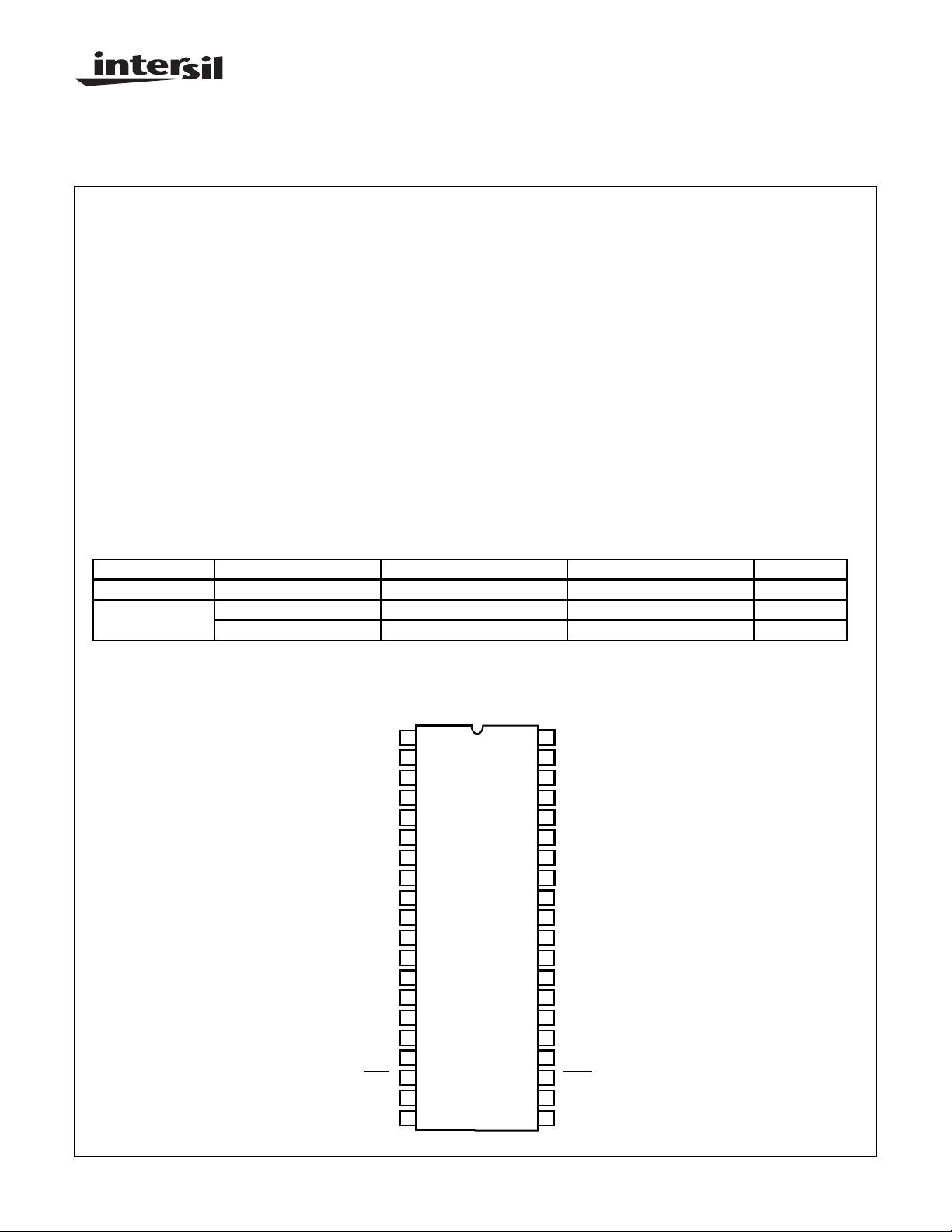

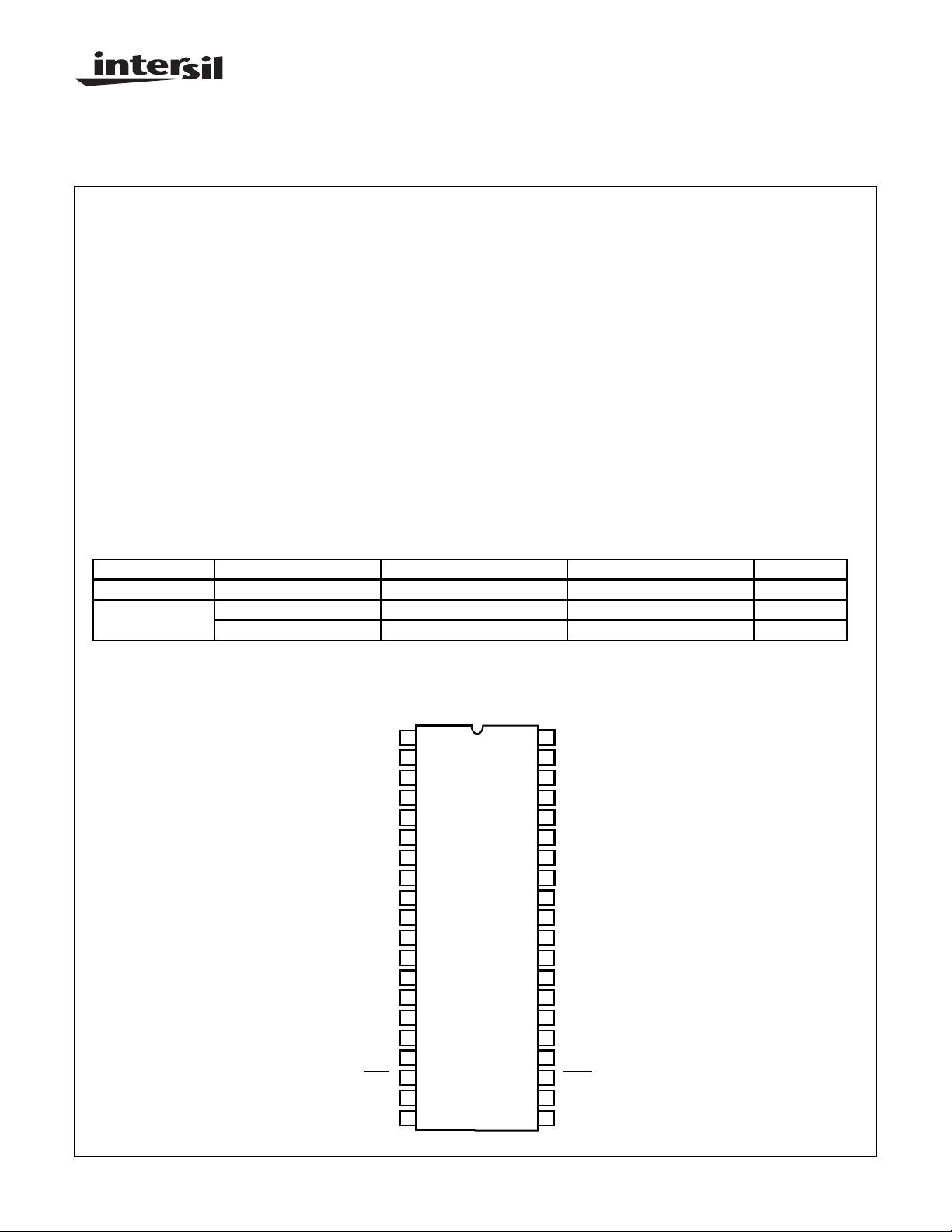

T1_syn.gif 15KB UART_6402.vhd 19KB

UART_6402.vhd 19KB UART6402.pdf 40KB

UART6402.pdf 40KB TB3_receiver.vhd 2KB

TB3_receiver.vhd 2KB TB_UART.vhd 3KB

TB_UART.vhd 3KB trans_gate.vhd 27KB

trans_gate.vhd 27KB TB1_transmitter.vhd 2KB

TB1_transmitter.vhd 2KB Trans_model.vhd 8KB

Trans_model.vhd 8KB R2_syn.gif 21KB

R2_syn.gif 21KB UART_gate.vhd 54KB

UART_gate.vhd 54KB- 1

- 粉丝: 97

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 白色大气风格响应式游戏应用商店企业网站模板.zip

- 白色大气风格响应式运动健身瑜伽企业网站模板.zip

- 白色大气风格响应式左栏产品展示企业网站模板.zip

- 白色大气简洁的整站企业网站模板下载.rar

- 白色大气简洁的汽车配件商城整站网站模板下载.zip

- 白色大气简洁的时装模特企业网站模板下载.zip

- 白色大气简洁风的商务企业网站模板下载.zip

- 白色大气精致的产品数据企业网站模板下载.zip

- 白色淡雅风的商务企业网站模板下载.zip

- 白色调简洁的咨询公司整站模板下载.zip

- 白色非常简洁的商务网站模板下载.zip

- 白色风格的bootstrap响应式网站IT软件公司模板下载.zip

- 白色风格的工业网站模板下载.rar

- 白色风格的包包品牌商城模板下载.rar

- 白色风格的个人简历整站模板下载.rar

- 白色风格的广告设计公司网站模板下载.rar

信息提交成功

信息提交成功