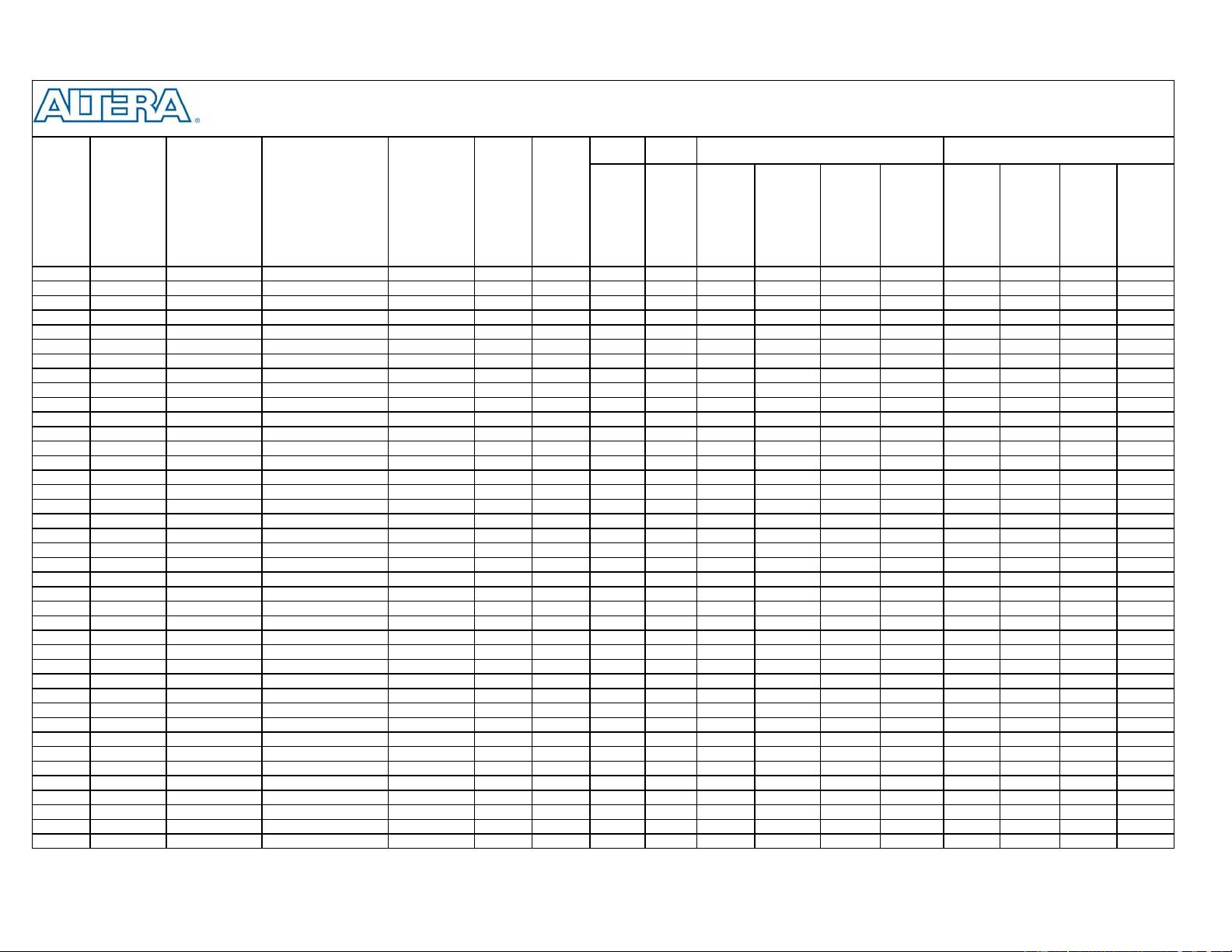

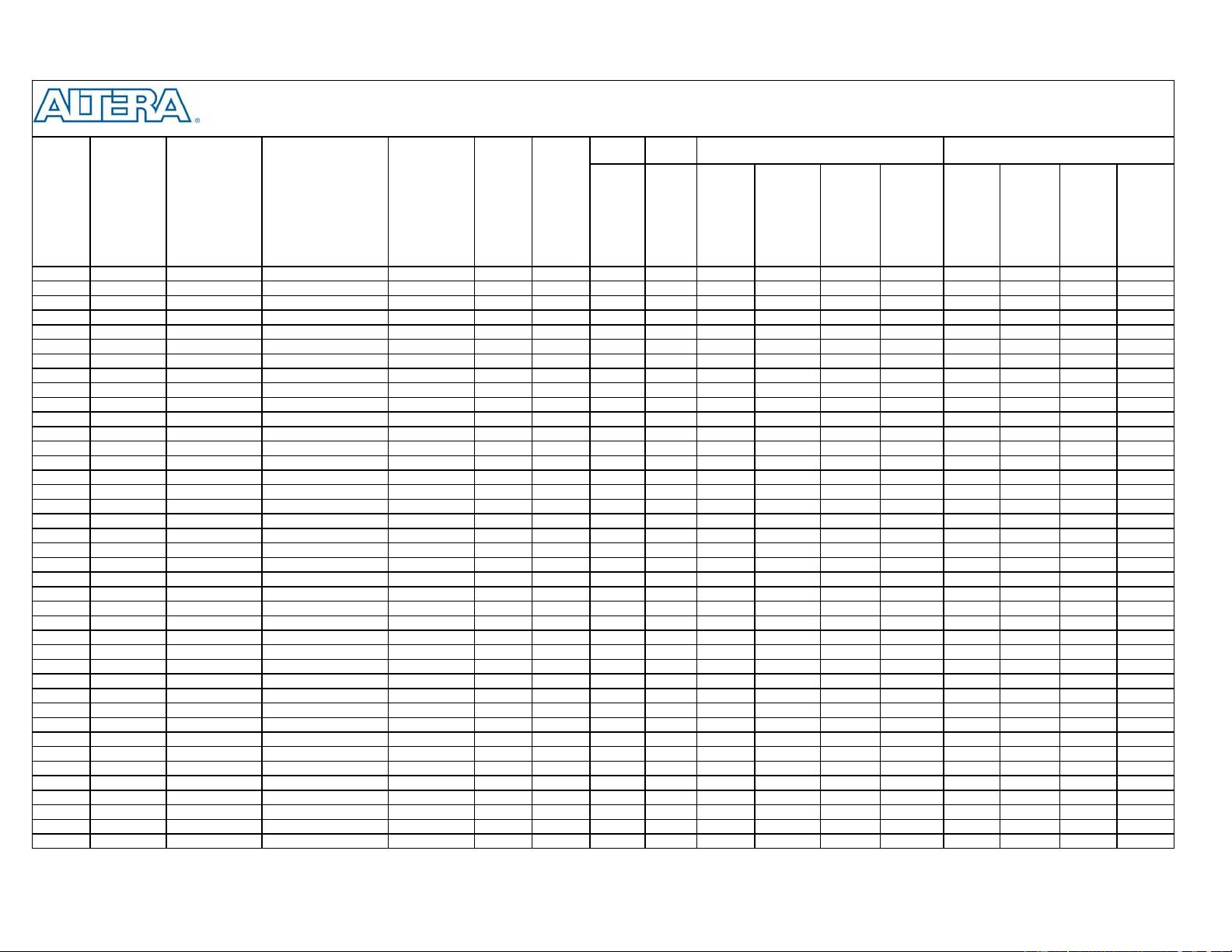

标题中的"EP2S30.rar_EP2S30_atomico78_datasheet_fpga"表明这是一份关于EP2S30 FPGA的详细资料,其中可能包含了与Atomico78设计相关的数据手册。"EP2S30"是Altera公司(现已被Intel收购)的Stratix II系列的一款 FPGA 芯片。"FPGA"代表Field Programmable Gate Array,即现场可编程门阵列,是一种高度灵活的集成电路,允许用户根据需求定制逻辑功能。 在描述中提到的"EP2S30资料,FPGA编程,适用于EP2S30芯片",意味着这个压缩包包含的信息主要涉及如何对EP2S30 FPGA进行编程和配置。FPGA编程通常包括硬件描述语言(如VHDL或Verilog)的设计、逻辑综合、布局布线、时序分析以及配置文件的生成。 标签"ep2s30 atomico78 datasheet fpga"进一步确认了内容的重点,"datasheet"是指器件的数据手册,它是工程师理解和使用芯片的关键参考资料,通常包括芯片的功能描述、电气特性、封装信息、引脚配置、性能参数等。"atomico78"可能是某种特定设计实例或者与EP2S30相关的开发板或项目名称。 压缩包内的"EP2S30.pdf"很可能就是EP2S30 FPGA的官方数据手册。这份PDF文档通常会包含以下内容: 1. **产品概述**:介绍EP2S30的基本特性和优势,比如逻辑单元数量、I/O端口、嵌入式存储器资源、时钟管理模块等。 2. **功能特性**:详述EP2S30的各种内置功能模块,如乘法器、分布式RAM、PLL(锁相环)和IOB(输入/输出块)。 3. **逻辑资源**:阐述LUT(查找表)、触发器和其他逻辑元件的可用性和用法。 4. **I/O特性**:描述EP2S30的输入输出能力,包括各种I/O标准(LVCMOS、LVDS等)、速度等级和驱动强度选择。 5. **功耗和热特性**:提供静态和动态功耗数据,以及散热指导。 6. **配置选项**:介绍如何对EP2S30进行配置,包括JTAG、SRAM、SPI等多种方式。 7. **设计工具支持**:说明使用Altera Quartus II等软件进行设计和实现的步骤和注意事项。 8. **应用示例**:可能包含Atomico78设计的相关实例,帮助用户理解如何在实际项目中应用EP2S30。 9. **电气特性**:列出各引脚的电压、电流规格,以及工作范围。 10. **封装和物理尺寸**:提供芯片封装图和尺寸,便于PCB布局设计。 通过这份资料,电子工程师和设计师可以全面了解EP2S30 FPGA的性能,并学习如何利用它来实现各种复杂的数字逻辑设计。对于初学者来说,数据手册是学习FPGA基础知识和实践操作的重要资源;而对于经验丰富的开发者,它则提供了验证设计和解决故障的关键信息。

EP2S30.rar (1个子文件)

EP2S30.rar (1个子文件)  EP2S30.pdf 395KB

EP2S30.pdf 395KB- 1

- 粉丝: 77

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 工作流-OA-低代码表单的 前端工程,基于 Activiti7 Vue3 TS ElementPlus Vite,支持三种布局

- 软考冲刺:计算机技术与软件专业技术资格基础教程

- 泰迪杯数据技能大赛题目word版

- experiment-demo.zip

- HarmonyOs实战项目=>App首页架构沉浸式效果

- 课程考试系统开发基础教程

- 已测价值299元最新升级版Xiuno Light(修罗·轻鸿)v3.3 - 修罗论坛程序主题

- Delphi XE 10.3 Demo 文件

- 基于SpringBoot + Vue3 + TypeScript + Vite的个人前后端分离博客

- H5幸运刮刮乐抽奖 免公众号+直运营

信息提交成功

信息提交成功