74ls107.zip_74ls107_K.

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

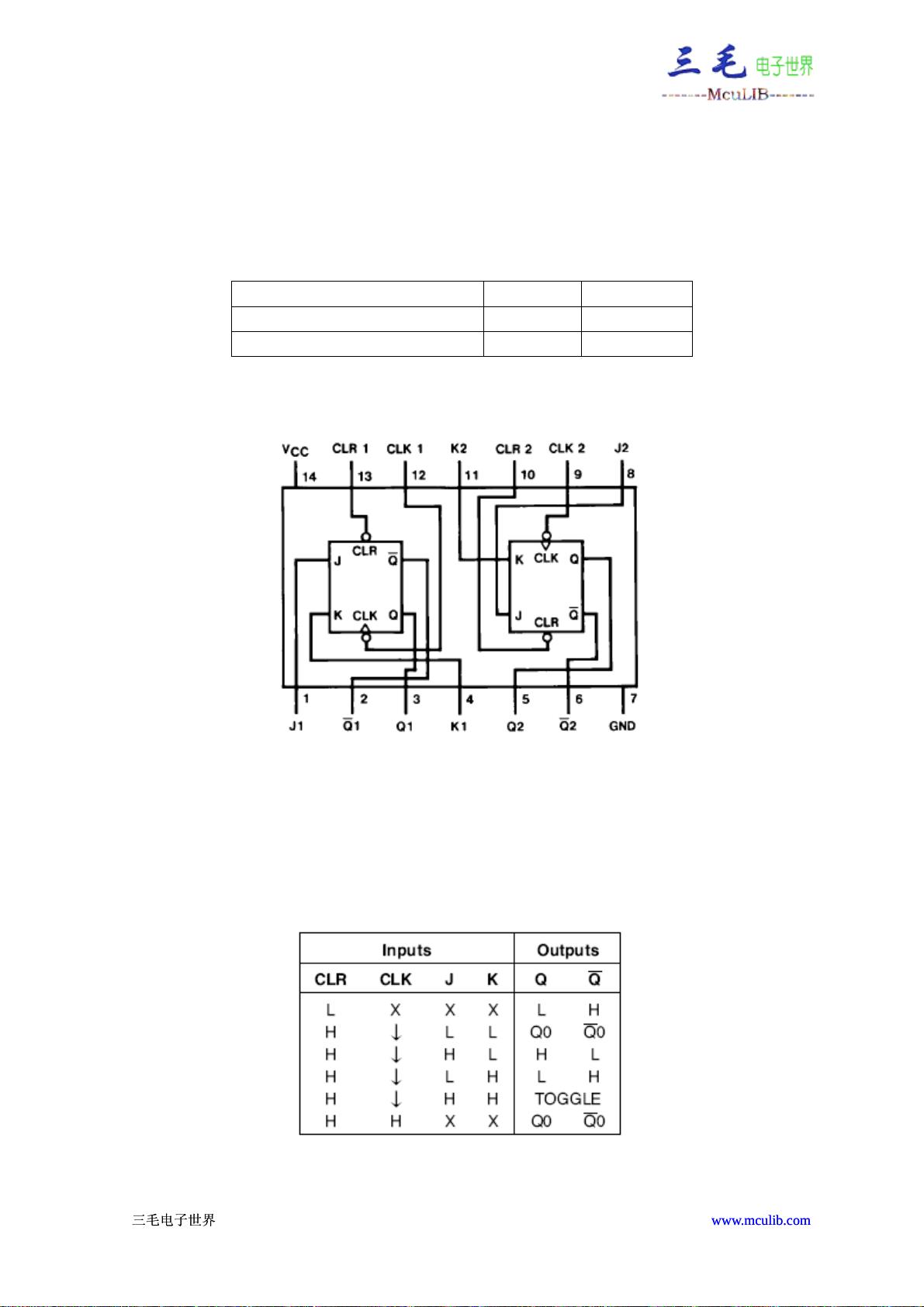

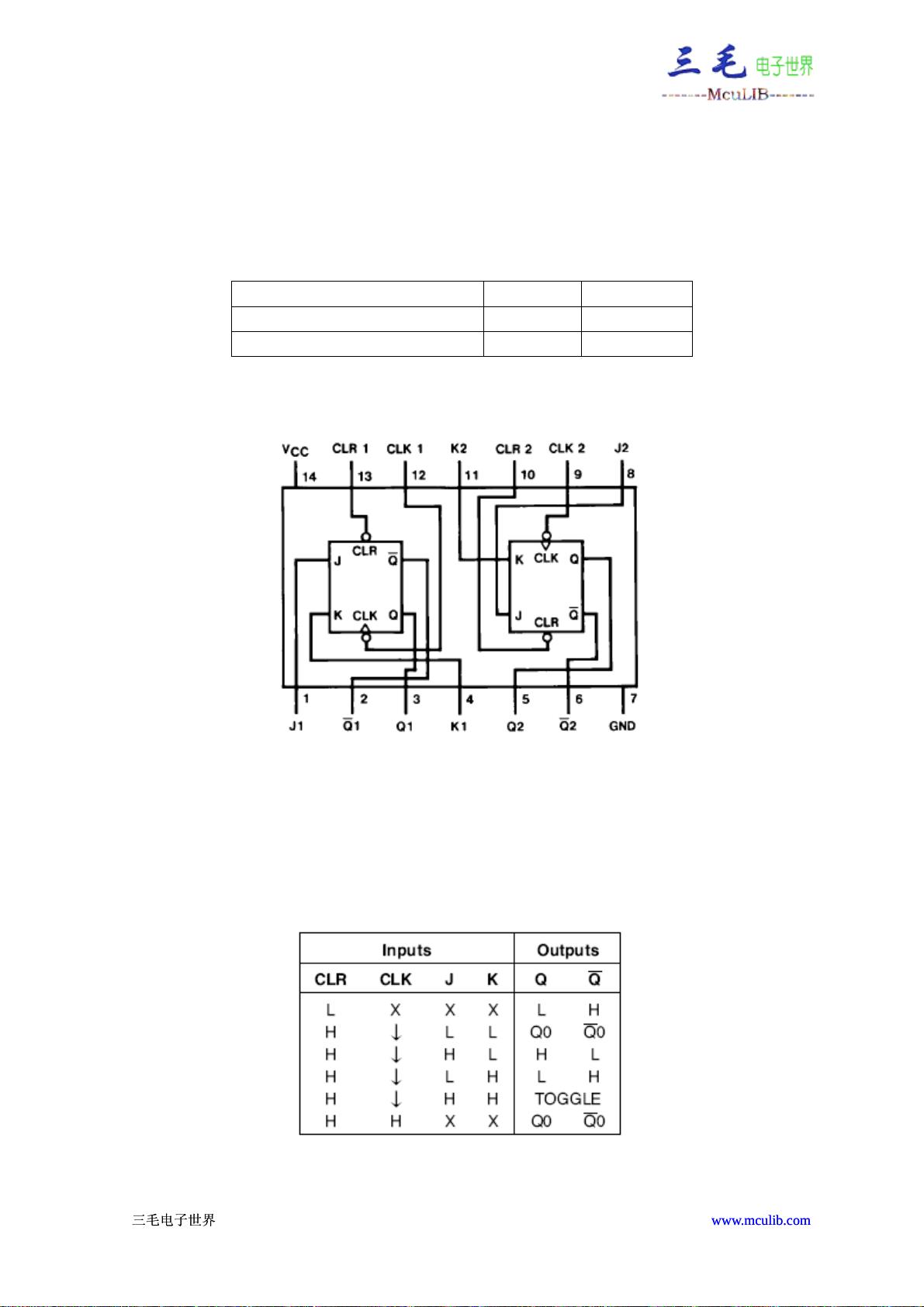

74LS107是一款经典的数字集成电路,属于74系列逻辑器件之一,主要功能是作为带清除端的两组J-K触发器。这个芯片在电路设计中被广泛应用于时序逻辑电路,数据处理和信号控制等领域。74LS107的"LS"代表低功耗肖特基(Low Power Schottky),它具有速度快、功耗低的特点,适用于对速度和能耗有较高要求的系统。 我们来了解下J-K触发器的基本概念。J-K触发器是一种双稳态电路,有两个互补的输出端Q和Q',以及输入端J(Set)、K(Reset)和一个时钟脉冲输入端CP。J和K输入的组合决定了触发器状态的变化。当J=1,K=0时,触发器执行置1操作;当J=0,K=1时,执行置0操作;如果J=K=1,触发器会在时钟脉冲到来时翻转其状态,这种操作被称为“toggle”或“无条件翻转”。 74LS107包含两组独立的J-K触发器,每组都有自己的清除(CLR)输入端。清除端的作用是当其接收到低电平时,无论其他输入如何,都会使触发器回到确定的初始状态,即Q=0,Q'=1。这种特性使得74LS107在系统复位或者初始化时能快速稳定到预设状态。 74LS107中的“主从结构”意味着在时钟脉冲CP的上升沿期间,输入信号先被存储在主触发器中,然后在下降沿传递到从触发器,这样可以确保在时钟边沿瞬间,输入不会发生变化,避免了由于输入变化导致的错误翻转。54/74107和54/74LS107之间的区别在于触发方式:54/74107是主从触发,而54/74LS107是下降沿触发,这意味着后者只在时钟脉冲的下降沿改变状态。 在实际应用中,74LS107可以用于构建计数器、移位寄存器、分频器等。例如,通过连接多个74LS107并利用它们的输出反馈到输入,可以构建任意进制的计数器。此外,还可以与其它逻辑门组合,实现更复杂的逻辑功能。 了解74LS107的内部工作原理和操作模式对于电子工程师来说非常重要,特别是在设计数字电路时。通过阅读74ls107.pdf文档,你可以深入理解该芯片的电气特性、引脚功能、真值表以及应用示例。这份文档通常会包含详细的电路图、逻辑符号、电气特性表格以及使用注意事项,帮助你更好地在实际项目中应用74LS107。 74LS107是一款实用的数字逻辑器件,尤其适合需要高速、低功耗、精确时序控制的场合。掌握其工作原理和使用方法,将有助于你设计出更高效、可靠的电子系统。

74ls107.zip (1个子文件)

74ls107.zip (1个子文件)  74ls107.pdf 145KB

74ls107.pdf 145KB- 1

- 粉丝: 79

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 生菜生长记录数据集(3K+ 记录,7特征) CSV

- 国际象棋检测2-YOLO(v5至v9)、COCO、CreateML、Darknet、Paligemma、TFRecord数据集合集.rar

- RGMII delay问题

- Python结合Pygame库实现圣诞主题动画和音乐效果的代码示例

- 国际象棋检测2-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- ssd5课件图片记录保存

- 常用算法介绍与学习资源汇总

- Python与Pygame实现带特效的圣诞节场景模拟程序

- 国际象棋检测11-YOLO(v7至v9)、COCO、Darknet、Paligemma、VOC数据集合集.rar

- 使用Python和matplotlib库绘制爱心图形的技术教程

信息提交成功

信息提交成功