Document Number: 001-94240 Rev. *D Page 4 of 22

Overview

The CY15B104Q is a serial F-RAM memory. The memory array

is logically organized as 524,288 × 8 bits and is accessed using

an industry-standard serial peripheral interface (SPI) bus. The

functional operation of the F-RAM is similar to serial flash and

serial EEPROMs. The major difference between the

CY15B104Q and a serial flash or EEPROM with the same pinout

is the F-RAM's superior write performance, high endurance, and

low power consumption.

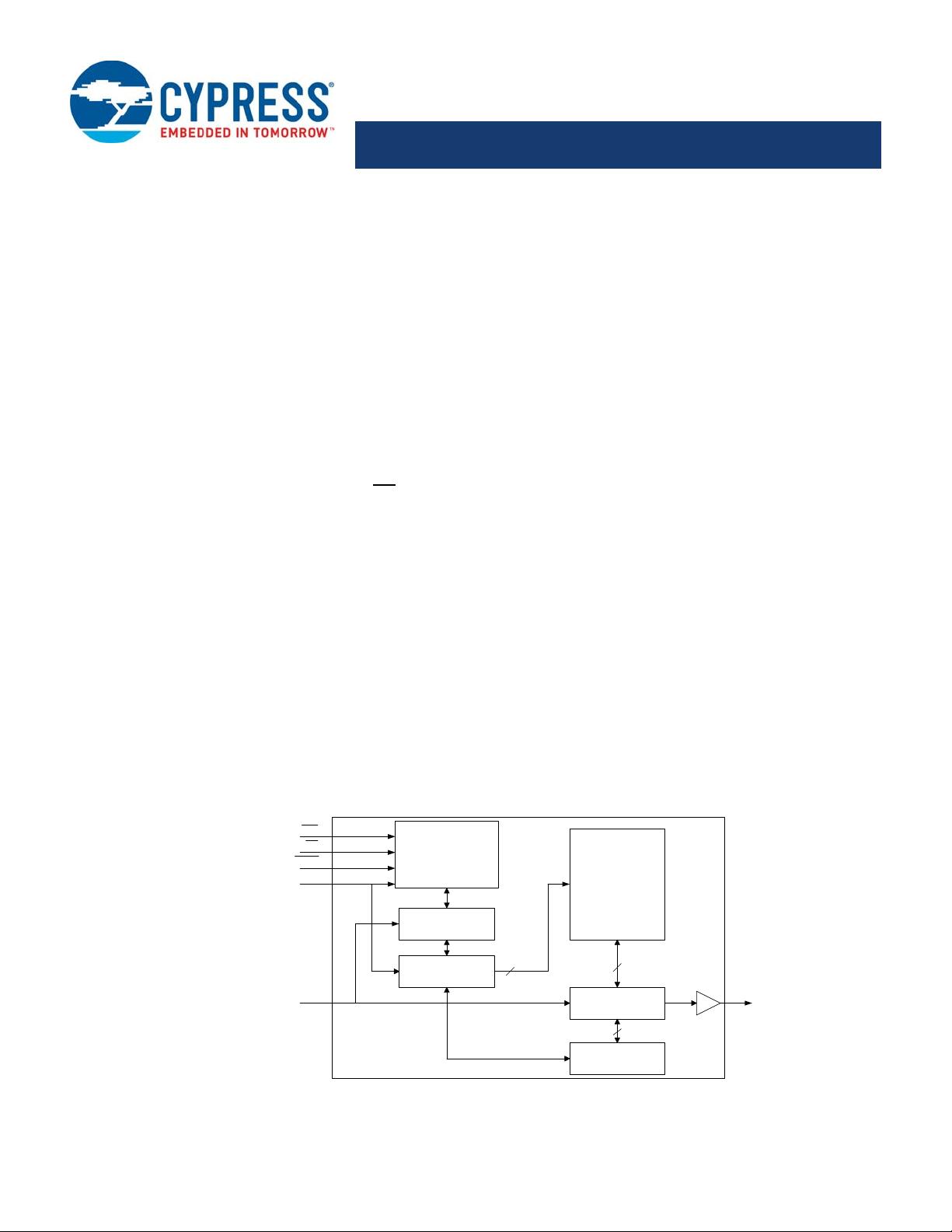

Memory Architecture

When accessing the CY15B104Q, the user addresses 512K

locations of eight data bits each. These eight data bits are shifted

in or out serially. The addresses are accessed using the SPI

protocol, which includes a chip select (to permit multiple devices

on the bus), an opcode, and a three-byte address. The upper 5

bits of the address range are 'don't care' values. The complete

address of 19 bits specifies each byte address uniquely.

Most functions of the CY15B104Q are either controlled by the

SPI interface or handled by on-board circuitry. The access time

for the memory operation is essentially zero, beyond the time

needed for the serial protocol. That is, the memory is read or

written at the speed of the SPI bus. Unlike a serial flash or

EEPROM, it is not necessary to poll the device for a ready

condition because writes occur at bus speed. By the time a new

bus transaction can be shifted into the device, a write operation

is complete. This is explained in more detail in the interface

section.

Serial Peripheral Interface (SPI) Bus

The CY15B104Q is an SPI slave device and operates at speeds

up to 40 MHz. This high-speed serial bus provides high-perfor-

mance serial communication to an SPI master. Many common

microcontrollers have hardware SPI ports allowing a direct

interface. It is simple to emulate the port using ordinary port pins

for microcontrollers that do not. The CY15B104Q operates in SPI

Mode 0 and 3.

SPI Overview

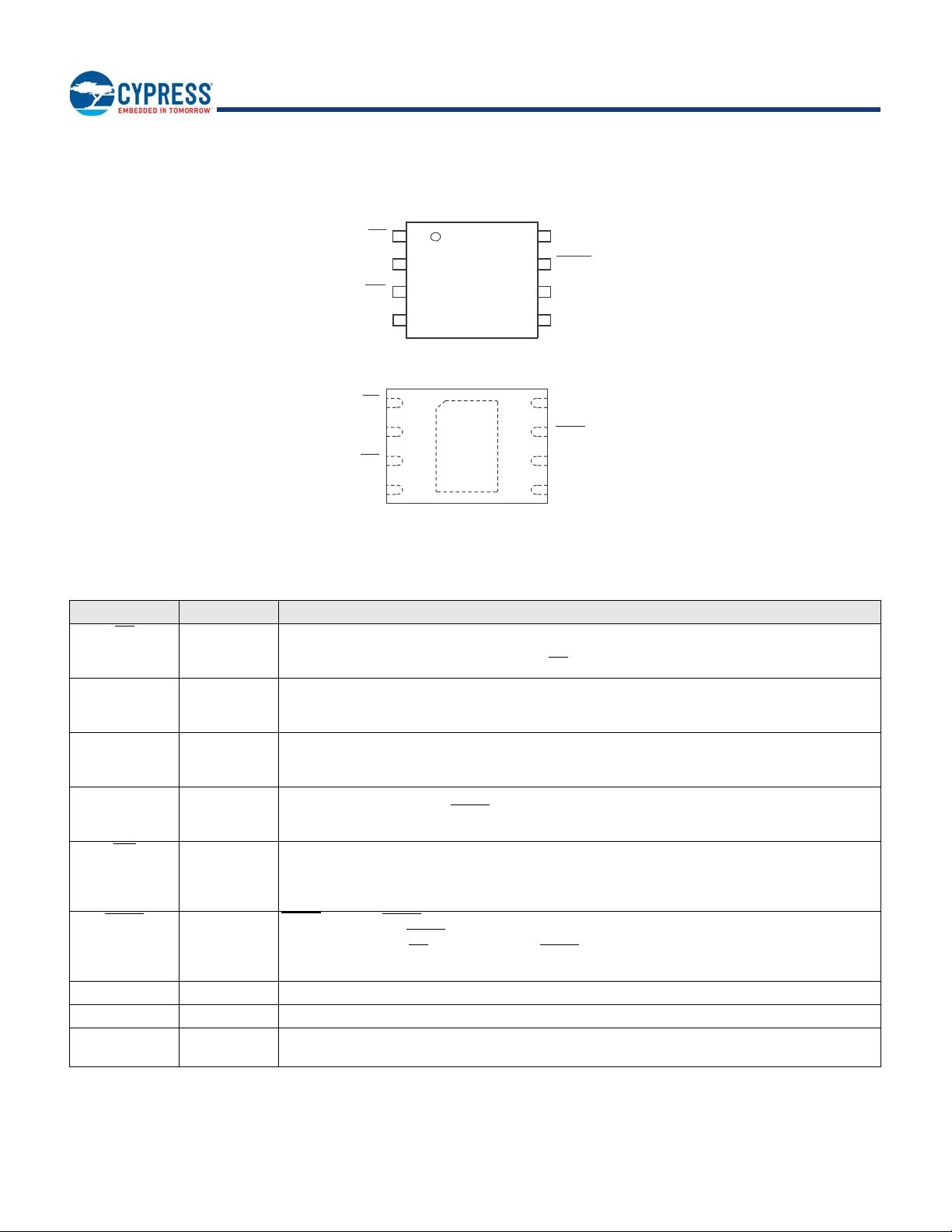

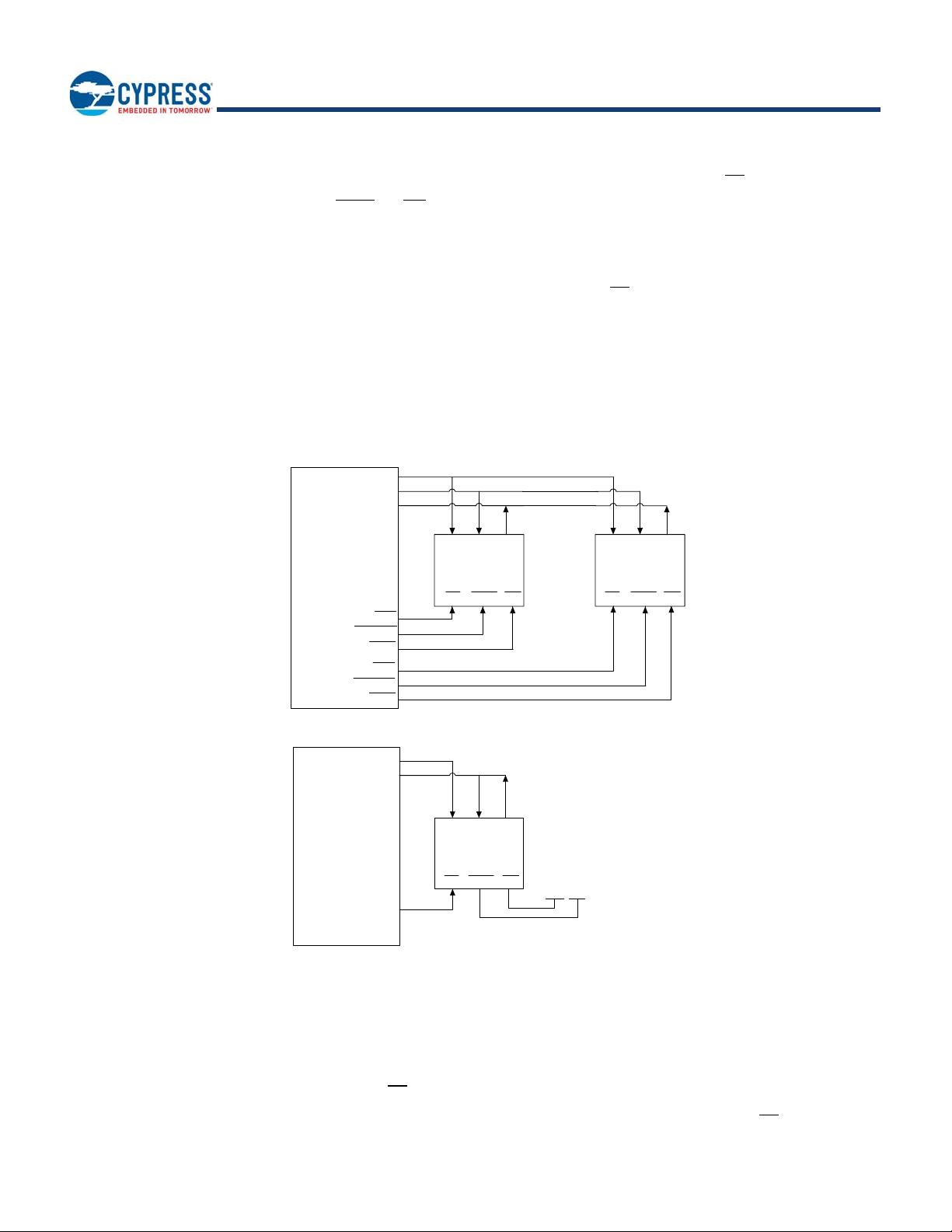

The SPI is a four-pin interface with Chip Select (CS), Serial Input

(SI), Serial Output (SO), and Serial Clock (SCK) pins.

The SPI is a synchronous serial interface, which uses clock and

data pins for memory access and supports multiple devices on

the data bus. A device on the SPI bus is activated using the CS

pin.

The relationship between chip select, clock, and data is dictated

by the SPI mode. This device supports SPI modes 0 and 3. In

both of these modes, data is clocked into the F-RAM on the rising

edge of SCK starting from the first rising edge after CS

goes

active.

The SPI protocol is controlled by opcodes. These opcodes

specify the commands from the bus master to the slave device.

After CS

is activated, the first byte transferred from the bus

master is the opcode. Following the opcode, any addresses and

data are then transferred. The CS

must go inactive after an

operation is complete and before a new opcode can be issued.

The commonly used terms in the SPI protocol are as follows:

SPI Master

The SPI master device controls the operations on the SPI bus.

An SPI bus may have only one master with one or more slave

devices. All the slaves share the same SPI bus lines and the

master may select any of the slave devices using the CS

pin. All

of the operations must be initiated by the master activating a

slave device by pulling the CS

pin of the slave LOW. The master

also generates the SCK and all the data transmission on SI and

SO lines are synchronized with this clock.

SPI Slave

The SPI slave device is activated by the master through the Chip

Select line. A slave device gets the SCK as an input from the SPI

master and all the communication is synchronized with this

clock. An SPI slave never initiates a communication on the SPI

bus and acts only on the instruction from the master.

The CY15B104Q operates as an SPI slave and may share the

SPI bus with other SPI slave devices.

Chip Select (CS

)

To select any slave device, the master needs to pull down the

corresponding CS

pin. Any instruction can be issued to a slave

device only while the CS

pin is LOW. When the device is not

selected, data through the SI pin is ignored and the serial output

pin (SO) remains in a high-impedance state.

Note A new instruction must begin with the falling edge of CS

.

Therefore, only one opcode can be issued for each active Chip

Select cycle.

Serial Clock (SCK)

The serial clock is generated by the SPI master and the commu-

nication is synchronized with this clock after CS

goes LOW.

The CY15B104Q enables SPI modes 0 and 3 for data commu-

nication. In both of these modes, the inputs are latched by the

slave device on the rising edge of SCK and outputs are issued

on the falling edge. Therefore, the first rising edge of SCK

signifies the arrival of the first Most Significant Bit (MSB) of an

SPI instruction on the SI pin. Further, all data inputs and outputs

are synchronized with SCK.

Data Transmission (SI/SO)

The SPI data bus consists of two lines, SI and SO, for serial data

communication. SI is also referred to as Master Out Slave In

(MOSI) and SO is referred to as Master In Slave Out (MISO). The

master issues instructions to the slave through the SI pin, while

the slave responds through the SO pin. Multiple slave devices

may share the SI and SO lines as described earlier.

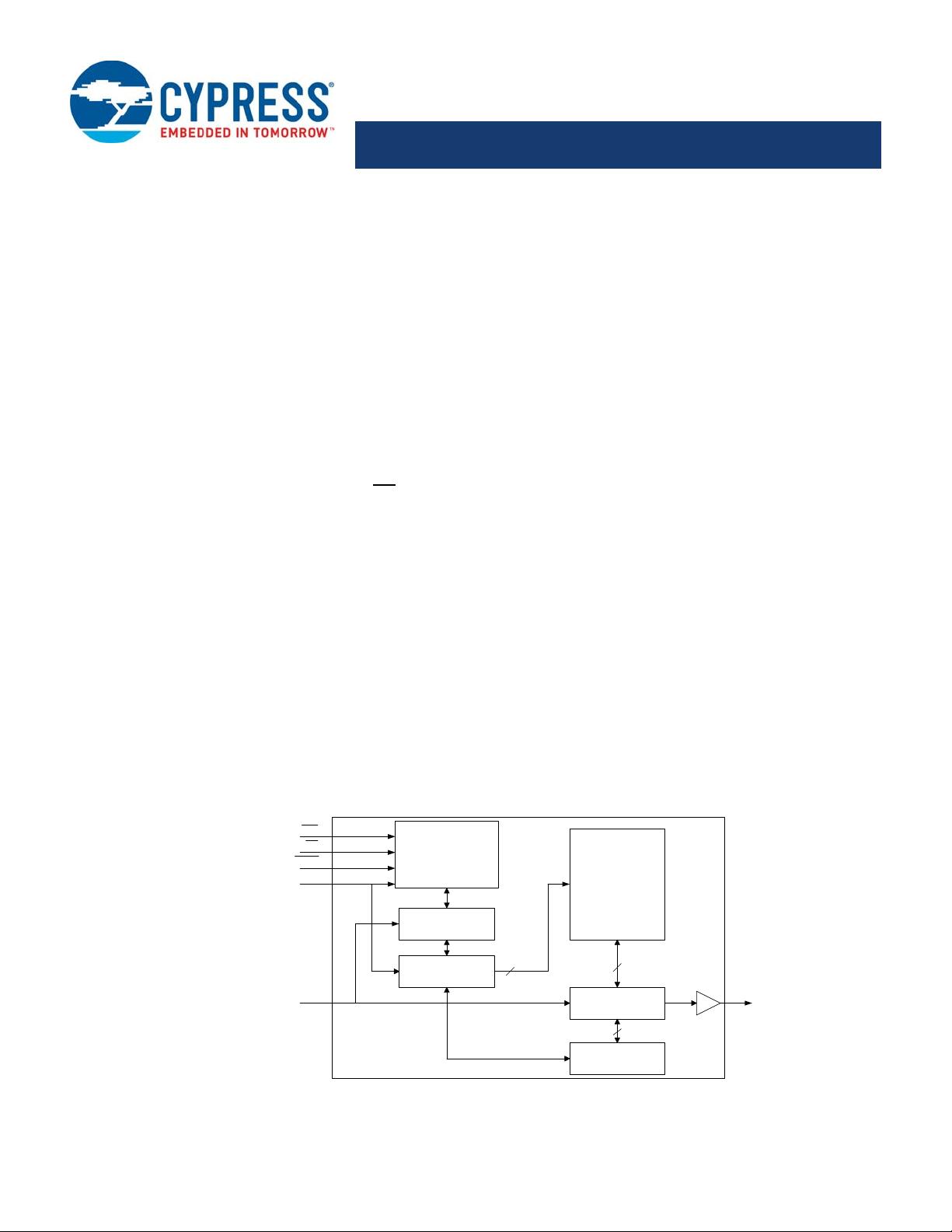

The CY15B104Q has two separate pins for SI and SO, which can

be connected with the master as shown in Figure 3.

CY15B104Q.zip (1个子文件)

CY15B104Q.zip (1个子文件)  CY15B104Q.pdf 743KB

CY15B104Q.pdf 743KB

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功