uart.rar_UART VHDL_基于FPGA的UART

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

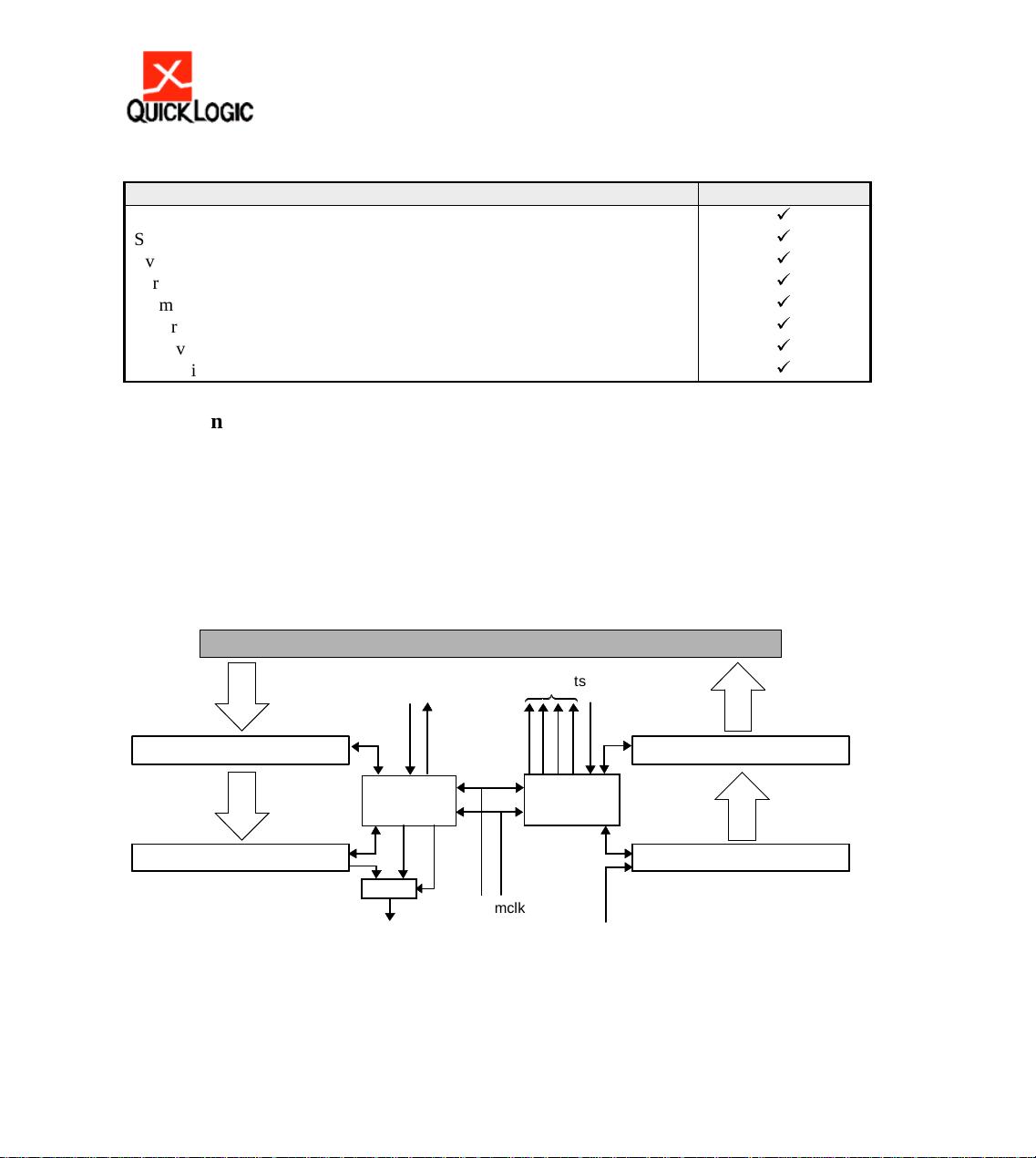

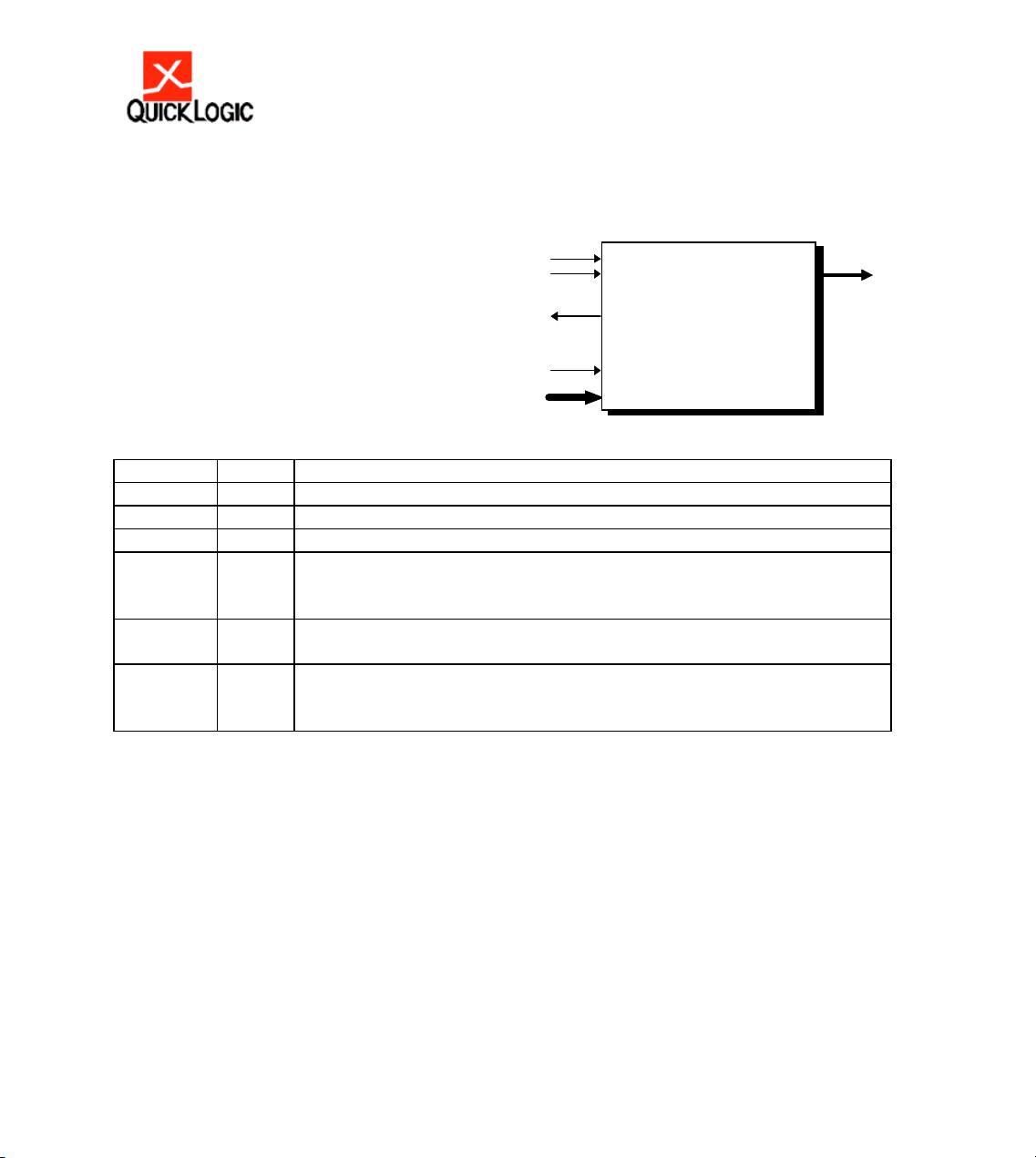

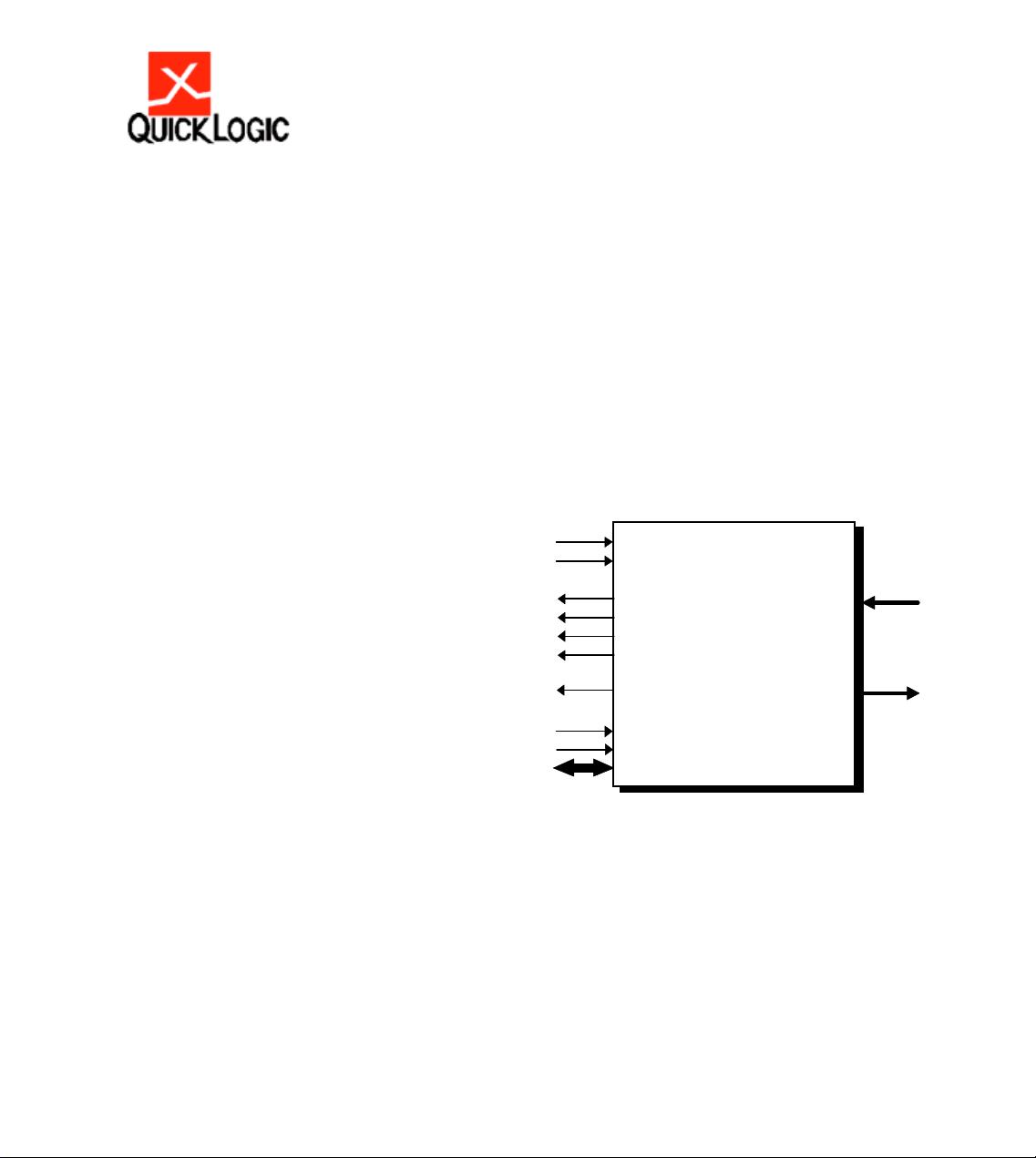

UART(通用异步收发传输器)是一种广泛用于设备间串行通信的接口标准,尤其在嵌入式系统和微控制器领域中应用广泛。在FPGA(现场可编程门阵列)设计中,UART模块的实现是实现系统与外部世界进行串行通信的关键部分。下面我们将深入探讨基于FPGA的UART设计及其相关知识点。 UART的工作原理: UART通过串行数据线进行通信,通常包括TX(发送)和RX(接收)两条线。它以字节为单位传输数据,每个字节前有起始位(通常是低电平),后跟数据位(8位)、奇偶校验位(可选)和停止位(通常为1或2位高电平)。UART采用异步通信方式,即收发双方无需共享时钟,而是依赖于数据帧的起止位来同步传输。 VHDL(Very High Speed Integrated Circuit Hardware Description Language)是FPGA设计中常用的硬件描述语言,用于描述数字系统的结构和行为。在UART的VHDL实现中,主要分为以下几部分: 1. 波特率发生器:UART的波特率决定了数据传输的速度。在FPGA中,波特率发生器通常使用分频器产生所需的波特率时钟,该时钟用于控制数据的发送和接收。 2. 发送器模块:发送器将并行数据转换为串行数据,按照预设的格式(起始位、数据位、奇偶校验位和停止位)进行编码,并通过TX线发送出去。在VHDL中,这通常涉及到移位寄存器和状态机的设计。 3. 接收器模块:接收器通过RX线接收串行数据,并将其解码为并行数据。同样,需要一个状态机来正确识别起始位、数据位、奇偶校验位和停止位。 4. 奇偶校验:奇偶校验位可以用于检测数据传输中的错误。发送端计算数据位的奇偶性并在数据帧中添加一个额外的位,接收端则根据接收到的数据重新计算奇偶性,若不一致则表示可能有误码。 5. FIFO(先进先出)缓冲区:在实际应用中,为了提高系统的实时性和处理突发数据流的能力,通常会在UART设计中加入FIFO,用于缓存待发送或接收到的数据。 在"uart.rar"压缩包中,我们看到几个相关的文件,如"UART.V"和"UART.VHD"可能是UART的VHDL源代码,"UART.TB"和"UART.TF"可能是测试平台或仿真文件,"QAN20.PDF"可能是UART的相关技术文档或论文,"资源说明.txt"可能提供了关于设计和使用的指导,而"RXCVER.V"和"TXMIT.V"以及它们的.vhd版本,可能是接收和发送模块的特定实现。 理解并掌握基于FPGA的UART设计,不仅可以帮助我们实现高效的串行通信,还可以为其他复杂的串行协议(如SPI、I2C等)的实现打下坚实的基础。通过学习和实践这些设计,我们可以更深入地理解数字系统设计和FPGA的工作原理。

uart.rar_UART VHDL_基于FPGA的UART (114个子文件)

uart.rar_UART VHDL_基于FPGA的UART (114个子文件)  uart_top_global_asgn_op.abo 271KB

uart_top_global_asgn_op.abo 271KB uart_top.root_partition.cmp.atm 43KB

uart_top.root_partition.cmp.atm 43KB uart_top.root_partition.map.atm 34KB

uart_top.root_partition.map.atm 34KB uart_top.cmp.bpm 854B

uart_top.cmp.bpm 854B uart_top.map.bpm 845B

uart_top.map.bpm 845B uart_top.cmp.cdb 60KB

uart_top.cmp.cdb 60KB uart_top.rtlv_sg.cdb 35KB

uart_top.rtlv_sg.cdb 35KB uart_top.pre_map.cdb 34KB

uart_top.pre_map.cdb 34KB uart_top.sgdiff.cdb 20KB

uart_top.sgdiff.cdb 20KB uart_top.map.cdb 18KB

uart_top.map.cdb 18KB uart_top.(3).cnf.cdb 11KB

uart_top.(3).cnf.cdb 11KB uart_top.(1).cnf.cdb 11KB

uart_top.(1).cnf.cdb 11KB uart_top.(4).cnf.cdb 9KB

uart_top.(4).cnf.cdb 9KB uart_top.(0).cnf.cdb 3KB

uart_top.(0).cnf.cdb 3KB uart_top.(2).cnf.cdb 2KB

uart_top.(2).cnf.cdb 2KB uart_top.rtlv_sg_swap.cdb 2KB

uart_top.rtlv_sg_swap.cdb 2KB uart_top.map_bb.cdb 859B

uart_top.map_bb.cdb 859B uart_top.eco.cdb 161B

uart_top.eco.cdb 161B uart_top.db_info 137B

uart_top.db_info 137B uart_top.cmp0.ddb 166KB

uart_top.cmp0.ddb 166KB uart_top.cmp2.ddb 54KB

uart_top.cmp2.ddb 54KB uart_top.asm_labs.ddb 7KB

uart_top.asm_labs.ddb 7KB uart_top.tis_db_list.ddb 174B

uart_top.tis_db_list.ddb 174B uart_top.root_partition.cmp.dfp 33B

uart_top.root_partition.cmp.dfp 33B uart_top.done 26B

uart_top.done 26B uart_top.root_partition.map.dpi 1KB

uart_top.root_partition.map.dpi 1KB uart_top.cmp.ecobp 28B

uart_top.cmp.ecobp 28B uart_top.map.ecobp 28B

uart_top.map.ecobp 28B uart_top.sgdiff.hdb 20KB

uart_top.sgdiff.hdb 20KB uart_top.pre_map.hdb 19KB

uart_top.pre_map.hdb 19KB uart_top.rtlv.hdb 18KB

uart_top.rtlv.hdb 18KB uart_top.cmp.hdb 18KB

uart_top.cmp.hdb 18KB uart_top.map.hdb 17KB

uart_top.map.hdb 17KB uart_top.map_bb.hdb 7KB

uart_top.map_bb.hdb 7KB uart_top.(1).cnf.hdb 3KB

uart_top.(1).cnf.hdb 3KB uart_top.(0).cnf.hdb 2KB

uart_top.(0).cnf.hdb 2KB uart_top.(3).cnf.hdb 2KB

uart_top.(3).cnf.hdb 2KB uart_top.(4).cnf.hdb 2KB

uart_top.(4).cnf.hdb 2KB uart_top.(2).cnf.hdb 1KB

uart_top.(2).cnf.hdb 1KB uart_top.root_partition.cmp.hdbx 9KB

uart_top.root_partition.cmp.hdbx 9KB uart_top.root_partition.map.hdbx 8KB

uart_top.root_partition.map.hdbx 8KB uart_top.hier_info 13KB

uart_top.hier_info 13KB uart_top.hif 4KB

uart_top.hif 4KB uart_top.lpc.html 2KB

uart_top.lpc.html 2KB uart_top.root_partition.map.kpt 79KB

uart_top.root_partition.map.kpt 79KB uart_top.map.kpt 79KB

uart_top.map.kpt 79KB uart_top.cmp_merge.kpt 345B

uart_top.cmp_merge.kpt 345B uart_top.root_partition.cmp.kpt 341B

uart_top.root_partition.cmp.kpt 341B uart_top.cmp.kpt 339B

uart_top.cmp.kpt 339B uart_top.cmp.logdb 4B

uart_top.cmp.logdb 4B uart_top.map.logdb 4B

uart_top.map.logdb 4B uart_top.map_bb.logdb 4B

uart_top.map_bb.logdb 4B uart_top.root_partition.cmp.logdb 4B

uart_top.root_partition.cmp.logdb 4B QAN20.PDF 206KB

QAN20.PDF 206KB uart_top.pin 27KB

uart_top.pin 27KB uart_top.pof 512KB

uart_top.pof 512KB prev_cmp_uart_top.fit.qmsg 68KB

prev_cmp_uart_top.fit.qmsg 68KB uart_top.fit.qmsg 68KB

uart_top.fit.qmsg 68KB uart_top.tan.qmsg 64KB

uart_top.tan.qmsg 64KB prev_cmp_uart_top.tan.qmsg 64KB

prev_cmp_uart_top.tan.qmsg 64KB uart_top.map.qmsg 17KB

uart_top.map.qmsg 17KB prev_cmp_uart_top.map.qmsg 17KB

prev_cmp_uart_top.map.qmsg 17KB prev_cmp_uart_top.qmsg 14KB

prev_cmp_uart_top.qmsg 14KB prev_cmp_uart_top.asm.qmsg 2KB

prev_cmp_uart_top.asm.qmsg 2KB uart_top.asm.qmsg 2KB

uart_top.asm.qmsg 2KB uart_top.rpp.qmsg 2KB

uart_top.rpp.qmsg 2KB uart_top.qpf 1KB

uart_top.qpf 1KB uart_top.qsf 3KB

uart_top.qsf 3KB uart_top.qws 175B

uart_top.qws 175B uart_top.root_partition.cmp.rcf 13KB

uart_top.root_partition.cmp.rcf 13KB uart_top.cmp.rdb 28KB

uart_top.cmp.rdb 28KB uart_top.lpc.rdb 470B

uart_top.lpc.rdb 470B README 653B

README 653B uart_top.fit.rpt 121KB

uart_top.fit.rpt 121KB uart_top.tan.rpt 118KB

uart_top.tan.rpt 118KB uart_top.map.rpt 41KB

uart_top.map.rpt 41KB uart_top.asm.rpt 7KB

uart_top.asm.rpt 7KB uart_top.flow.rpt 7KB

uart_top.flow.rpt 7KB uart_top.atom.rvd 37KB

uart_top.atom.rvd 37KB uart_top.sgate.rvd 30KB

uart_top.sgate.rvd 30KB uart_top.sgate_sm.rvd 10KB

uart_top.sgate_sm.rvd 10KB uart_top.sld_design_entry_dsc.sci 154B

uart_top.sld_design_entry_dsc.sci 154B uart_top.sld_design_entry.sci 154B

uart_top.sld_design_entry.sci 154B uart_top.fit.smsg 513B

uart_top.fit.smsg 513B uart_top.sof 235KB

uart_top.sof 235KB uart_top.tan.summary 2KB

uart_top.tan.summary 2KB uart_top.fit.summary 599B

uart_top.fit.summary 599B uart_top.map.summary 462B

uart_top.map.summary 462B uart_top.syn_hier_info 0B

uart_top.syn_hier_info 0B UART.TB 5KB

UART.TB 5KB uart_top.cmp.tdb 45KB

uart_top.cmp.tdb 45KB UART.TF 4KB

UART.TF 4KB uart_top.tmw_info 304B

uart_top.tmw_info 304B uart_top.lpc.txt 2KB

uart_top.lpc.txt 2KB uart_top.smp_dump.txt 831B

uart_top.smp_dump.txt 831B VERSION.TXT 682B

VERSION.TXT 682B 资源说明.txt 437B

资源说明.txt 437B RXCVER.V 6KB

RXCVER.V 6KB TXMIT.V 5KB

TXMIT.V 5KB UART.V 2KB

UART.V 2KB- 1

- 2

- 粉丝: 76

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- pyheif-0.8.0-cp37-cp37m-win-amd64.whl.zip

- pyheif-0.8.0-cp38-cp38-win-amd64.whl.zip

- pyheif-0.8.0-cp39-cp39-win-amd64.whl.zip

- pyheif-0.8.0-cp313-cp313-win-amd64.whl.zip

- MyBatis SQL mapper framework for Java.zip

- pyheif-0.8.0-cp312-cp312-win-amd64.whl.zip

- pyheif-0.8.0-cp311-cp311-win-amd64.whl.zip

- pyheif-0.8.0-cp310-cp310-win-amd64.whl.zip

- 基于51单片机万年历(程序源码、原理图、实验报告)-基于单片机的万年历设计

- 51单片机万年历(源码+实验报告).zip (高分大作业项目)

信息提交成功

信息提交成功