OpenCores EV_JPEG_ENC 9/21/2022

tmp.doc

Michal Krepa

Page 2 of 52

Created on 3/10/2009

1:11:00 AM

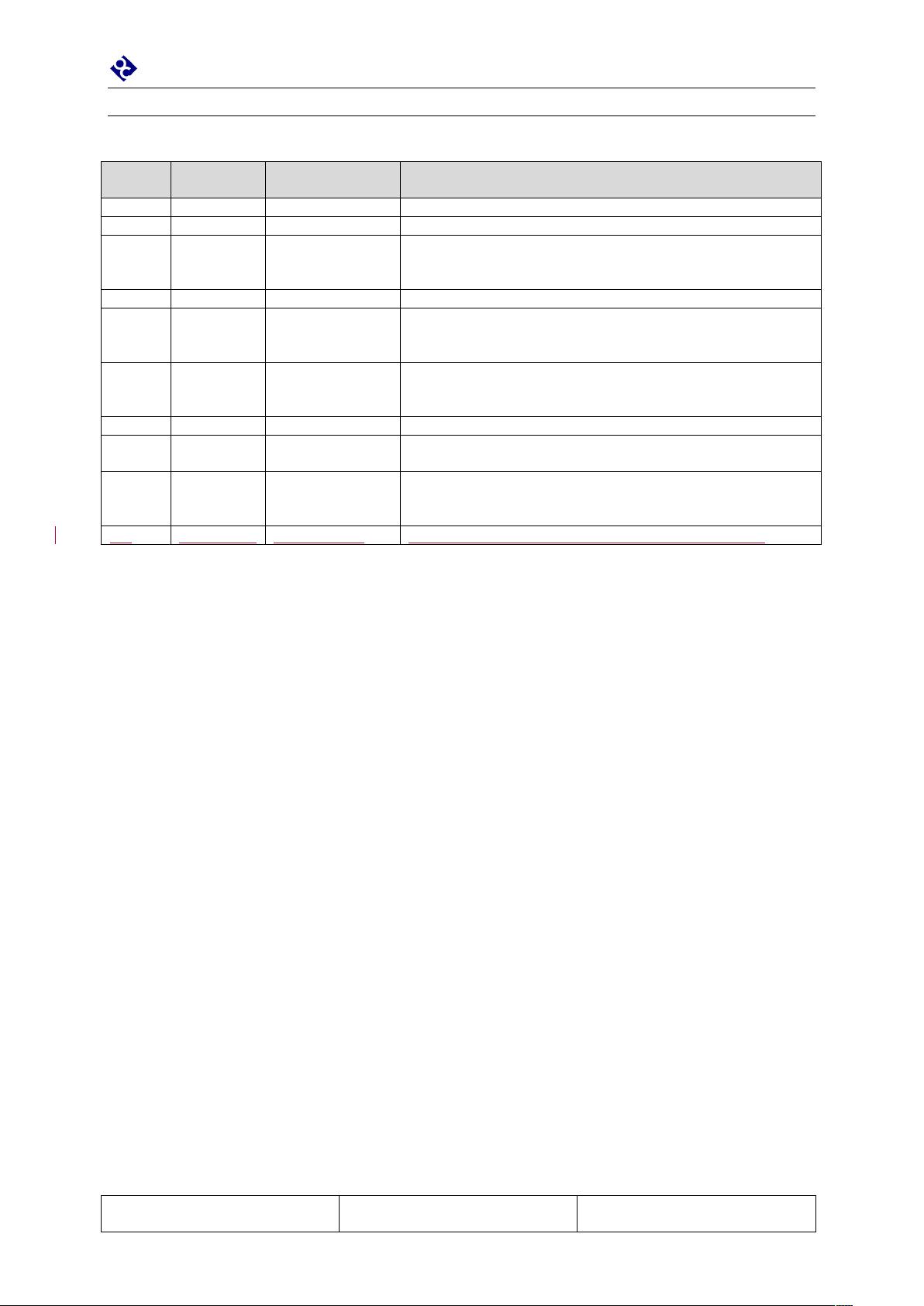

Version

Date

Author

Comment

1.0

15.02.2009

Michal Krepa

Initial Creation.

1.1

13.03.2009

Michal Krepa

Huffman description updated.

1.2

17.03.2009

Michal Krepa

Huffman design restored to use two stage VLI/VLC

handler to achieve better timing. Simulation HOWTO

chapter added.

1.3

19.03.2009

Michal Krepa

BUF_FIFO fifo almost full signal changed.

1.4

20.03.2009

Michal Krepa

Added C_MEMORY_OPTIMIZED configuration constant

to reduce memory footprint at expense of performance.

Look at BUF_FIFO description for details.

1.5

24.03.2009

Michal Krepa

BUF_FIFO now uses single RAM which is used for all

SubFIFOs. Added description of divider used in Quantizer

block.

1.6

26.03.2009

Michal Krepa

Added chrominance quantization table support.

1.7

28.03.2009

Michal Krepa

Added separate pipeline stage for Quantizer to balance

chain load across design.

1.8

29.03.2009

Michal Krepa

Added chrominance table support for Huffman encoding.

Fixed bug in RLE for ZRL (Zero Run Length) handling.

Fixed bug in number of encoded bytes output.

1.9

05.02.2009

Michal Krepa

Fixed bugs in BUF_FIFO almost full flag generation.

OpenCores EV_JPEG_ENC 9/21/2022

tmp.doc

Michal Krepa

Page 3 of 52

Created on 3/10/2009

1:11:00 AM

1.1 EV_JPEG_ENC..........................................................................................................................5

1.1.1 General description............................................................................................................5

1.1.2 Architecture........................................................................................................................5

1.1.3 Features.............................................................................................................................5

1.1.4 Example throughput...........................................................................................................6

1.1.5 Open points / TODO list / Limitations.................................................................................6

1.1.6 Control State Machine (CTRL_SM) ...................................................................................7

1.1.7 MAIN_SM...........................................................................................................................8

1.1.8 MAIN_SM details .............................................................................................................10

1.1.9 BUF_FIFO........................................................................................................................11

1.1.10 Output Mux ......................................................................................................................13

1.2 Host IF ......................................................................................................................................14

1.3 FDCT ........................................................................................................................................17

1.3.1 BUF_FIFO Read Controller .............................................................................................17

1.3.2 FRAM1.............................................................................................................................18

1.3.3 RGB to YCbCr conversion ...............................................................................................18

1.3.4 Write Counter / DCT matrix transpose.............................................................................18

1.3.5 Mux1 ................................................................................................................................19

1.3.6 MDCT...............................................................................................................................19

1.3.7 FIFO1 and FIFO RD CTRL ..............................................................................................19

1.3.8 DBUF ...............................................................................................................................19

1.4 ZIGZAG ....................................................................................................................................20

1.4.1 ZIGZAG Core...................................................................................................................21

1.4.2 FIFO ctrl ...........................................................................................................................22

1.4.3 DBUF ...............................................................................................................................22

1.5 QUANTIZER.............................................................................................................................23

1.5.2 DBUF ...............................................................................................................................24

1.6 RLE...........................................................................................................................................27

1.6.1 RLE Core .........................................................................................................................28

1.6.2 Entropy Coder..................................................................................................................29

1.6.3 Read counter ...................................................................................................................29

1.6.4 EOB Detector / Write Counter..........................................................................................29

1.6.5 Double FIFO ....................................................................................................................30

1.7 HUFFMAN Encoder..................................................................................................................31

1.7.1 General Description .........................................................................................................31

1.7.2 Operation .........................................................................................................................31

1.7.3 Double FIFO ....................................................................................................................32

1.7.4 Mux ..................................................................................................................................33

1.7.5 Variable Length Processor...............................................................................................34

1.7.6 DC Luminance ROM........................................................................................................38

1.7.7 DC Chrominance ROM ....................................................................................................39

1.7.8 AC Luminance ROM ........................................................................................................40

1.7.9 AC Chrominance ROM ....................................................................................................40

1.8 Byte Stuffer...............................................................................................................................42

1.8.1 CTRL_SM ........................................................................................................................42

1.8.2 Write Counter...................................................................................................................43

1.8.3 Byte Stuff Detector...........................................................................................................43

1.8.4 bs_buf_sel........................................................................................................................43

1.8.5 last_addr ..........................................................................................................................43

1.9 JFIF Header Generator ............................................................................................................44

1.9.1 Header RAM Programming..............................................................................................44

1.9.2 JFIF Generator.................................................................................................................45

1.9.3 EOI Writer ........................................................................................................................45

1.9.4 Mux1/Mux2 ......................................................................................................................45

1.9.5 Header RAM ....................................................................................................................45

1.9.6 Generic Header................................................................................................................45

1.10 Programming Interface.........................................................................................................49

1.10.1 General ............................................................................................................................49

1.10.2 Core address map ...........................................................................................................49

OpenCores EV_JPEG_ENC 9/21/2022

tmp.doc

Michal Krepa

Page 4 of 52

Created on 3/10/2009

1:11:00 AM

1.10.3 Register Descriptions.......................................................................................................49

1.11 Users Manual .......................................................................................................................51

1.12 Simulation.............................................................................................................................52

1.12.1 OPB Master BFM.............................................................................................................52

OpenCores EV_JPEG_ENC 9/21/2022

tmp.doc

Michal Krepa

Page 5 of 52

Created on 3/10/2009

1:11:00 AM

1.1 EV_JPEG_ENC

1.1.1 General description

EV_JPEG_ENC core is intended to encode raw bitmap images into JPEG compliant coded bit stream.

JPEG baseline encoding method is used.

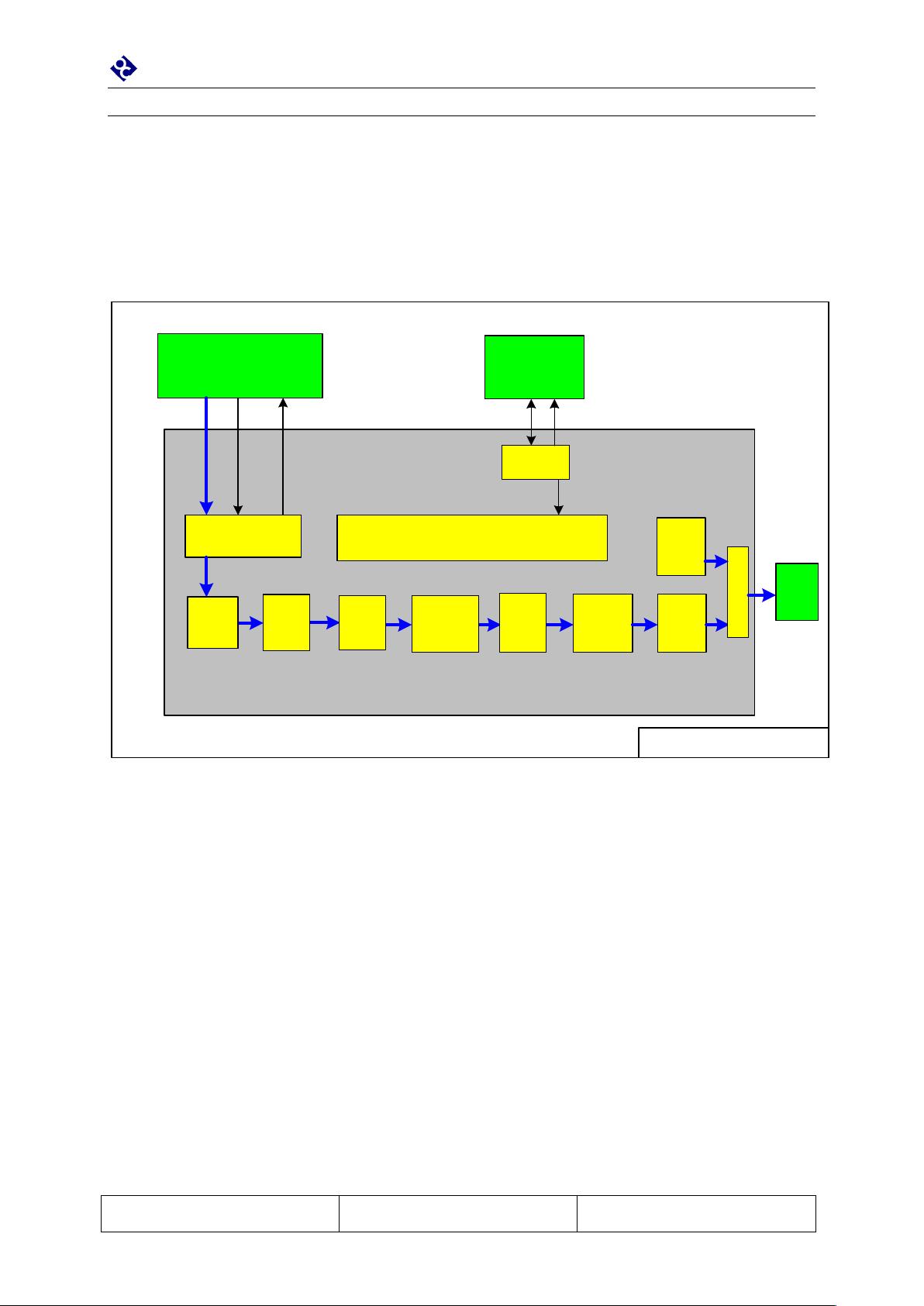

1.1.2 Architecture

JPEG_ENC.vsd

data(23:0)

HOST DATA

HOST

PROG

Huffman

Encoder

RLE

ZIG

ZAG

Quantizer

DCT

2D

RGB

to

YCbCr

Pipeline Controller

RAM

Host IF

sof

size_x

size_y

almost_full

Byte

Stuffer

ready_int

JFIF

GEN

m

u

x

BUF_FIFO

we

Figure 1

General system architecture consist of encoding chain started by Host Programming interface. Host

Data interface shall continuously write BUF_FIFO until FIFO almost full signal is received. Then, it

should stop and wait for signal FIFO almost full to deassert. When this is the case it should continue

writing and so on.

Encoding is governed by Controller and is a pipelined process where each pipeline stage process 8x8

block of samples at a time (8x8 block is so called “data unit”).

Finally, encoded bit stream is byte stuffed and then stored to output (RAM or FIFO).

Following steps are performed: Line Buffering, RGB to YCbCr conversion, Discrete Cosine Transform

2-dimensional, followed by Zig Zag scan, Quantizer, , Run Length Encoding and Huffman coding

followed by byte stuffing and JFIF header is also generated at the beginning of encoding and with EOI

marker closing image.

1.1.3 Features

� JPEG baseline encoding JPEG ITU-T T.81 | ISO/IEC 10918-1

� Standard JFIF header v 1.01 automatic generation

� Color images only (3 components, RGB input)

� Two programmable Quantization tables, one for luminance and one for chrominance

� Hardcoded Huffman tables