EDA技术实用教程

第

第

6

6

章

章

VHDL

VHDL

设

设

计

计

进

进

阶

阶

6.1 4位加法计数器的VHDL描述

6.1.1 4位加法计数器

【例6-1】

ENTITY CNT4 IS

PORT ( CLK : IN BIT ;

Q : BUFFER INTEGER RANGE 15 DOWNTO 0 ) ;

END ;

ARCHITECTURE bhv OF CNT4 IS

BEGIN

PROCESS (CLK)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN

Q <= Q + 1 ;

END IF;

END PROCESS ;

END bhv;

6.1.2 整数、自然数和正整数数据类型

整数常量的书写方式示例如下:

1 十进制整数

0 十进制整数

35 十进制整数

10E3 十进制整数

16#D9# 十六进制整数

8#720# 八进制整数

2#11010010# 二进制整数

6.1 4位加法计数器的VHDL描述

6.1.3 4位加法计数器的另一种表达方式

【例6-2】

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

USE IEEE.STD_LOGIC_UNSIGNED.ALL ;

ENTITY CNT4 IS

PORT ( CLK : IN STD_LOGIC ;

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ) ;

END ;

ARCHITECTURE bhv OF CNT4 IS

SIGNAL Q1 : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS (CLK)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN

Q1 <= Q1 + 1 ;

END IF;

Q <= Q1 ;

END PROCESS ;

END bhv;

6.1.3 4位加法计数器的另一种表达方式

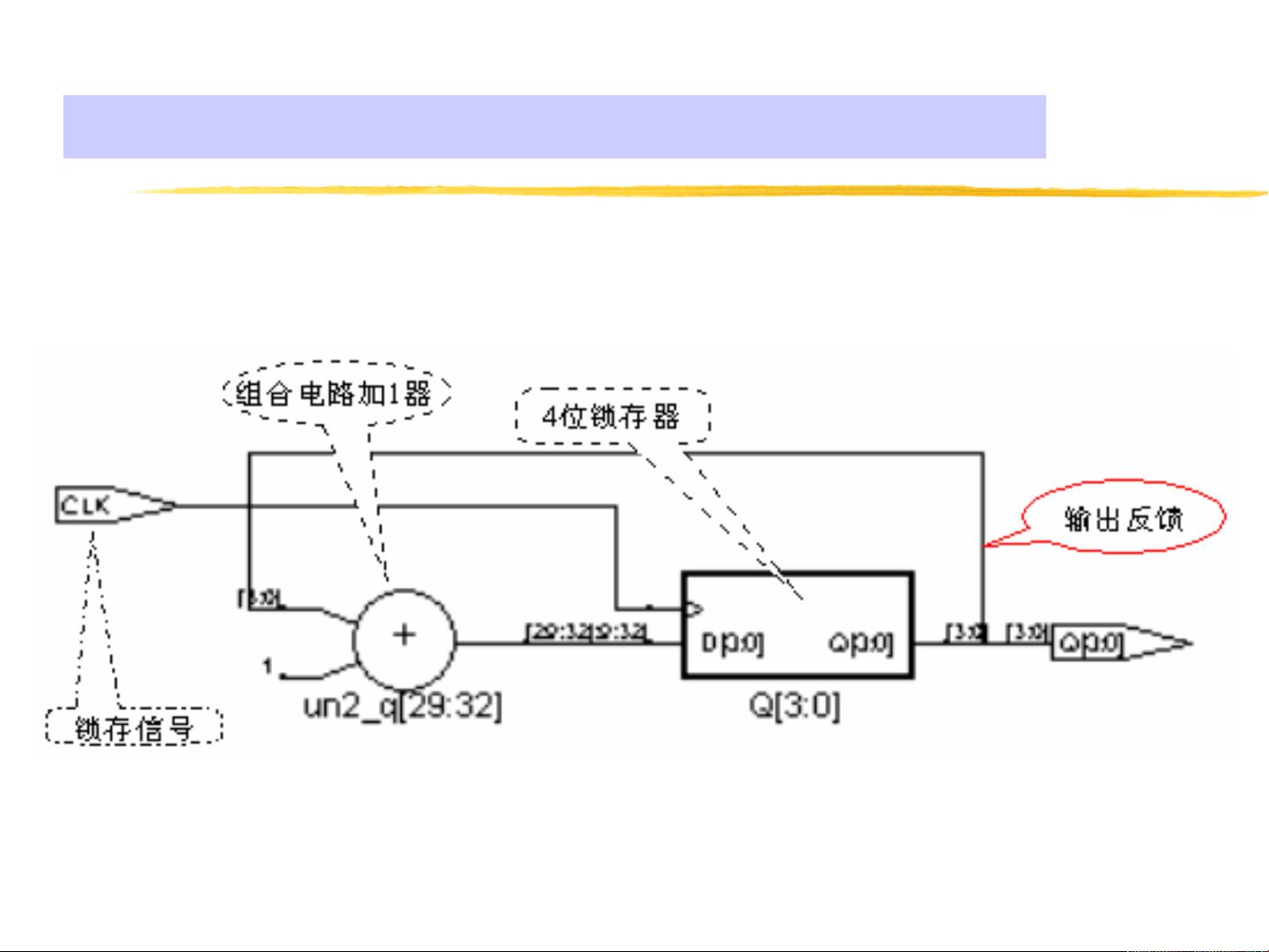

4位加法计数器由两大部分组成:

图6-1 4位加法计数器RTL电路