05-cache_v1.rar_cache_v1_s3c4510

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

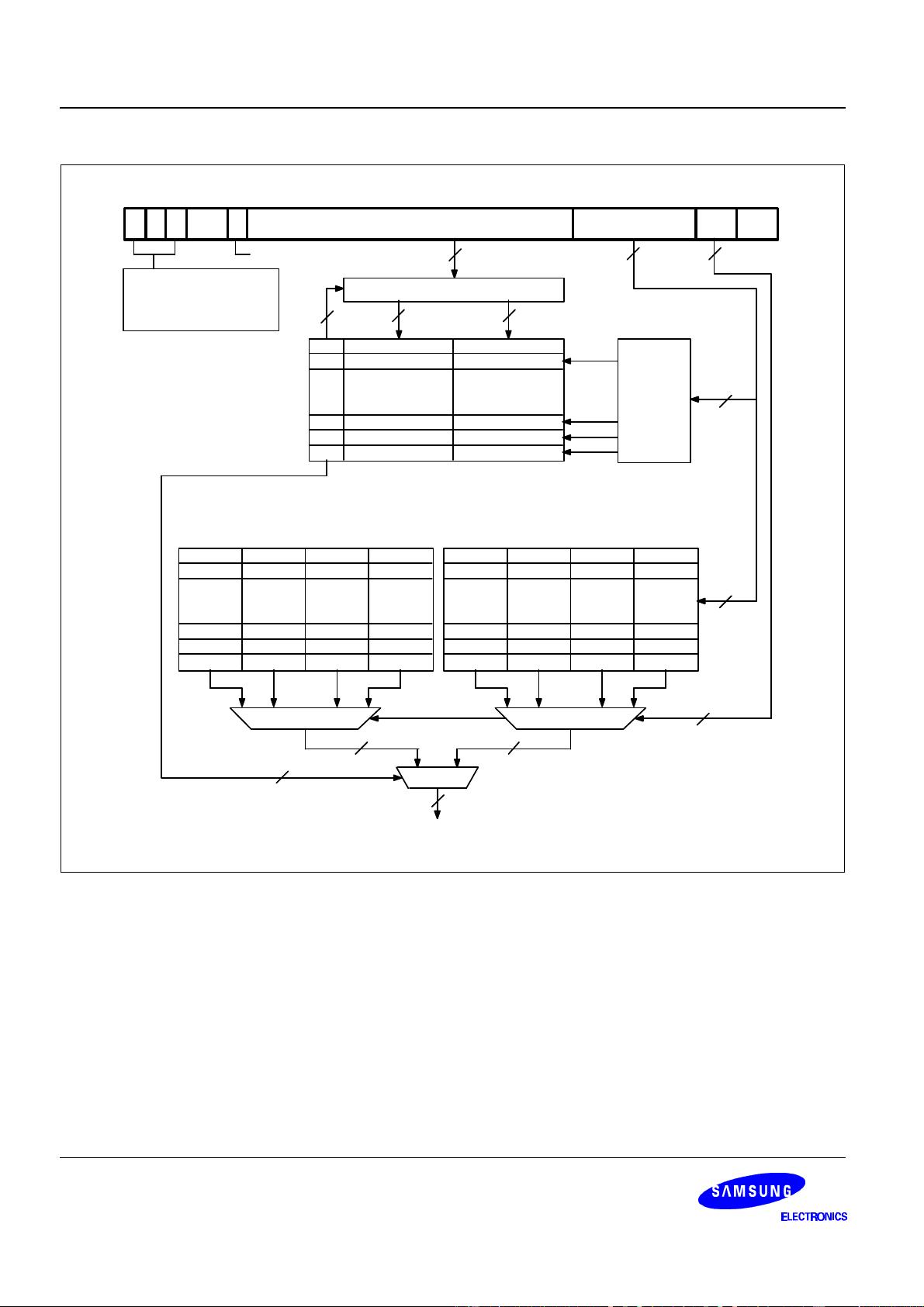

《S3C4510开发板与Cache_v1详解》 在嵌入式系统领域,三星的S3C4510处理器是一款经典而重要的微处理器,它被广泛应用于各种嵌入式设备的设计中。本文档将深入探讨S3C4510开发板的使用,以及与其密切相关的Cache_v1机制,旨在为开发者提供详尽的设计资料和实践指导。 S3C4510是一款基于ARM7TDMI架构的RISC(精简指令集计算机)处理器,具有高性能、低功耗的特点。它支持多种操作系统,如Linux、Windows CE等,适用于嵌入式应用如工业控制、通信设备和消费电子等。S3C4510开发板则为开发者提供了验证和调试该处理器功能的平台,包含必要的外围接口,如串口、USB、以太网、GPIO等,方便进行硬件原型设计和软件开发。 Cache_v1是S3C4510中的高速缓存系统,对于提升处理器性能至关重要。缓存是一种存储技术,用于临时存储频繁访问的数据,减少主存访问时间,提高系统运行速度。Cache_v1可能包含数据缓存和指令缓存两部分,通过高速总线与处理器核心相连。理解并优化Cache的使用,能显著提升系统整体性能。 在“05-cache_v1.pdf”文档中,详细介绍了S3C4510处理器的Cache_v1配置、操作模式、缓存替换策略(如LRU或PLRU)、写策略(写直达、写回、写分配等)以及缓存一致性等问题。开发者需要掌握如何在编程时考虑缓存的影响,例如避免数据冲突、最小化缓存失效,以充分利用Cache_v1的优势。 同时,“www.pudn.com.txt”文件可能是下载来源或附加信息,虽然在本文档中未直接涉及具体技术细节,但它可能提供了获取更多相关资源的链接,如其他开发者的经验分享、源代码示例或更新的技术文档。 这份“05-cache_v1.rar_cache_v1_s3c4510”资料集合,为S3C4510开发人员提供了宝贵的学习和参考材料,涵盖了从硬件设计到软件优化的多个层面。通过深入学习和实践,开发者可以更好地理解和利用S3C4510处理器的特性,提高其在实际项目中的应用效能。

05-cache_v1.rar (2个子文件)

05-cache_v1.rar (2个子文件)  www.pudn.com.txt 218B

www.pudn.com.txt 218B 05-cache_v1.pdf 28KB

05-cache_v1.pdf 28KB- 1

- 粉丝: 109

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 智能笔项目源代码全套技术资料.zip

- 在线考试系统项目源代码全套技术资料.zip

- 高等数学学习资料合集 高等数学(工本)mind

- 西门子V90效率倍增-伺服驱动功能库详解简易循环功能库之Homing-V90PN.mp4

- 自考04741计算机网络原理真题及答案及课件

- 基于STM32芯片开发 安防系统 完整作品

- 4_base.apk.1

- 学生导师双选系统项目源代码全套技术资料.zip

- 自考02318《计算机组成原理》试题及答案 2014-2018及课件

- 图书管理系统,仅供参考

- 数据科学与大数据毕业设计系统项目源代码全套技术资料.zip

- 全国自考02197概率论与数理统计(二)试题及答案2014-2019

- CHGCOLOR压缩包

- 多轮自动红队方法提升大语言模型安全性

- python语言kssp爬虫程序代码XQZQ.txt

- 亲测源码云赏V7.0微信视频打赏系统源码已测试完整无错版

信息提交成功

信息提交成功