© Copyright 2019 WIZnet Co., Ltd. All rights reserved.

W6100

Hardwired Dual TCP/IP Stack Controller

V1.0.0

http://www.wiznet.io/

W6100 – Hardwired Dual TCP/IP Stack Controller 2/149

W6100

W6100 is a hardwired Internet controller chip supporting IPv4/IPv6 dual stack by adding IPv6

functions on the basis of WIZnet’s patented hardwired TCP/IP core technology. W6100 supports

TCP/IP protocols such as TCP, UDP, IPv6, IPv4, ICMPv6, ICMPv4, IGMP, ARP and PPPoE. W6100

also includes 10Base-T / 10Base-Te / 100Base-TX Ethernet PHY and Ethernet MAC Controller

which makes it suitable for embedded internet-enabled devices.

W6100 has 8 independent hardwired SOCKETs and supports various SOCKET-less commands,

which are for IPv6 auto-configuration, monitoring, and managing the network via ARP, PINGv4,

and PINGv6.

W6100 supports two kinds of HOST interfaces; SPI and parallel system BUS. It has 32KB internal

memory for sending and receiving data. Designed for low power and low heat, W6100 provides

WOL (Wake On LAN), Ethernet PHY power down mode and etc.

W6100 has two package types; 48 LQFP and 48 QFN lead-free.

Both versions are PIN-2-PIN compatible with W5100S.

W6100 – Hardwired Dual TCP/IP Stack Controller 3/149

Features

- Supports hardwired TCP/IP protocols

: TCP, UDP, IPv6, IPv4, ICMPv6, ICMPv4, IGMP, MLDv1, ARP, PPPoE

- Supports IPv4/IPv6 dual stack

- Supports 8 independent SOCKETs simultaneously with 32KB memory

- Supports SOCKET-less commands

: ARP, ICMPv6 (ARP, DAD, NA, RS) command for IPv6 auto-configuration & network

monitoring (PING, PING6)

- Supports Ethernet PHY power down mode & system clock switching for power save

- Supports wake on LAN over UDP

- Supports serial & parallel HOST interface

: High speed SPI (MODE 0/3), system BUS with 2 address signal & 8bit data

- Internal 32Kbytes memory for TX/ RX Buffers

- 10BaseT/ 10BaseTe / 100BaseTX Ethernet PHY integrated

- Supports auto negotiation (full/half duplex, 10 and 100-based)

- Supports auto-MDIX only on auto-negotiation mode

- Does not support IP fragmentation & jumbo packet

- 3V operation with 5V I/O signal tolerance

- Network indicator LEDs (full/half duplex, link, 10/100 speed, active)

- 48 Pin LQFP & QFN lead-free package (7x7mm, 0.5mm pitch)

- PIN-2-PIN compatible with W5100S

Target Applications

W6100 can be used in various applications.

- Home network devices: set-top boxes, PVRs, digital media adapters

- Serial-to-Ethernet: access control, LED display, wireless AP relay

- Parallel-to-Ethernet: POS / mini printers, copy machine

- USB-to-Ethernet: storage devices, network printers

- GPIO-to-Ethernet: Home network sensors

- Security systems: DVR, network cameras, kiosks

- Factory & home automation

- Medical monitoring equipment

- Embedded servers

- Internet of Thing (IoT) devices

- IoT cloud devices

- Etc

W6100 – Hardwired Dual TCP/IP Stack Controller 4/149

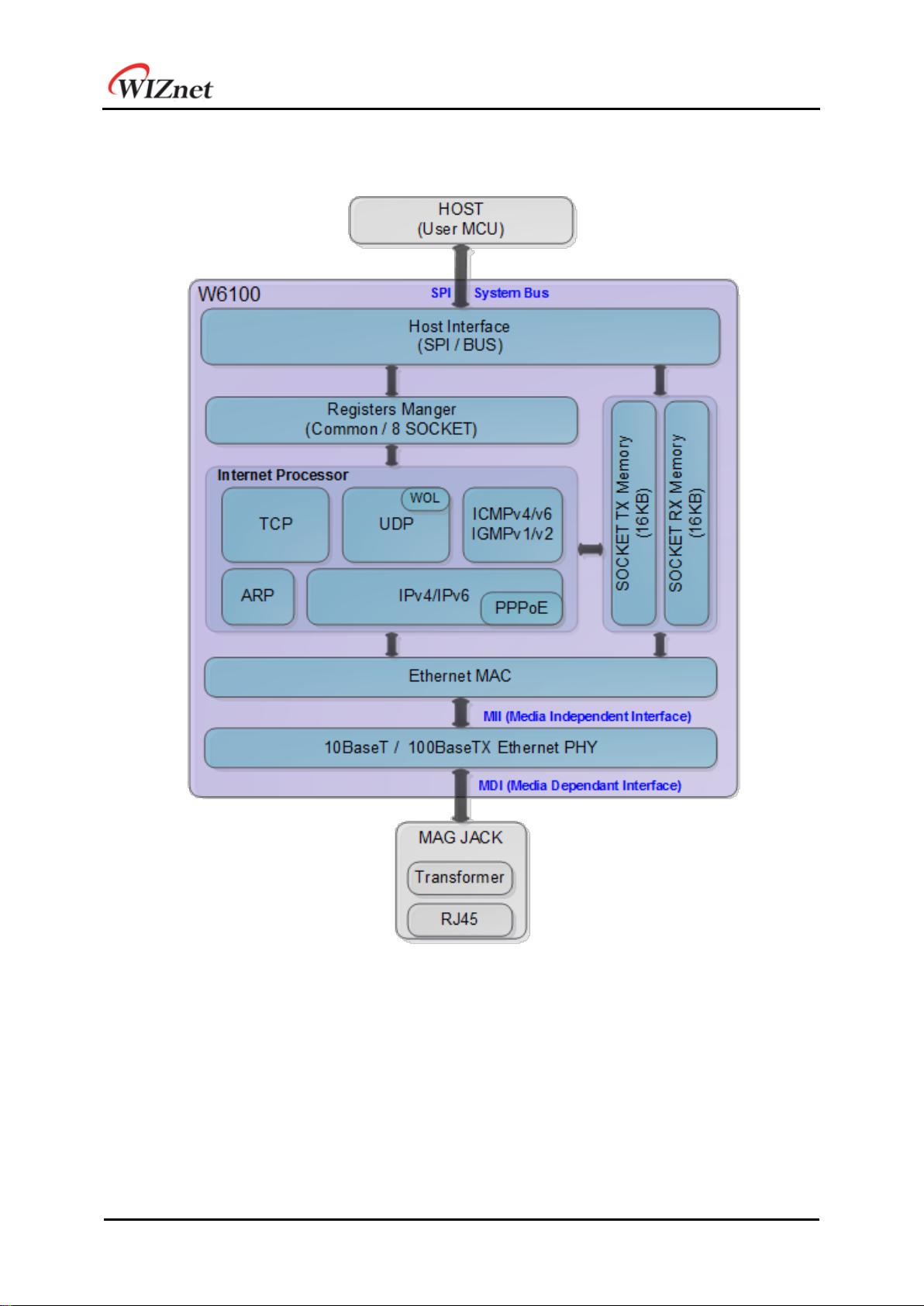

Block Diagram

Figure 1 Block Diagram

W6100 – Hardwired Dual TCP/IP Stack Controller 5/149

Contents

1. PIN Description ........................................................................................ 12

1.1 PIN Description ........................................................................... 13

2. Memory Map ............................................................................................ 17

3. W6100 Registers ....................................................................................... 19

3.1 Common Register ........................................................................ 19

3.2 SOCKET Register .......................................................................... 25

4. Register Descriptions ................................................................................. 27

4.1 Common Registers ....................................................................... 28

4.1.1 CIDR (Chip Identification Register) ................................................... 28

4.1.2 VER (Version Register) ................................................................. 28

4.1.3 SYSR (System Status Register) ........................................................ 28

4.1.4 SYCR0 (System Config Register 0) .................................................... 29

4.1.5 SYCR1 (System Config Register 1) .................................................... 30

4.1.6 TCNTR (Tick Counter Register) ....................................................... 30

4.1.7 TCNTRCLR (TCNTR Clear Register) ................................................... 30

4.1.8 IR (Interrupt Register) .................................................................. 30

4.1.9 SIR (SOCKET Interrupt Register) ...................................................... 31

4.1.10 SLIR (SOCKET-less Interrupt Register) .............................................. 32

4.1.11 IMR (Interrupt Mask Register) ........................................................ 33

4.1.12 IRCLR (IR Clear Register) ............................................................. 34

4.1.13 SIMR (SOCKET Interrupt Mask Register) ............................................ 34

4.1.14 SLIMR (SOCKET-less Interrupt Mask Register) ...................................... 34

4.1.15 SLIRCLR (SLIR Clear Register) ........................................................ 35

4.1.16 SLPSR (SOCKET-less Prefer Source IPv6 Address Register) ....................... 35

4.1.17 SLCR (SOCKET-less Command Register) ............................................ 36

4.1.18 PHYSR (PHY Status Register) ......................................................... 37

4.1.19 PHYRAR (PHY Register Address Register) .......................................... 37

4.1.20 PHYDIR (PHY Data Input Register) .................................................. 38

4.1.21 PHYDOR (PHY Data Output Register) ............................................... 38

4.1.22 PHYACR (PHY Access Control Register) ............................................. 38

4.1.23 PHYDIVR (PHY Division Register) .................................................... 38

4.1.24 PHYCR0 (PHY Control Register 0) ................................................... 39

4.1.25 PHYCR1 (PHY Control Register 1) ................................................... 39

4.1.26 NET4MR (Network IPv4 Mode Register) ............................................. 40

4.1.27 NET6MR (Network IPv6 Mode Register) ............................................. 41

4.1.28 NETMR (Network Mode Register) .................................................... 42

4.1.29 NETMR2 (Network Mode Register 2) ................................................ 43