MT2523 Series Datasheet

Version: 1.5

Release date: 5 May 2017

© 2015 - 2017 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc. (“MediaTek”) and/or its licensor(s). MediaTek cannot grant you

permission for any material that is owned by third parties. You may only use or reproduce this document if you have agreed to and been

bound by the applicable license agreement with MediaTek (“License Agreement”) and been granted explicit permission within the License

Agreement (“Permitted User”). If you are not a Permitted User, please cease any access or use of this document immediately. Any

unauthorized use, reproduction or disclosure of this document in whole or in part is strictly prohibited. THIS DOCUMENT IS PROVIDED ON AN

“AS-IS” BASIS ONLY. MEDIATEK EXPRESSLY DISCLAIMS ANY AND ALL WARRANTIES OF ANY KIND AND SHALL IN NO EVENT BE LIABLE FOR ANY

CLAIMS RELATING TO OR ARISING OUT OF THIS DOCUMENT OR ANY USE OR INABILITY TO USE THEREOF. Specifications contained herein are

subject to change without notice.

MT2523 Series Datasheet

© 2015 - 2017 MediaTek Inc.

Page i of iii

This document contains information that is proprietary to MediaTek Inc. (“MediaTek”) and/or its licensor(s).

Any unauthorized use, reproduction or disclosure of this document in whole or in part is strictly prohibited.

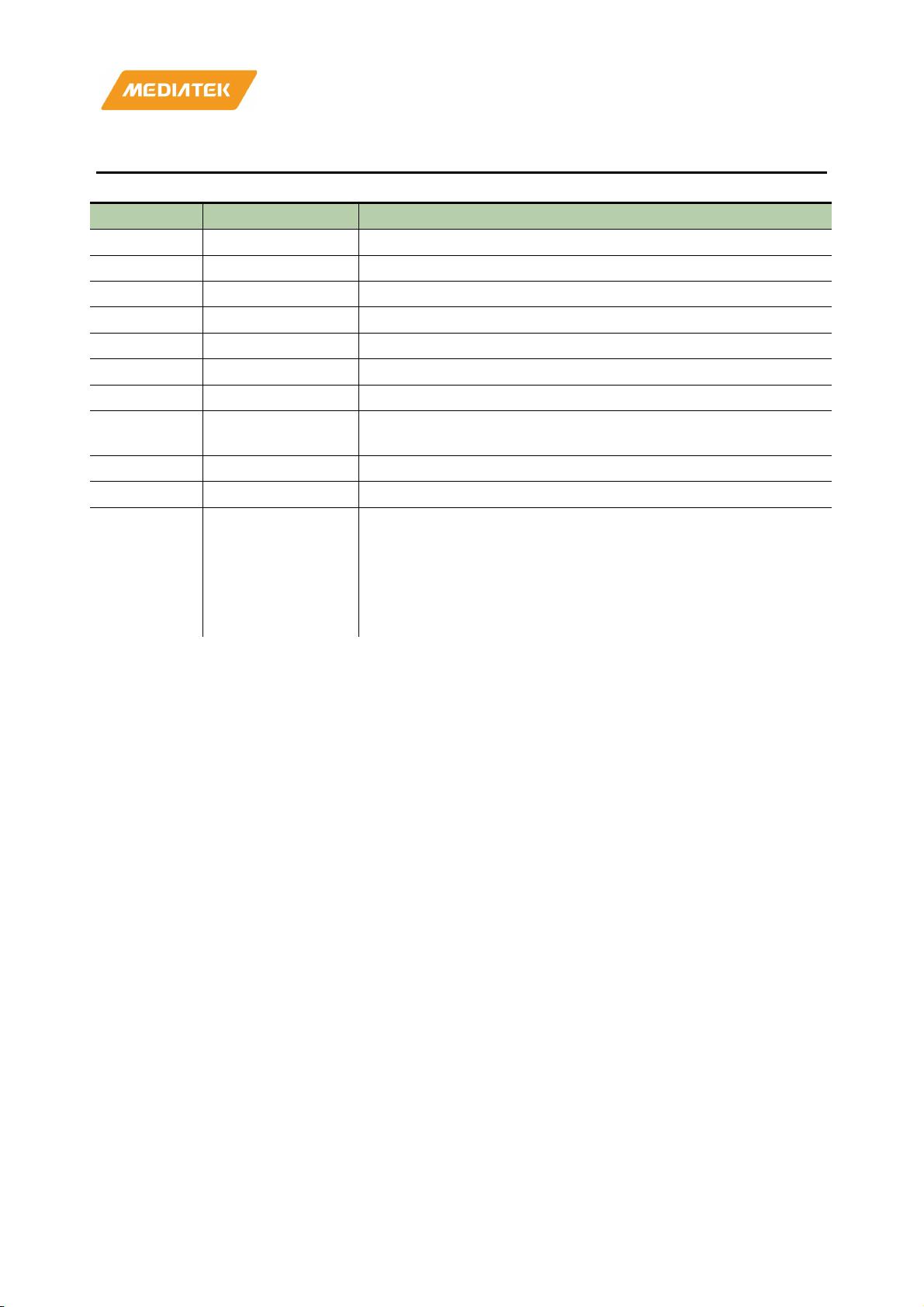

Document Revision History

Revision Date Description

0.1 26 June 2015 Initial release

0.2 11 December 2015 Document format update

0.3 29 January 2016 Review completed

0.4 28 April 2016 Updated power performance

0.9 17 May 2016 Updated PMU AUXADC specifications

1.0 06 June 2016 Updated Bluetooth specifications

1.1 14 September 2016 Updated platform performance specification

1.2 30 September 2016 Updated pinmux description, power consumption data, peripheral

functions by power scenario, and clock sources.

1.3 04 November 2016 Updated MT2523S information

1.4 13 January 2017 Updated interface timing diagram

1.5 5 May 2017 Updated the GPIO speed and added Table 2.5-1 in section 2.5.2,

“General Purpose Inputs/Outputs (GPIOs)”.

Removed GPT mode naming in section 2.5.4, “General Purpose Timer

(GPT)”.

Added MicBias0 description for Figure 2.6-1.

Added GPIO45 information to Table 6.4-1, “PinMux description”.

MT2523 Series Datasheet

© 2015 - 2017 MediaTek Inc.

Page ii of iii

This document contains information that is proprietary to MediaTek Inc. (“MediaTek”) and/or its licensor(s).

Any unauthorized use, reproduction or disclosure of this document in whole or in part is strictly prohibited.

Features

Platform

• 208MHz ARM® Cortex®-M4 with FPU

• High power efficiency with system DVFS

o 1.3V, 208MHz

o 1.2V, 104MHz

o 1.1V, 104MHz

o 0.9V, 26MHz

o 0.7V, 32kHz

• Hardware DVS from deep sleep (0.7V) to active

(0.9V or above)

• Fast 7µs wakeup from sleep to active

• Hardware DFS from 1.6MHz to 208MHz

• 17 DMA channels

• One RTC timer and six GPTs

• Crypto engine AES 128/192/256 bits

• True random number generator

• Ambient temperature from -40°C to 85°C

Memory

• 160kB SRAMs

o Zero-wait state

o Maximum frequency at 208MHz

• 32kB L1 cache

o High hit rate

o Zero-wait state

o Maximum frequency at 208MHz

• Embedded flash

o Sleep current 100nA

o Maximum frequency 78MHz

• Embedded pseudo SRAM

o Sleep current 10µA

o Maximum frequency 104MHz

Connectivity

• One USB2.0

• Two SDIO v2.0

• Three I2C (3.4Mbps) interfaces

• Three UARTs (3Mbps)

• Four SPI masters and one SPI slave (SCK signal

up to 13MHz)

• I2S master or slave

• PCM master

• Dual PDM digital MIC

• Six PWM channels

• 38 GPIOs

• 5 channel 12-bit AUXADC

• 10-bit general purpose DAC

• 3 x 3 matrix keypad

Bluetooth

• Bluetooth specification 4.2

• Dual mode (Bluetooth and Bluetooth LE)

• Integrated T/R switch, Balun and PA

• PA provides 8dBm output power

• Bluetooth and Bluetooth LE receiver sensitivity

of -93dBm and -96.5dBm, respectively

• Up to 7 simultaneous active ACL links

• One SCO or eSCO link with CVSD/mSBC coding

Audio codec

• AAC/SBC for Bluetooth audio

• CVSD/mSBC for Bluetooth speech

• PCM playback with 8-48kHz sample rate

• PCM record with 8kHz and 16kHz sample rate

MT2523 Series Datasheet

© 2015 - 2017 MediaTek Inc.

Page iii of iii

This document contains information that is proprietary to MediaTek Inc. (“MediaTek”) and/or its licensor(s).

Any unauthorized use, reproduction or disclosure of this document in whole or in part is strictly prohibited.

Display

• Hardware 2D accelerator supporting:

o 4 overlay layers

o ARGB8888, RGB888, RGB565, ARGB6666

o BitBlt supports 7 rotation types

o Alpha blending and font drawing

o Hardware display rotation

• Four blending layers with individual color depth,

window size, vertical and horizontal offset,

source key, dither and alpha value

• Read frame buffer format - RGB565, RGB888,

ARGB8888, PARGB8888, ARGB6666,

PARGB6666, YUYV422, index-4, index-2 and

index-1 color

• DBI serial interface supporting 320 x 320 pixels

and 30fps resolution

• 1-lane MIPI DSI interface with 480x320 pixels

and 30fps resolution (not supported in MT2523S)

Camera

• MediaTek camera serial interface

• VGA at 30fps with YUV422 or RGB565

Power management

• Wide Li+ battery voltage from 3.0V to 4.8V

• Multiple power supplies for 1.8V, 2.8V and 3.3V

• Power switch of 1.8V, 2.8V, 3.3V for low power

mode

• High efficiency buck (from 0.7V to 1.3V) for SOC

platform

• Pulse charger supports BC1.2

• 15-bit AUXADC for BATSNS

• Hardware thermal shutdown protection

• Supports LED current sink

• Supports Vibrator driver

• Supports WDT system reset

• Supports power key and long press shutdown

GNSS (MT2523G only)

• GPS, GLONASS, GALILEO and BEIDOU

• Supports multi-GNSS including QZSS, SBAS

ranging

• Supports WAAS/EGNOS/MSAS/GAGAN

• 12 multi-tone active interference cancellers

(ISSCC2011 award)

• Indoor and outdoor multi-path detection and

compensation

• Supports FCC E911 compliance and A-GPS

Package type

• Highly integrated chipset technology

• MT2523G: 9.2 x 6.0 x 1.05mm 246-ball TFBGA

with 0.4mm pitch (with GNSS)

• MT2523D: 6.2 x 5.8 x 1.05mm 165-ball TFBGA

with 0.4mm pitch

• MT2523S: 6.2 x 5.8 x 1.05mm 165-ball TFBGA

with 0.4mm pitch

MT2523 Series Datasheet

© 2015 – 2017 MediaTek Inc.

Page 1 of 125

This document contains information that is proprietary to MediaTek Inc. (“MediaTek”) and/or its licensor(s).

Any unauthorized use, reproduction or disclosure of this document in whole or in part is strictly prohibited.

Table of Contents

1. Overview ............................................................................................................................................... 7

Platform .............................................................................................................................................. 7

Multimedia ....................................................................................................................................... 11

Audio ................................................................................................................................................ 12

Bluetooth .......................................................................................................................................... 13

Debugging ......................................................................................................................................... 14

Power management ......................................................................................................................... 14

Package ............................................................................................................................................. 14

2. Functional Overview ............................................................................................................................. 15

2.1. Host processor subsystem ................................................................................................................ 15

2.2. Boot mode ........................................................................................................................................ 17

2.3. Clock source architecture ................................................................................................................. 18

2.4. Communication interfaces ............................................................................................................... 20

2.5. Peripherals ........................................................................................................................................ 22

2.6. Analog baseband .............................................................................................................................. 23

2.7. Audio front-end ................................................................................................................................ 31

3. Bluetooth RF Subsystem ....................................................................................................................... 34

3.1. Bluetooth description ....................................................................................................................... 34

3.2. Functional specifications .................................................................................................................. 35

4. Power Management Unit (PMU)........................................................................................................... 39

4.1. Power supply .................................................................................................................................... 40

4.2. Voltage regulator .............................................................................................................................. 41

4.3. Low power mode .............................................................................................................................. 46

4.4. Pulse battery charger (PCHR) ........................................................................................................... 47

4.5. Power on/off sequence .................................................................................................................... 51

4.6. LED current sink (ISINK) .................................................................................................................... 53

4.7. Vibrator driver .................................................................................................................................. 54

4.8. PMU AUXADC ................................................................................................................................... 54

5. Low Power Control System ................................................................................................................... 56

5.1. Power sources .................................................................................................................................. 56

5.2. MTCMOS power domain .................................................................................................................. 57

5.3. Power modes .................................................................................................................................... 57

5.4. Power performance summary .......................................................................................................... 58

5.5. Peripheral constraints and voltage for power mode ........................................................................ 61

6. Pin Description ..................................................................................................................................... 63

6.1. MT2523G ball diagram ..................................................................................................................... 63

6.2. MT2523D and MT2523S ball diagram .............................................................................................. 65

6.3. MT2523 series pins ........................................................................................................................... 68

6.4. MT2523 series pin multiplexing........................................................................................................ 79

7. System Configuration ........................................................................................................................... 84

7.1. System mode selection and trapping ............................................................................................... 84

8. Electrical Characteristics ....................................................................................................................... 85

8.1. Absolute maximum ratings ............................................................................................................... 85

8.2. Operating conditions ........................................................................................................................ 86

8.3. Communications interfaces .............................................................................................................. 95

8.4. Display controller ............................................................................................................................ 105

8.5. MIPI DBI TYPE-C interface characteristics ...................................................................................... 106