5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet

of

TITLE PAGE

RTL8211D/8211E

A3

16

Title

Size Document Number Rev

Date: Sheet of

TITLE PAGE

RTL8211D/8211E

A3

16

Title

Size Document Number Rev

Date: Sheet of

TITLE PAGE

RTL8211D/8211E

A3

16

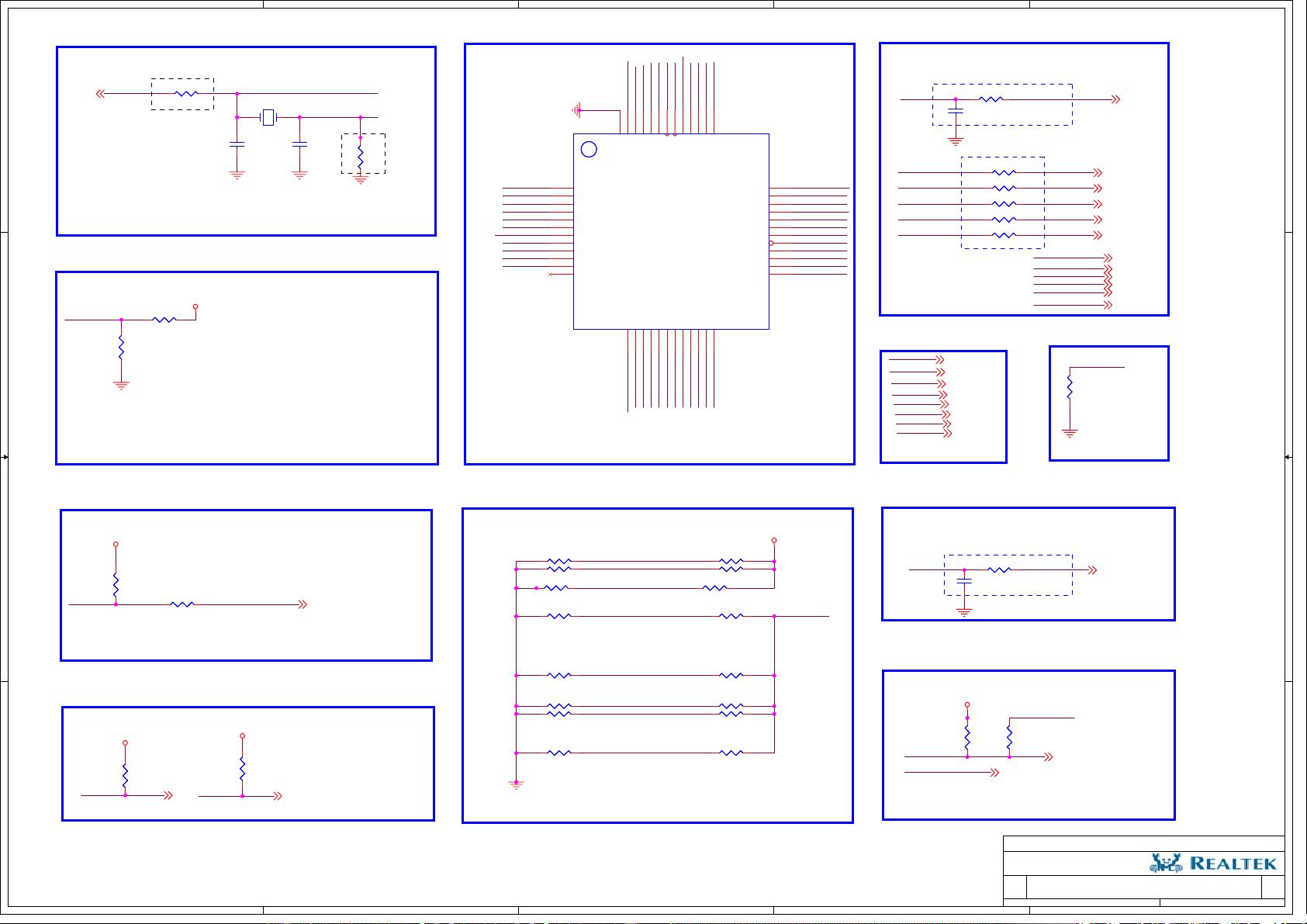

RTL8211D-VB/8211E-VB/8211E-VL Schematic

Page Index

1. Title Page

2. PHY

3. MDI

4. CMC

5. Power

6. History

REV.1.6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

RXD3_AN1

RXD2_N

RXD1_N

RXD0_SELRGV

RXD3_N

RXD2_AN0

RXD0_N

RXCTL_AD2 RXCTL_N

RXD1_TXDLY

LED0_AD0

LED1_AD1

RXD1_TXDLY

RX_CLK_N

RXD0_SELRGV

RXD3_AN1

RXD2_AN0

CLK25_N XTAL1

ENSWREG

MAC_RSTPHYRSTB

RSET

MDC

PMEB

INTB

RX_CLK

CLK125 CLK125_N

VDD33_VDD25

DVDD10

TXD0

RX_CLK

VDD33_VDD25

RXCTL_AD2

RXD2_AN0

TXD1

RXD0_SELRGV

TXCLK

VDD33_VDD25

RXD3_AN1

RXD1_TXDLY

LED2_RXDLY

MDC

PHYRSTB

MDIO

LED0_AD0

LED1_AD1

TXCTL

PMEB

TXD3

TXD2

MDI2-

MDI3-

MDI3+

AVDD10

MDI0-

AVDD33

MDI1-

AVDD10

MDI0+

MDI2+

MDI1+

GND

CLK125

AVDD33

VDDREG

ENSWREG

VDDREG

RSET

AVDD10

DVDD10

XTAL1

INTB

XTAL2

DVDD33

GND

MDIO

VDD33_VDD25

LED2_RXDLY

GND

RXCTL_AD2

REGOUT

XTAL2

DVDD33

AVDD33

DVDD33

DVDD33

DVDD33

DVDD33

RXCTL_N

RXD0_N

RXD1_N

RXD2_N

RXD3_N

RX_CLK_N

CLK25_N

MAC_RST

MDIO

MDC

PMEB

INTB

TXCTL

TXD0

TXD3

TXD2

TXD1

TXCLK

VDD33_VDD25

REGOUT

VDDREG

CLK125_N

DVDD33

AVDD33

DVDD10

AVDD10

VDD33

Title

Size Document Number Rev

Date: Sheet

of

PHY

RTL8211D/8211E

A3

26

Title

Size Document Number Rev

Date: Sheet of

PHY

RTL8211D/8211E

A3

26

Title

Size Document Number Rev

Date: Sheet of

PHY

RTL8211D/8211E

A3

26

R61,R62: Config for all capability

R51,R54: PHY Address=01(RTL8211D)

R51,R54,R148: PHY Address=001(RTL8211E)

R64,R50: Without TX/RX Delay

Place filter network close to RX_CLK.

Reserved for EMI

External clock and Crystal

External clock source from OSC or Chipset.

Connect ENSWREG to AVDD33 to enable

Switching regulator or connect ENSWREG

to GND to disable Switching regulator.

Enable/Disable SWREG

PHY Reset

For wake on LAN function, please keep PHYRSTB pin to high.

Enable SWREG: R75

Disable SWREG: R77

RSET

MDC/MDIO

WOL & Interrupt

Configuration Setting

Pull down for 2.5V RGMII(RTL8211D/8211E)

Pull up for 3.3V RGMII (RTL8211D/8211E)

Pull up1.5 /1.8V RGMII (RTL8211E-VL only)

RGMII Interface

Power

RTL8211D/8211E

Place filter network close to CLK125.

Reserved for EMI

Output Clock

R36 for RTL8211D

R147 for RTL8211E

PHYAD2 only for RTL8211E

If use external clock then the XTAL2 need connect to GND for RTL8211E.

R28 NC for RTL8211D

R52 4.7K(NC)R52 4.7K(NC)

R57 4.7KR57 4.7K

R39 0R39 0

R55

4.7K

R55

4.7K

R50

4.7K

R50

4.7K

R105 0R105 0

R54 4.7KR54 4.7K

R40 0R40 0

R32 0R32 0

R9

2.49K(1%)

R9

2.49K(1%)

R64 4.7KR64 4.7K

R59 4.7K(NC)R59 4.7K(NC)

R44 0R44 0

MDI[0]+

1

MDI[0]-

2

AVDD10

3

MDI[1]+

4

MDI[1]-

5

AVDD33

6

MDI[2]+

7

MDI[2]-

8

AVDD10

9

MDI[3]+

10

MDI[3]-

11

NC

12

RXCTL/PHYAD2

13

RXD0/SELRGV

14

DVDD33

15

RXD1/TXDLY

16

RXD2/AN0

17

RXD3/AN1

18

RXC

19

INTB

20

DVDD33

21

TXC

22

TXD0

23

TXD1

24

TXD2

25

TXD3

26

TXCTL

27

DVDD10

28

PHYRSTB

29

MDC

30

MDIO

31

LED2_RXDLY

32

PMEB

33

LED0/PHYAD0

34

LED1/PHYAD1

35

DVDD10

36

DVDD33

37

ENSWREG

38

RSET

39

AVDD10

40

AVDD33

41

CKXTAL1

42

VDDREG

45

CLK125

46

GND

47

REGOUT

48

CKXTAL2

43

VDDREG

44

GND(EPAD)

49

RTL8211D

RTL8211E

U7

RTL8211D

RTL8211E

U7

R65 4.7K(NC)R65 4.7K(NC)

R62 4.7KR62 4.7K

Y2

25MHz

Y2

25MHz

C19

22pF-NC

C19

22pF-NC

C6

27pF

C6

27pF

R27

4.7K

R27

4.7K

R60 4.7K(NC)R60 4.7K(NC)

R36

1.5K

R36

1.5K

R51 4.7KR51 4.7K

C8

27pF

C8

27pF

R33 0R33 0

R47 0R47 0

R87 4.7K(NC)R87 4.7K(NC)

R61 4.7KR61 4.7K

R75 0R75 0

C31

22pF-NC

C31

22pF-NC

R149 4.7K(NC)R149 4.7K(NC)

R49 0R49 0

R56 0 (NC)R56 0 (NC)

R77

0(NC)

R77

0(NC)

R28

0

R28

0

R148 4.7KR148 4.7K

R88 4.7K(NC)R88 4.7K(NC)

R147

1.5K

R147

1.5K

R106

4.7K

R106

4.7K

R53 4.7K(NC)R53 4.7K(NC)

评论7