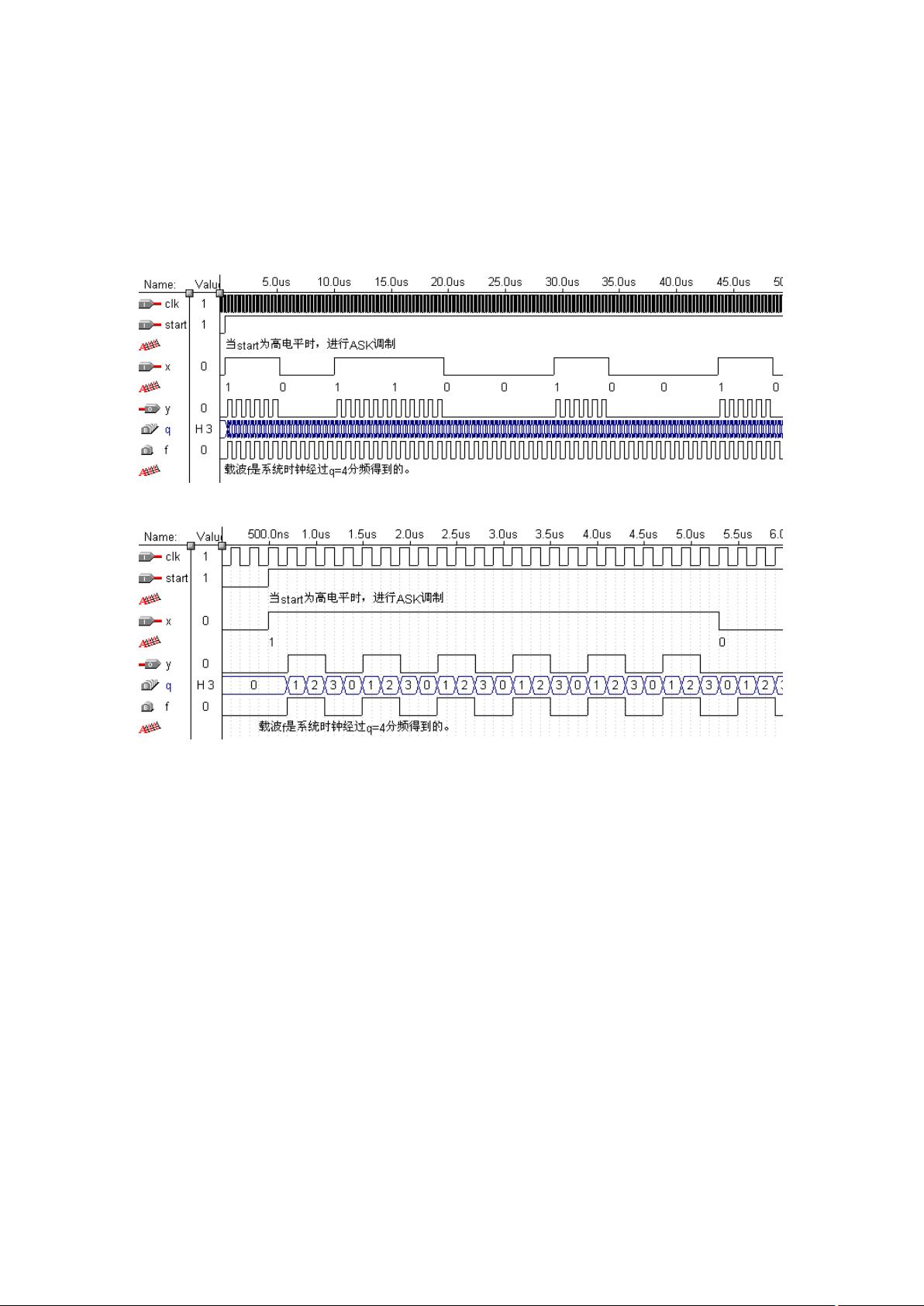

8.17 采用等精度测频原理的频率计的程序与仿真

--文件名:PLJ.vhd。

--功能:4 位显示的等精度频率计。

--最后修改日期:2004.4.14。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity PLJ is

port(clk:in std_logic; --基准时钟(10KHz)

tclk:in std_logic; --被测信号

start:in std_logic; --复位信号

alarm0,alarm1:out std_logic; --超量程,欠量程显示

dian:out std_logic_vector(3 downto 0); --小数点

data1:out integer range 0 to 9999); --频率数据

end PLJ;

architecture behav of PLJ is

signal q:integer range 0 to 9999; --预置闸门分频系数

signal q1:integer range 0 to 10000; --被测信号计数器

signal q2:integer range 0 to 20000; --基准信号计数器

signal en,en1:std_logic; --预置闸门,实际闸门

signal qq,qqq:integer range 0 to 200000000; --运算器

signal data0:integer range 0 to 9999; --频率数据中间信号

begin

process(clk) --此进程得到一个预置闸门信号

begin

if clk'event and clk='1' then

if start='1' then q<=0;en<='0';

elsif q=9999 then q<=9999;en<='0';

else q<=q+1;en<='1';

end if;

end if;

评论0