I

2

C-Master Core

Specification

Author: Richard Herveille

rherveille@opencores.org

Rev. 0.9

July 3, 2003

This page has been intentionally left blank

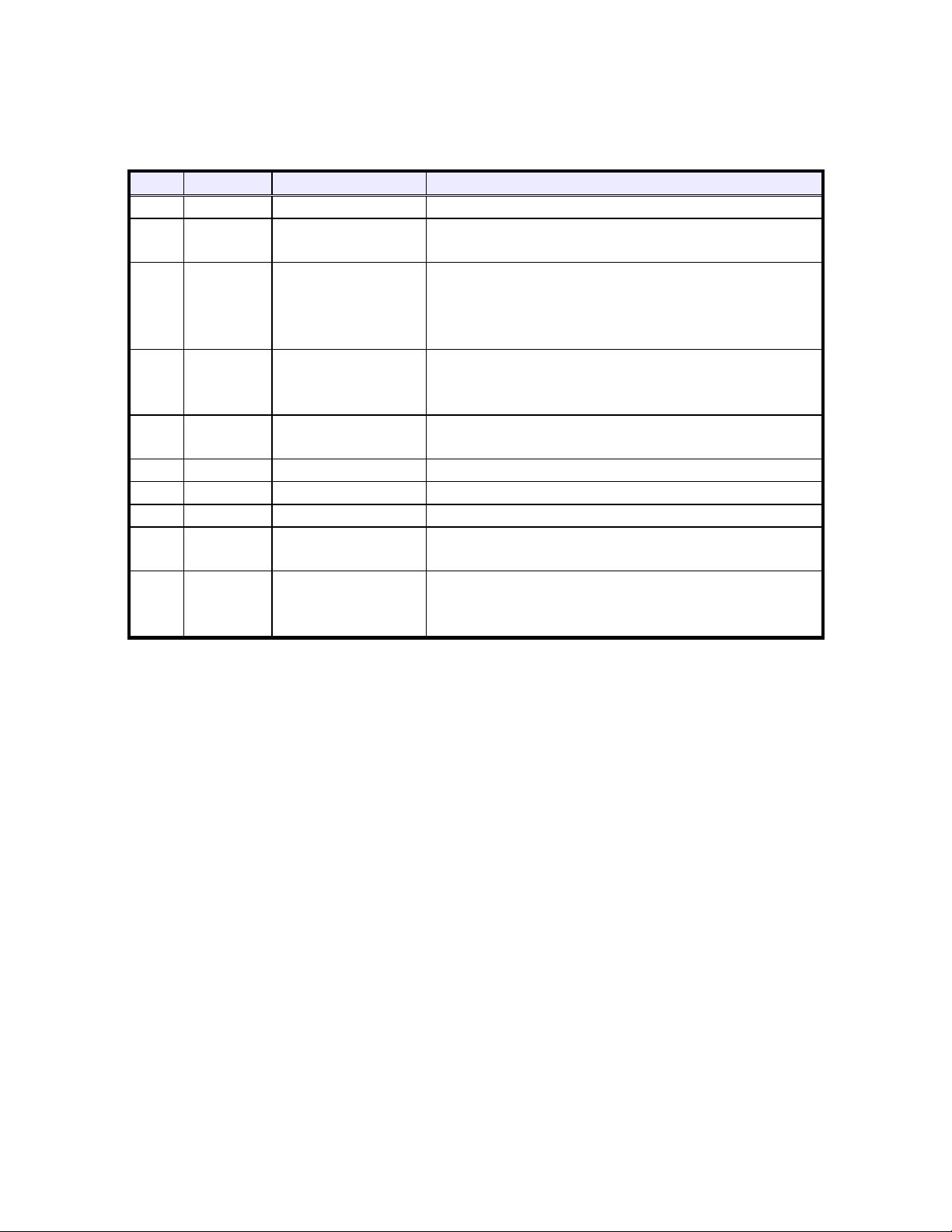

Revision History

Rev. Date Author Description

0.1 17/02/01 Richard Herveille First draft release

0.2 01/03/01 Richard Herveille Some cleaning up throughout the document

Added ‘Programming Examples’ section

0.3 Richard Herveille Added some comments after core-changes

- added BUSY bit (status register)

- changed I2C IO for ASIC support

- added comment for FGPA IO

0.4 10/19/01 Richard Herveille Changed core’s databus size to 8bit.

Changed documentation to reflect changes.

Changed port names to new naming convention.

0.5 18/02/02 Richard Herveille Changed table headers.

Added OpenCores logo.

0.5a 05/02/02 Richard Herveille Reviewed entire document.

0.6 21/03/02 Richard Herveille Added Appendix A, Synthesis Results

0.7 25/06/02 Richard Herveille Changed Prescale Register formula

0.8 30/12/02 Richard Herveille Added Multi-Master capabilities.

New timing diagrams.

0.9 03/07/03 Richard Herveille Changed ‘0x5C’ to ‘0xAC’ in Example1.

Changed ‘RW’ to ‘W’ in Command Register.

Changed ‘RW’ to ‘W’ in Transmit Register.

OpenCores I

2

C-Master core 7/3/2003

www.opencores.org Rev 0.8 Preliminary 1 of 15

1

Introduction

I

2

C is a two-wire, bi-directional serial bus that provides a simple and efficient method of

data exchange between devices. It is most suitable for applications requiring occasional

communication over a short distance between many devices. The I

2

C standard is a true

multi-master bus including collision detection and arbitration that prevents data

corruption if two or more masters attempt to control the bus simultaneously.

The interface defines 3 transmission speeds:

- Normal: 100Kbps

- Fast: 400Kbps

- High speed: 3.5Mbps

Only 100Kbps and 400Kbps modes are supported directly. For High speed special IOs

are needed. If these IOs are available and used, then High speed is also supported.

FEATURES

• Compatible with Philips I

2

C standard

• Multi Master Operation

• Software programmable clock frequency

• Clock Stretching and Wait state generation

• Software programmable acknowledge bit

• Interrupt or bit-polling driven byte-by-byte data-transfers

• Arbitration lost interrupt, with automatic transfer cancelation

• Start/Stop/Repeated Start/Acknowledge generation

• Start/Stop/Repeated Start detection

• Bus busy detection

• Supports 7 and 10bit addressing mode

• Operates from a wide range of input clock frequencies

• Static synchronous design

• Fully synthesizable

OpenCores I

2

C-Master core 7/3/2003

www.opencores.org Rev 0.8 Preliminary 2 of 15

2

IO ports

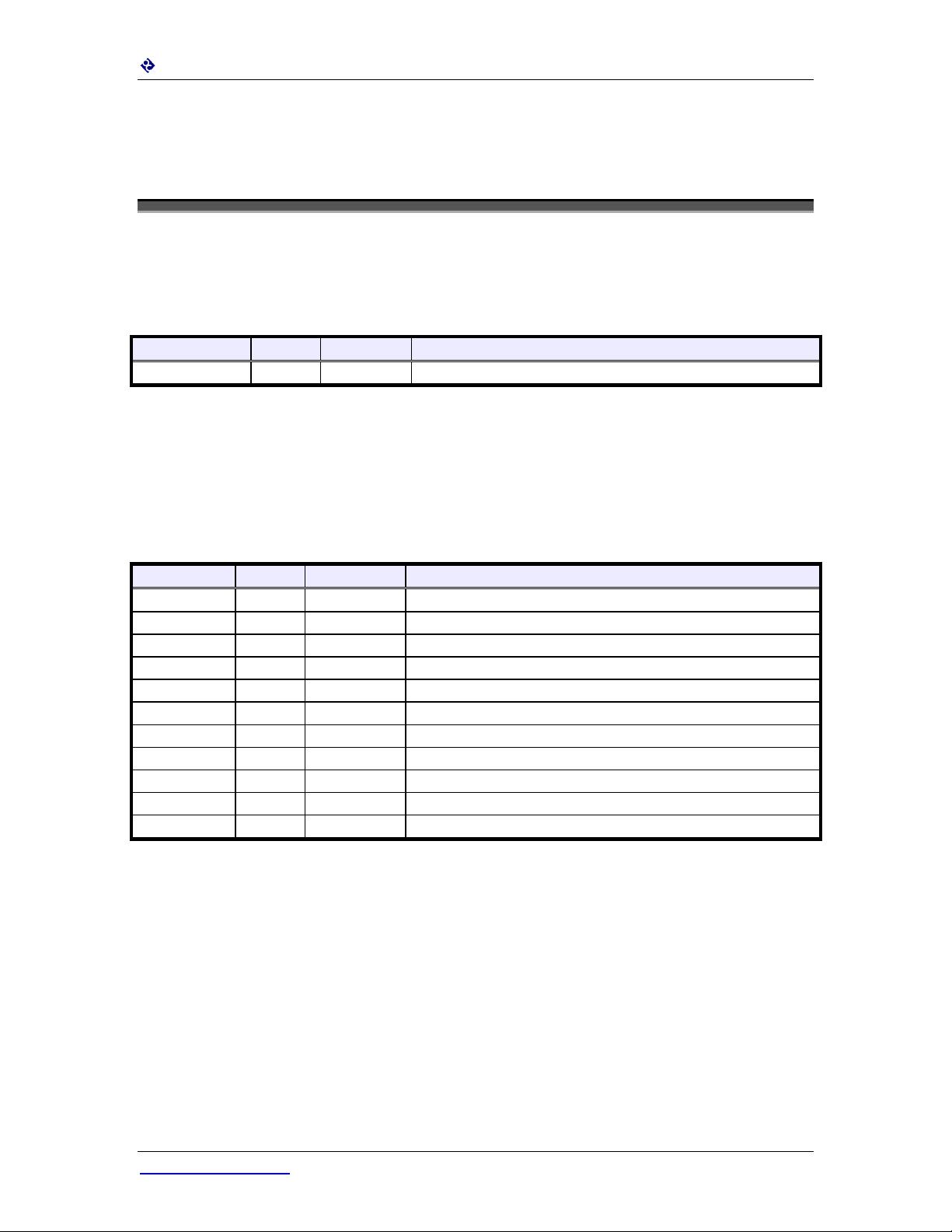

2.1 Core Parameters

Parameter Type Default Description

ARST_LVL Bit 1’b0 Asynchronous reset level

2.1.1 ARST_LVL

The asynchronous reset level can be set to either active high (1’b1) or active low (1’b0).

2.2 WISHBONE interface signals

Port Width Direction Description

wb_clk_i 1 Input Master clock

wb_rst_i 1 Input Synchronous reset, active high

arst_i 1 Input Asynchronous reset

wb_adr_i 3 Input Lower address bits

wb_dat_i 8 Input Data towards the core

wb_dat_o 8 Output Data from the core

wb_we_i 1 Input Write enable input

wb_stb_i 1 Input Strobe signal/Core select input

wb_cyc_i 1 Input Valid bus cycle input

wb_ack_o 1 Output Bus cycle acknowledge output

wb_inta_o 1 Output Interrupt signal output

The core features a WISHBONE RevB.3 compliant WISHBONE Classic interface. All

output signals are registered. Each access takes 2 clock cycles.

arst_i is not a WISHBONE compatible signal. It is provided for FPGA implementations.

Using [arst_i] instead of [wb_rst_i] can result in lower cell-usage and higher

performance, because most FPGAs provide a dedicated asynchronous reset path. Use

either [arst_i] or [wb_rst_i], tie the other to a negated state.