The GH VHDL Library

An

www.OpenCores.org

Project

ghuber@opencores.org

gh_vhdl_lib@yahoo.com

The GH VHDL Library

Revision 3.48 ii 7 March 2009

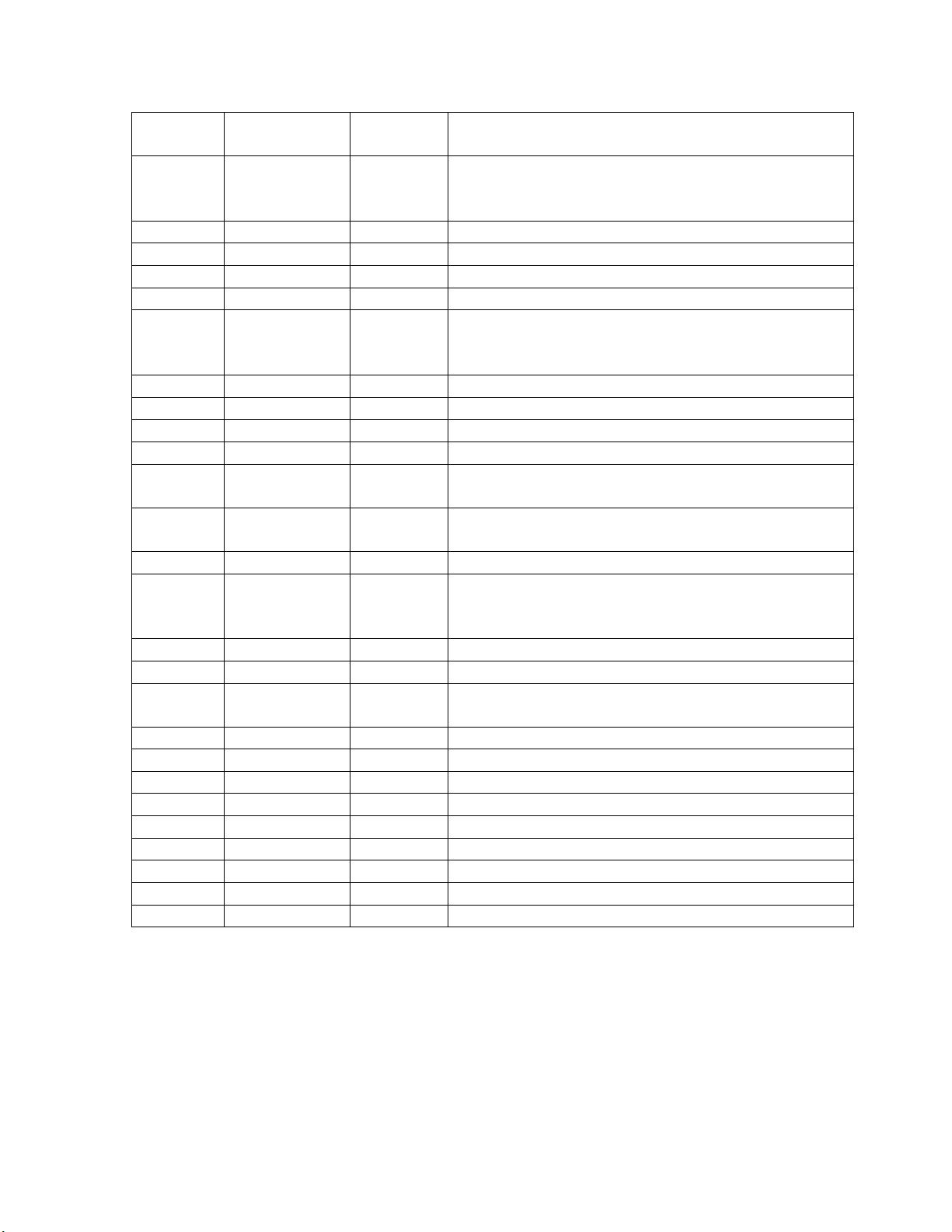

Revision History

Revision Date Author Description

1.0 3 Sept 2005 G Huber Initial Revision

1.1 10 Sept 2005 G Huber Add parts, fix some typo’s

2.0 17 Sept 2005 H LeFevre

1. Add LFSR’s

2. Add gh_ prefix to the name of some parts.

(See chapter 4 for explanation on this change)

3 Mod parts to use gh_ parts (where required)

2.1 18 Sept 2005 G Huber Add decoder/mux, clock divider, and NCO

2.2 24 Sept 2005 S A Dodd Add pulse generator

2.3 1 Oct 2005 G Huber Add sweep generator

2.4 4 Oct 2005 H LeFevre

Add Random Number Generator/CASR

3.0 8 Oct 2005 G Huber Reorganize library,

add a couple of shift registers

3.1 15 Oct 2005 S A Dodd Add parity generator, FIFO’s, integer counters

3.2 23 Oct 2005 G Huber Add programmable LFSR’s

3.3 29 Oct 2005 G Huber Add Configuration Registers

3.4 13 Nov 2005 S A Dodd,

G Huber

Add some memory parts

3.5 14 Jan 2006 G Huber Add delay lines

3.6 21 Jan 2006 S A Dodd

G Huber

Add Control Registers

Add a fixed delay line for a bus

3.7 28 Jan 2006 H LeFevre

Add a baud rate generator

3.8 4 Feb 2006 S A Dodd

H LeFevre

Add FIFO with sync clear

Add an In Place Multiplier

3.9 11 Feb 2006 H LeFevre

G Huber

Add two more In Place Multipliers (one has both

inputs unsigned and the other both inputs are

signed)

Add another shift register (shifts left)

3.10 18 Feb 2006 G Huber Add another shift register (also shifts left)

Finished adding the gh_ prefix to all parts

3.11 25 Mar 2006 H LeFevre

S A Dodd

Add one more In Place Multiplier

Mod gh_sincos to use Cordic + 45

3.12 13 May 2006 S A Dodd Add FIR Filter

3.13 26 May 1006 G Huber Add debounce, stretch low

3.14 16 Sept 2006 G Huber Add a counter, 18 bit multipliers

3.15 23 Sept 2006 SA Dodd Add complex math parts

3.16 23 Dec 2006 H LeFevre

Replace async FIFO (to use gray code)

3.17 27 Dec 2006 G Huber

HL/SD

Add Gray code converters

Update FIFO’s

3.18 13 Jan 2007 H LeFevre

add async FIFO’s with ¼. ½, and ¾ full flags

3.19 27 Jan 2007 SA Dodd add digital attenuator

3.20 3 Feb 2007 H LeFevre

add parallel FIR Filter

3.21 10 Feb 2007 H LeFevre

add FIR Filters of odd order, negative symmetry

The GH VHDL Library

Revision 3.48 iii 7 March 2009

3.22 9 June 2007 G Huber

SA Dodd

add programmable delay bus, FASM dual port Ram

with reset, 3 multipliers with generics

3.23 30 June 2007 H LeFevre

G Huber

add 2 in-place multipliers, with all data bits out

add MAC with full generics and an unsigned array

divider

3.24 15 July 2007 S A Dodd add a FIR filter and Pulse time/width module

3.25 12 Aug 2007 S A Dodd mod/add filter

3.26 16 Aug 2007 S A Dodd add (two clock multiply) complex multipliers

3.27 14 Oct 2007 H LeFevre

add some filters w/o multipliers

3.28 21 Oct 2007 S A Dodd

G Huber

Add rev A of rectangular to polar (CORDIC

application) – increases pipelining

add 4 byte memory

3.29 22 Nov 2007 H LeFevre

add VMEbus Slave Interface Module parts

3.30 25 Nov 2007 H LeFevre

add FIR filter, rev A for NCO

3.31 8 Dec 2007 G Huber add VME read Modules

3.32 30 Dec 2007 H LeFevre

add 3 multiplier complex multipliers

3.33

3.33a

3 May 2008

4 May 2008

H LeFevre

Add random number scalar (serial multiplier)

Add random number scalar (parallel multiplier)

3.34 24 May 2008 H LeFevre

Add two asynchronous fifo’s (with UART style

flags)

3.35 27 May 2008 G Huber Add programmable delay line using generics

3.36 1 June 2008 S A Dodd

3 complex multipliers, with an extra register

delay for higher operating frequency

Data Mux(2:1) /DeMux (1:2) set

3.37 4 July 2008 G Huber Add some NCO type accumulators

3.38 1 Sept 2008 H LeFevre

Add versions of a couple frequency syntheses parts

3.39 20 Sept 2008 H LeFevre

Add programmable Stretch parts, add init to some

of the memory parts

3.40 27 Sept 2008 H LeFevre

Add 4 byte GPIO

3.41 04 Oct 2008 H LeFevre

Add Burst Generator

3.42 11 Oct 2008 H LeFevre

Add CORDIC’s with 28 bit atan functions

3.43 26 Oct 2008 H LeFevre

Add Sin Cos ROM’s

3.44 1 Nov 2008 H LeFevre

Add Sin Cos ROM’s with quarter size tables

3.45 8 Nov 2008 H LeFevre

Add config registers (3072, 4096 bits), fix notes

3.46 25 Jan 2009 H LeFevre

Add watch dog timers

3.47 28 Feb 2009 H LeFevre

Add Pulse Width Modulator

3.48 7 Mar 2009 H LeFevre

Add NCO’s that use Lookup tables for nsin/cos

The GH VHDL Library

Revision 3.48 iv 7 March 2009

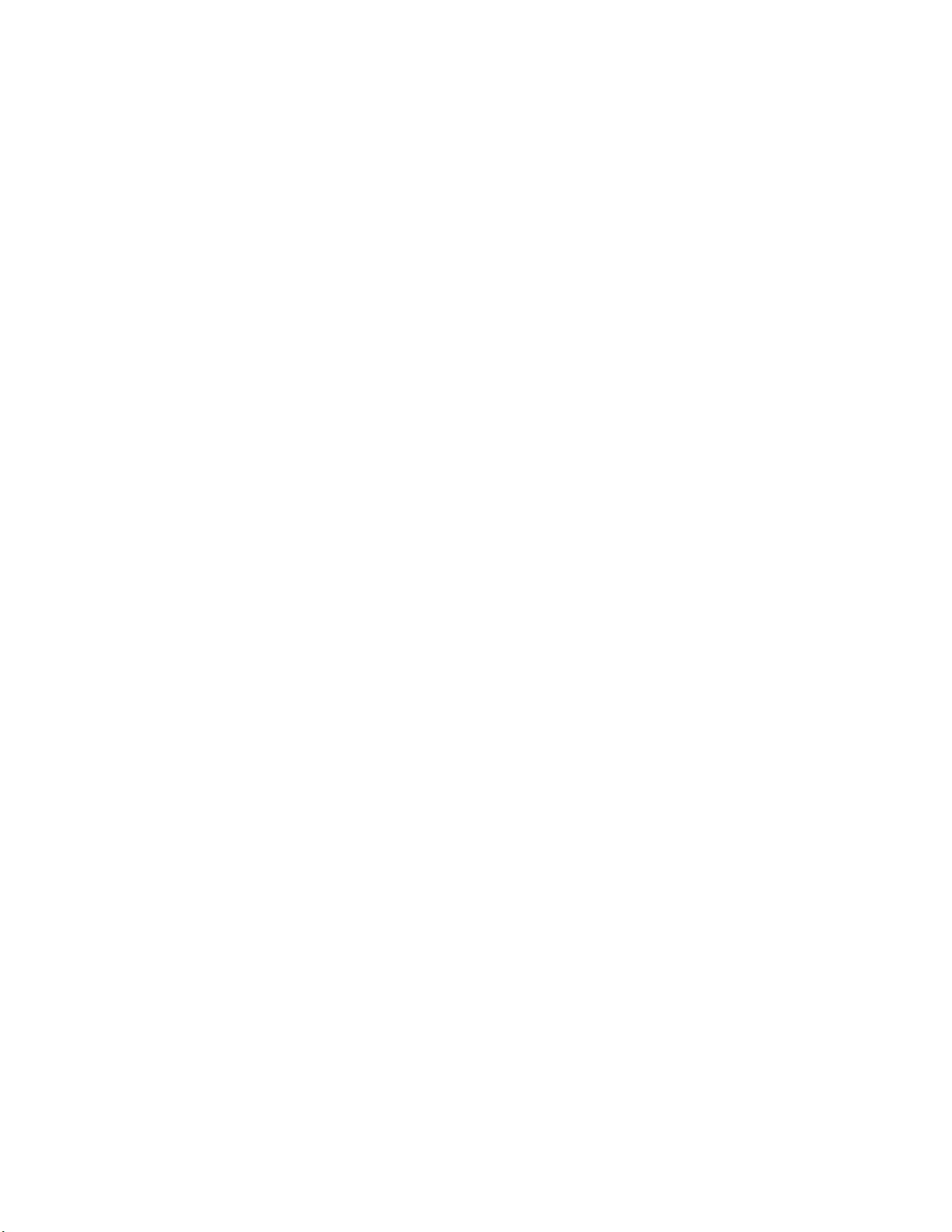

Table of Contents

1 Introduction................................................................................................................. 1

1.1 Purpose................................................................................................................ 1

1.2 What the Library is Not ...................................................................................... 1

1.3 GH VHDL License ............................................................................................. 1

2 Basic Registers and Gates........................................................................................... 3

2.1 D Flip Flop.......................................................................................................... 3

2.2 JK Flip Flop ........................................................................................................ 3

2.3 Basic Register and Latch .................................................................................... 4

2.4 XOR Bus............................................................................................................. 4

2.5 Comparators........................................................................................................ 5

2.6 Decoders ............................................................................................................. 6

2.7 Multiplexers........................................................................................................ 6

2.8 Shift Registers..................................................................................................... 7

2.9 Four Byte Configuration Registers ..................................................................... 8

3 Counters...................................................................................................................... 9

3.1 Binary Counters .................................................................................................. 9

3.2 Modulo Counter................................................................................................ 10

3.3 Integer Counters................................................................................................ 10

4 Custom MSI Parts..................................................................................................... 11

4.1 Pulse Stretcher .................................................................................................. 11

4.2 Edge Detector.................................................................................................... 12

4.3 Clock Divider.................................................................................................... 12

4.4 Pulse Generator................................................................................................. 13

4.5 Parity Generator................................................................................................ 13

4.6 Delay Lines....................................................................................................... 14

4.7 Baud Rate Generator......................................................................................... 15

4.8 Control Registers .............................................................................................. 16

4.9 A Switch de-bouncer......................................................................................... 17

4.10 An Edge Detector for changing Clock Domains .............................................. 17

4.11 Gray code converters ........................................................................................ 18

4.12 Pulse Width/Time Measurement....................................................................... 18

4.13 Lower Rate Clock Mirror.................................................................................. 19

4.14 Data DeMux 1 to 2............................................................................................ 19

4.15 Data Mux 2 to 1 ................................................................................................ 20

4.16 Four Byte GPIO................................................................................................ 20

4.17 Burst Generator................................................................................................. 21

4.18 Watch Dog Timers............................................................................................ 22

4.19 Pulse Width Modulator..................................................................................... 22

5 Math Functions ......................................................................................................... 24

5.1 Accumulator...................................................................................................... 24

5.2 Multipliers......................................................................................................... 24

5.3 Multipliers using Generics................................................................................ 25

5.4 Multiplier Accumulator .................................................................................... 25

5.5 Random Number Generation ............................................................................ 26

The GH VHDL Library

Revision 3.48 v 7 March 2009

5.5.1 The Linear Feedback Shift Register (LFSR) ............................................ 26

5.5.2 CASR and Random Number Generator.................................................... 27

5.5.3 Programmable LFSR’s.............................................................................. 28

5.5.4 Random Number Scalars .......................................................................... 29

5.6 In Place Multipliers........................................................................................... 30

5.7 Unsigned Array Divider.................................................................................... 31

5.8 Complex Math .................................................................................................. 32

5.9 Digital Attenuator ............................................................................................. 34

6 Memory..................................................................................................................... 35

6.1 Synchronous RAM............................................................................................ 35

6.2 FIFO’s............................................................................................................... 36

6.2.1 Synchronous FIFO.................................................................................... 36

6.2.2 Asynchronous FIFO.................................................................................. 37

6.2.3 Asynchronous FIFO’s with UART Style Flags........................................ 38

6.3 Four Byte Dual Port RAM................................................................................ 39

7 Frequency Synthesis ................................................................................................. 40

7.1 The DDS (also known as the NCO, or DCO)................................................... 40

7.1.1 NCO Style Accumulators ......................................................................... 41

7.2 Sweep Generator............................................................................................... 42

7.2.1 Simulation of the Sweep Generator.......................................................... 45

7.3 CORDIC Rotation Algorithm........................................................................... 46

7.3.1 Theory of the CORDIC............................................................................. 47

7.3.2 Applications for the CORDIC .................................................................. 49

7.4 Sin Cos ROM Lookup Tables........................................................................... 50

8 Filters ........................................................................................................................ 51

8.1 CIC Filter .......................................................................................................... 51

8.2 Time–Varying Fractional Delay Filters............................................................ 54

8.2.1 The Lagrange Interpolator ........................................................................ 54

8.2.2 Time–Varying Control.............................................................................. 55

8.2.3 TVFD Application Notes.......................................................................... 55

8.3 A single MAC FIR Filter.................................................................................. 56

8.4 Symmetrical, parallel FIR Filters...................................................................... 57

8.4.1 FIR Filter Architecture.............................................................................. 58

8.5 FIR Filters Without Multipliers ........................................................................ 59

9 VMEbus [VXIbus] Interface Modules...................................................................... 60

9.1 VME Slave Modules......................................................................................... 61

9.2 VME Chip Select Modules ............................................................................... 63

9.3 VME Read Modules ......................................................................................... 63

10 Library Notes ........................................................................................................ 64