利用 DC 进行逻辑综合

一.综合流程以及约束的编写:

一般来说,集成电路的设计过程可分为前端设计(front end)和后端设计

(back end)两个阶段。在前端设计阶段,根据用户需求,确定设计所要实现的

功能和时序,并确定出具体的数字逻辑电路(schematic);在后端设计阶段,由

电路逻辑图产生相应的电路版图(layout)。

1.1概述

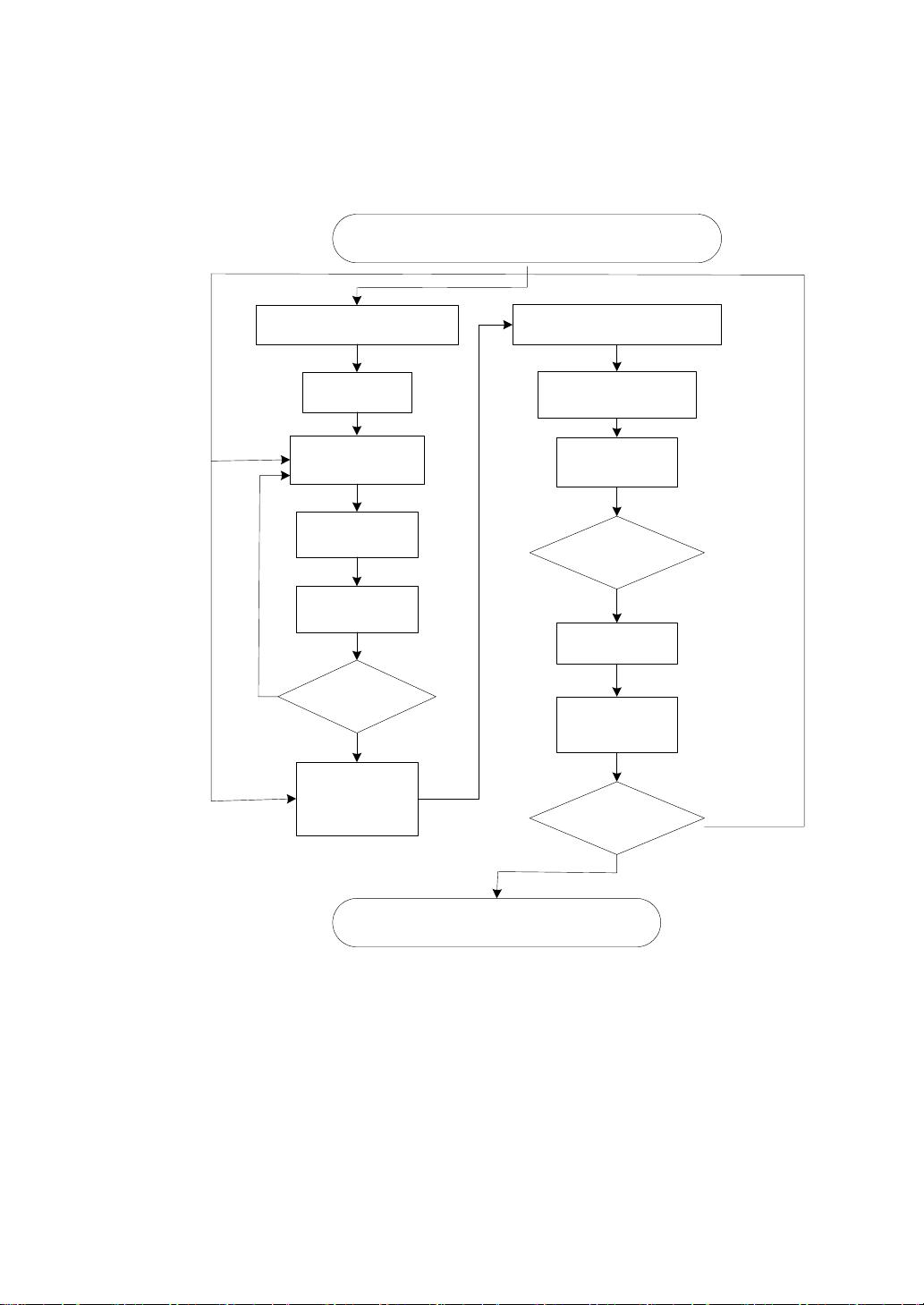

芯片综合的过程:芯片的规格说明,芯片设计的划分,预布局,RTL 逻辑单元的

综合,各逻辑单元的集成,测试,布局规划,布局布线,最终验证等步骤。设计

流程与思想概述:一个设计从市场需求到实际应用需要运用工程的概念和方法加

以实现,这需要工程人员遵循一定的规则按一定的设计步骤进行操作。下面我们

给出了一个设计工程通常的工作步骤(请参见设计流程图)。从图中可以看出对

一个完整的设计流程来说,可以将工作划分为两个阶段:前段设计和后端设计。

前端工作主要完成 IC 与通讯整机设计接口问题,以及整个 IC 的内部总体结构设

计;而后端工作则主要是在前段设计的基础上,使用 EDA 工具,遵循设计流程,

完成整个 IC 设计。

1.1.1 逻辑综合简介

综合就是将设计的原始思想转化为可大规模生产的并可以执行预期功能的

器件这一过程。长期以来,硬件描述语言(HDL)只是用于逻辑验证, 设计者不

得不手工将 HDL 代码转化为逻辑图并且画出组件间的互连线用以产生门级网表。

随着综合工具的改进,这些手工操作渐渐由工具替代了,设计人员可以由工具自

动完成 HDL 代码到门级网表的转化,这项工作就是综合。

设计的抽象层级依次为:原始设计思想、器件的功能描述、设计的行为级

描述、寄存器传输级(RTL)、门级网表、物理设备。

综合的益处有以下几点:可以提高工作效率、代码可复用性(可以通过使

用参数化代码、构建好的逻辑块、重新定位新库等手段达到目的)、可验证性、

可以更加抽象等等。

综合是由约束来驱动的。

①环境属性约束:PVT,线负载模型、模式。

②设计规则约束:面积,扇出,驱动,负载。

③时序约束。

评论0