IMX8MDQLQCEC.zip_embedded

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

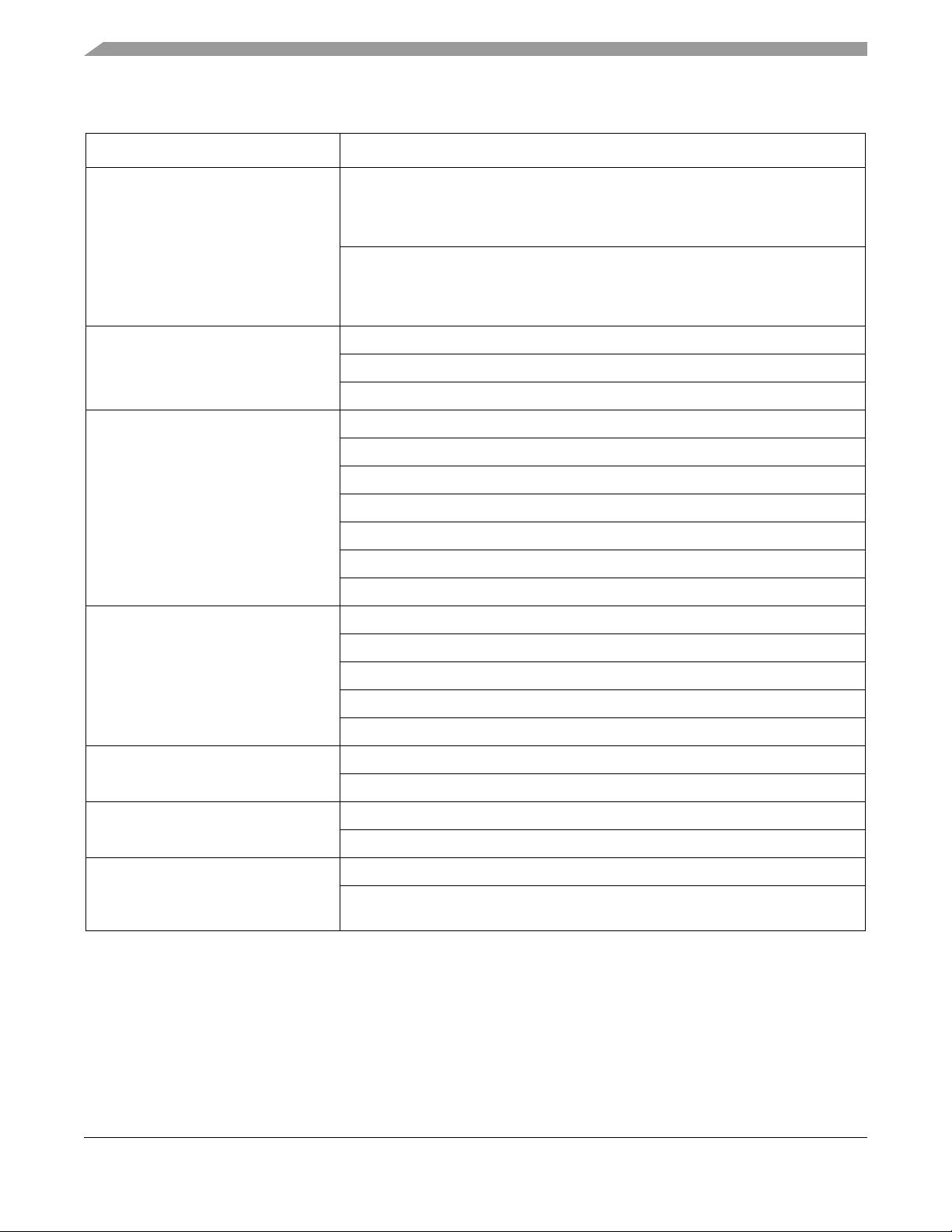

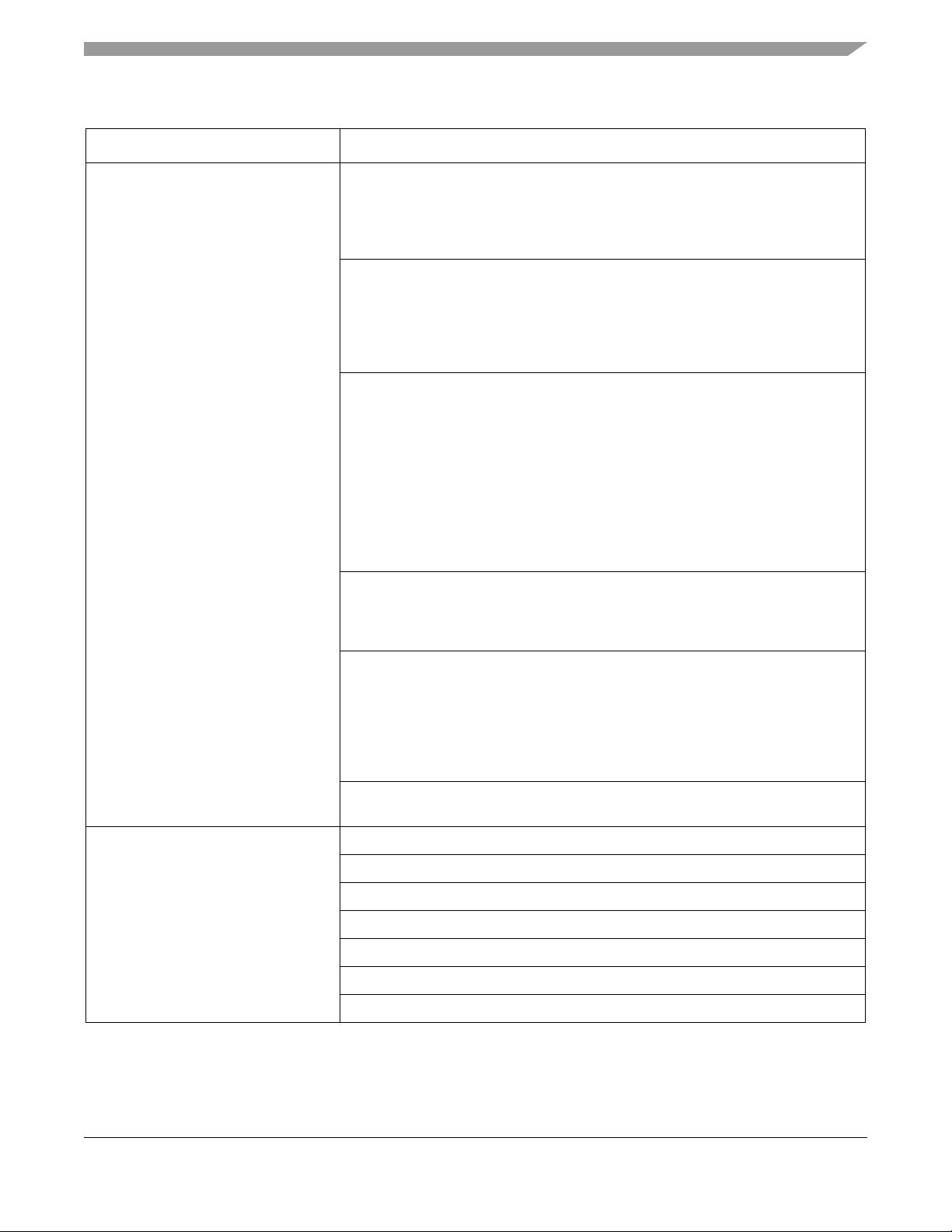

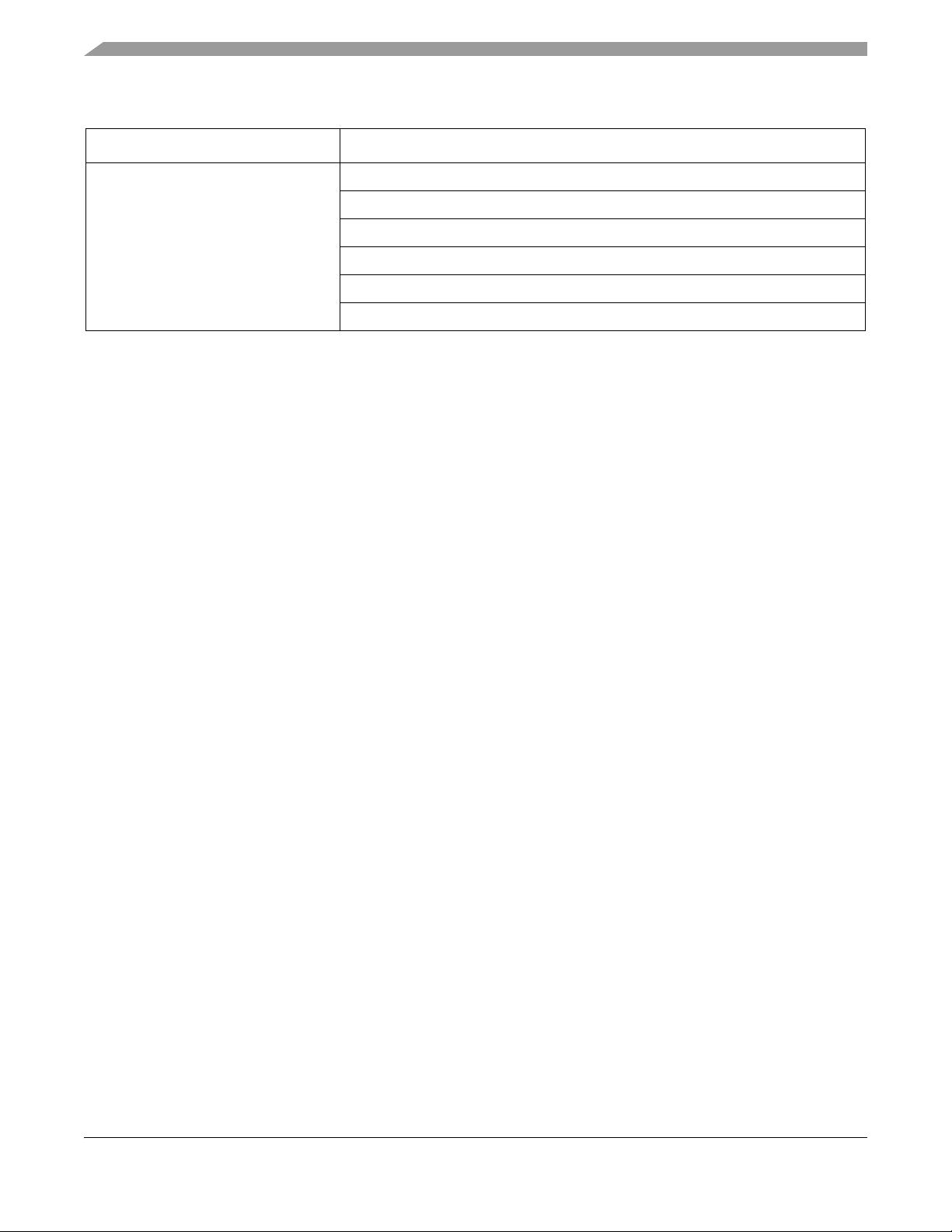

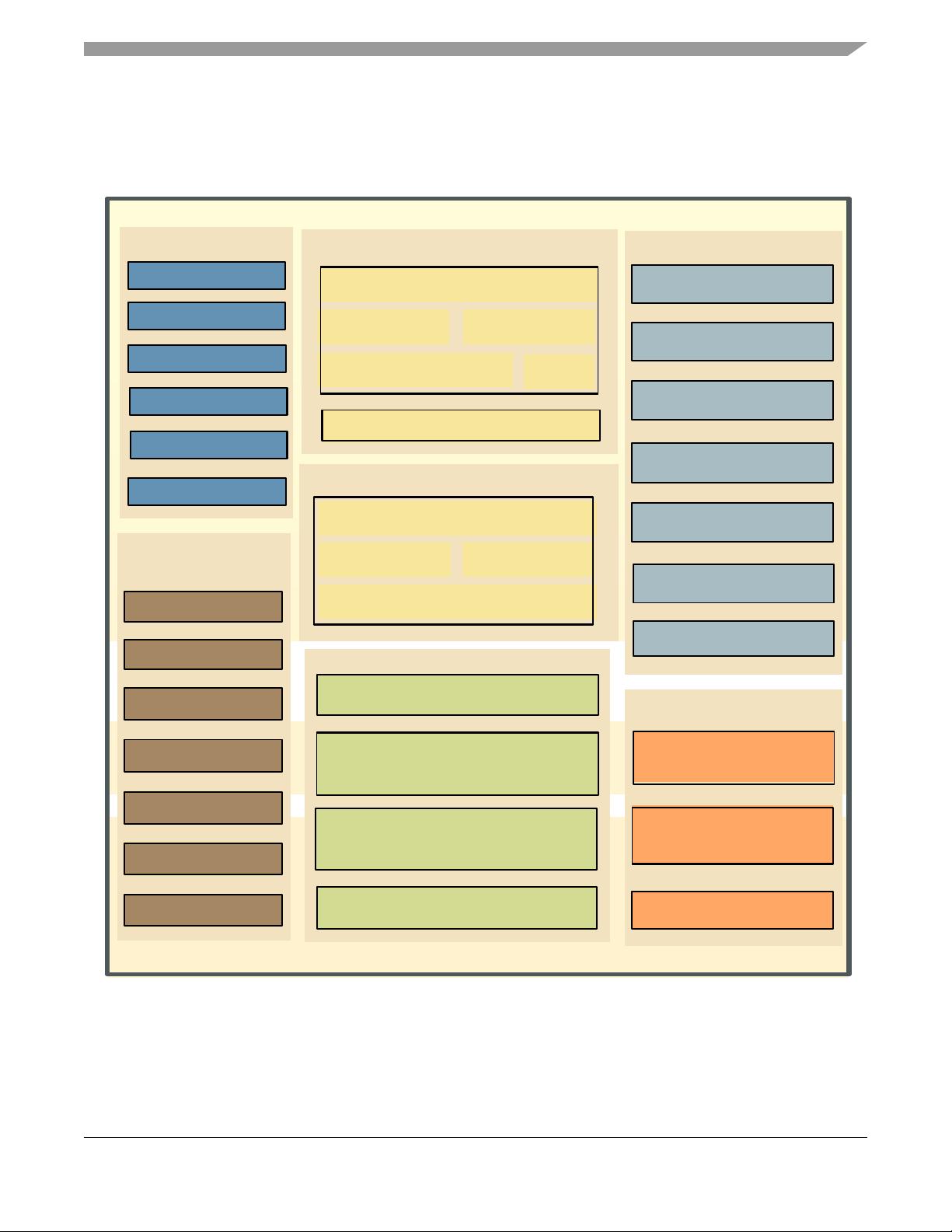

标题中的"IMX8MDQLQCEC.zip.Embedded"提到了一款嵌入式处理器的资料包,其中包含了NXP的i.MX 8M系列的Dual、Quad Lite和Quad应用处理器的数据表,主要面向消费类产品。这个压缩包里的关键文件是"IMX8MDQLQCEC.pdf",我们可以期待它提供了关于这些处理器的详细技术规格和信息。 嵌入式系统是设计用于特定功能的计算机系统,通常集成在更大的设备中,如智能家居设备、汽车电子系统或工业自动化设备。i.MX 8M系列是NXP半导体公司推出的高性能、低功耗的应用处理器,适用于各种嵌入式应用。 i.MX 8M Dual、8M Quad Lite和8M Quad处理器都是基于ARM架构的,具有多核处理能力。"Dual"指的是双核配置,而"Quad"则表示四核配置。"Lite"版本可能是在性能或功耗方面进行了优化,以适应对成本敏感或电源限制的项目。 这些处理器的核心特性可能包括: 1. **处理器核心**: 可能包括ARM Cortex-A53 CPU,这是一种高效能、低功耗的64位处理器核心,适合运行复杂的操作系统和应用程序。 2. **图形处理单元(GPU)**: i.MX 8M系列可能配备了ARM Mali GPU,用于图形渲染和多媒体处理,支持高清视频播放和现代UI的流畅显示。 3. **多媒体加速器**: 为了增强多媒体处理能力,NXP的i.MX 8M系列可能会包含硬件编解码器,支持多种视频格式,如H.264、H.265(HEVC)和VP9。 4. **连接性**: 针对嵌入式应用,处理器可能集成了Wi-Fi、蓝牙和以太网接口,方便设备联网。 5. **安全性**: 为了保护数据和应用,i.MX 8M系列可能内置了安全功能,如加密引擎和安全岛,符合物联网(IoT)的安全标准。 6. **内存和I/O**: 这些处理器将支持高速内存接口,如LPDDR4,并提供多种I/O接口,如SPI、I2C、GPIO、UART等,便于连接外围设备。 7. **电源管理**: 为了适应不同应用的电源需求,i.MX 8M系列可能具有精细的电源管理单元,实现动态电压和频率调整。 8. **开发工具和支持**: NXP通常会提供开发板、软件开发工具链以及全面的文档,帮助开发者快速进行产品原型设计和软件开发。 "Data Sheet"是技术文档,详细描述了这些处理器的电气特性、引脚定义、操作条件、性能参数以及应用注意事项等内容。对于系统设计师和硬件工程师来说,它是选择和使用这些处理器的关键参考资料。通过阅读这份数据表,可以深入了解如何根据具体项目需求来选择合适的处理器型号,以及如何进行硬件设计和软件优化。

IMX8MDQLQCEC.zip (1个子文件)

IMX8MDQLQCEC.zip (1个子文件)  IMX8MDQLQCEC.pdf 1.77MB

IMX8MDQLQCEC.pdf 1.77MB- 1

- 粉丝: 94

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Python+SQL Server的实验室管理系统python数据库管理系统

- 离线xml转json的html代码

- springboot学生综合测评系统 PPT

- 油雾分离器工程图机械结构设计图纸和其它技术资料和技术方案非常好100%好用.zip

- hadoop-大数据技术中的Hadoop架构与应用解析

- CH340系列PDF数据手册

- IMG_20241225_103252.jpg

- 批量调整表格的行高Python实现源代码(不存在多行合并)

- silvaco学习资料!

- 职工工资表接近满分作业包含所有源文件

- 不同操作系统上tomcat安装与配置教程指南

- 纯js实现国密算法:sm2,sm3,sm

- 安卓源码,安卓开发,跑步打卡项目app源码,包括源码和简单文档

- selenium自动化测试工具详解:核心组件、编程语言支持及应用场景

- 大数据架构初步规划与应用

- 代码审核管理规范1.0

信息提交成功

信息提交成功