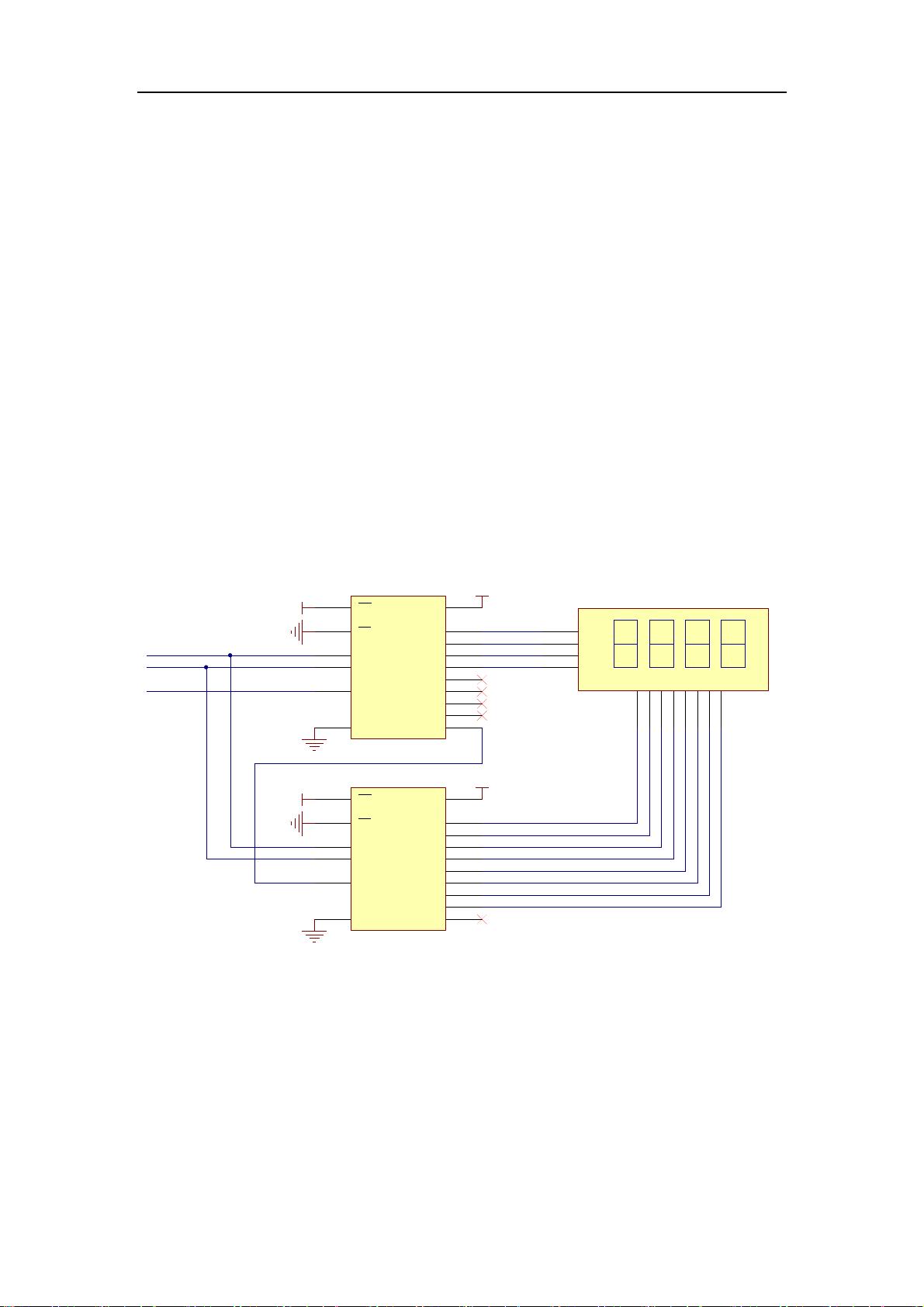

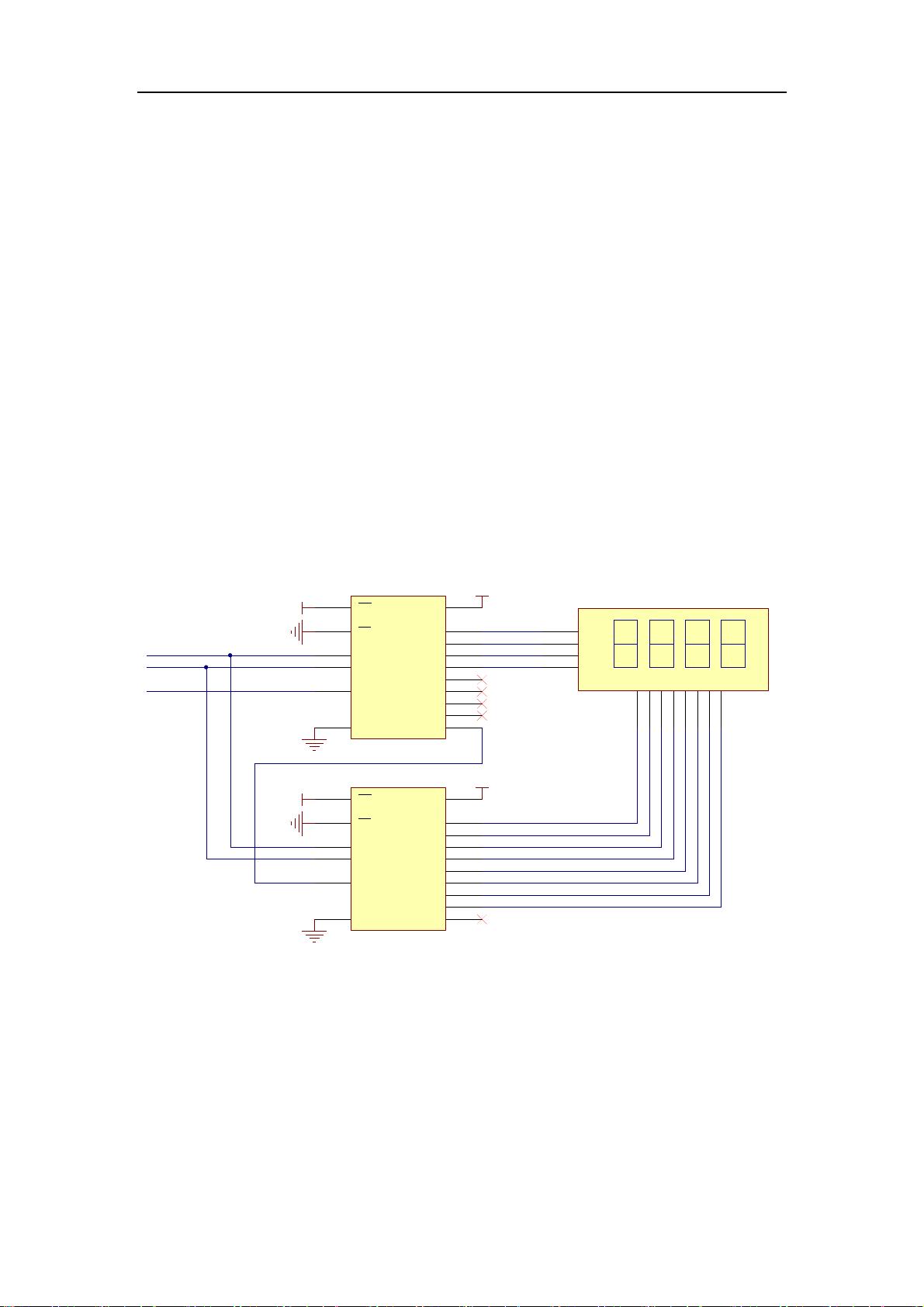

在电子设计领域,FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它允许用户根据需求自定义硬件电路。本实验“ex2_seg7.rar”专注于使用FPGA来控制七段数码管的显示,这对于理解和实践数字系统设计至关重要。七段数码管是一种常见的显示设备,常用于各种仪表、计数器和时钟等,它通过七段的亮或灭组合来显示0-9的数字。 VHDL(VHSIC Hardware Description Language)是用于描述数字系统的硬件描述语言之一,它可以用来定义电路的行为和结构。在本实验中,我们将使用VHDL编写代码来控制数码管的各个段,实现数字的动态显示。VHDL代码通常包括实体(entity)、结构体(architecture)和过程(process)等部分,实体描述接口,结构体则描述其内部工作原理。 数码管的控制主要涉及段驱动和位驱动。段驱动是指控制每个独立的七段,这通常通过译码器实现,将二进制数据转换为对应的段选信号。位驱动则是选择要显示的数码管,如果有多个数码管并联,可以通过简单的开关电路或者多路选择器来实现。 在FPGA中实现数码管显示,首先需要创建一个VHDL模块,该模块的输入可能包括要显示的数字以及任何控制信号,如扫描频率。输出则是七段数码管的段驱动信号。在VHDL代码中,可以定义一个数组来表示数码管的七段,然后通过逻辑操作(如AND、OR、NOT)来生成对应的段选和位选信号。 在实验过程中,你可能需要理解以下概念: 1. 译码:将数字编码转换为特定的输出,如七段译码。 2. 循环移位寄存器:用于实现数码管的动态扫描,提高显示效果。 3. 时序控制:控制数码管的亮灭时间,以达到视觉上的连续显示。 4. 锁存器和触发器:存储当前显示的数字。 5. FPGA I/O接口:了解如何将FPGA的输入/输出引脚连接到数码管。 在压缩包“ex2_seg7.rar”中,包含了实现这一功能的具体代码和可能的仿真文件。通过分析和运行这些文件,你可以深入理解FPGA如何与数码管交互,以及VHDL如何描述这种交互。实践中,你可能需要在开发环境中加载配置文件到FPGA,然后观察实际的数码管显示效果,以验证你的设计是否正确。 这个实验提供了一个很好的平台,让你能够亲手实现一个实际的数字系统,同时加深对FPGA、VHDL和数码管显示原理的理解。通过这个项目,你不仅能掌握基本的硬件描述语言编程技巧,还能增强数字逻辑设计的能力。

ex2_seg7.rar_FPGA 数码管_VHDL数码管_fpga数码管_数码管 (418个子文件)

ex2_seg7.rar_FPGA 数码管_VHDL数码管_fpga数码管_数码管 (418个子文件)  _info 31KB

_info 31KB seg7_global_asgn_op.abo 131KB

seg7_global_asgn_op.abo 131KB verilog.asm 1.91MB

verilog.asm 1.91MB verilog.asm 909KB

verilog.asm 909KB verilog.asm 823KB

verilog.asm 823KB verilog.asm 737KB

verilog.asm 737KB verilog.asm 736KB

verilog.asm 736KB verilog.asm 732KB

verilog.asm 732KB verilog.asm 636KB

verilog.asm 636KB verilog.asm 630KB

verilog.asm 630KB verilog.asm 579KB

verilog.asm 579KB verilog.asm 526KB

verilog.asm 526KB verilog.asm 467KB

verilog.asm 467KB verilog.asm 455KB

verilog.asm 455KB verilog.asm 452KB

verilog.asm 452KB verilog.asm 269KB

verilog.asm 269KB verilog.asm 258KB

verilog.asm 258KB verilog.asm 234KB

verilog.asm 234KB verilog.asm 197KB

verilog.asm 197KB verilog.asm 196KB

verilog.asm 196KB verilog.asm 191KB

verilog.asm 191KB verilog.asm 186KB

verilog.asm 186KB verilog.asm 157KB

verilog.asm 157KB verilog.asm 147KB

verilog.asm 147KB verilog.asm 141KB

verilog.asm 141KB verilog.asm 139KB

verilog.asm 139KB verilog.asm 138KB

verilog.asm 138KB verilog.asm 134KB

verilog.asm 134KB verilog.asm 130KB

verilog.asm 130KB verilog.asm 124KB

verilog.asm 124KB verilog.asm 114KB

verilog.asm 114KB verilog.asm 94KB

verilog.asm 94KB verilog.asm 92KB

verilog.asm 92KB verilog.asm 79KB

verilog.asm 79KB verilog.asm 75KB

verilog.asm 75KB verilog.asm 71KB

verilog.asm 71KB verilog.asm 61KB

verilog.asm 61KB verilog.asm 56KB

verilog.asm 56KB verilog.asm 51KB

verilog.asm 51KB verilog.asm 50KB

verilog.asm 50KB verilog.asm 46KB

verilog.asm 46KB verilog.asm 45KB

verilog.asm 45KB verilog.asm 42KB

verilog.asm 42KB verilog.asm 38KB

verilog.asm 38KB verilog.asm 35KB

verilog.asm 35KB verilog.asm 33KB

verilog.asm 33KB verilog.asm 32KB

verilog.asm 32KB verilog.asm 26KB

verilog.asm 26KB verilog.asm 24KB

verilog.asm 24KB verilog.asm 23KB

verilog.asm 23KB verilog.asm 22KB

verilog.asm 22KB verilog.asm 21KB

verilog.asm 21KB verilog.asm 21KB

verilog.asm 21KB verilog.asm 20KB

verilog.asm 20KB verilog.asm 18KB

verilog.asm 18KB verilog.asm 17KB

verilog.asm 17KB verilog.asm 16KB

verilog.asm 16KB verilog.asm 15KB

verilog.asm 15KB verilog.asm 15KB

verilog.asm 15KB verilog.asm 15KB

verilog.asm 15KB verilog.asm 14KB

verilog.asm 14KB verilog.asm 14KB

verilog.asm 14KB verilog.asm 14KB

verilog.asm 14KB verilog.asm 14KB

verilog.asm 14KB verilog.asm 13KB

verilog.asm 13KB verilog.asm 13KB

verilog.asm 13KB verilog.asm 12KB

verilog.asm 12KB verilog.asm 12KB

verilog.asm 12KB verilog.asm 12KB

verilog.asm 12KB verilog.asm 11KB

verilog.asm 11KB verilog.asm 10KB

verilog.asm 10KB verilog.asm 10KB

verilog.asm 10KB verilog.asm 10KB

verilog.asm 10KB verilog.asm 10KB

verilog.asm 10KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 5KB

verilog.asm 5KB verilog.asm 5KB

verilog.asm 5KB verilog.asm 4KB

verilog.asm 4KB verilog.asm 4KB

verilog.asm 4KB verilog.asm 4KB

verilog.asm 4KB verilog.asm 4KB

verilog.asm 4KB verilog.asm 4KB

verilog.asm 4KB verilog.asm 3KB

verilog.asm 3KB verilog.asm 3KB

verilog.asm 3KB verilog.asm 3KB

verilog.asm 3KB verilog.asm 3KB

verilog.asm 3KB verilog.asm 3KB

verilog.asm 3KB- 1

- 2

- 3

- 4

- 5

- 粉丝: 85

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【重磅,更新!】国自然管理学部标书80+份(内附清单)(2005-2021年)

- windows 自动关机小程序

- YUV视频播放器,包含图片显示,解码

- Kotlin编程语言详解及其在Android开发中的应用

- 基于C#使用Blazor+AutoGen打造多角色的会话Agent,打造有趣的智能体,通过.Net 集成AutoGen,可以在页面快速的配置不同角色的Agent进行群聊+源码(毕业设计&课程设计)

- cocos creator 3.8 抖音侧边栏复访功能

- 【重磅,更新!】中国2839个站点逐日降水数据集(0.1°/0.25°/0.5°)(1961-2022年)

- RPC远程调用示例,zeroc入门例程

- 基于python实现的多智能体强化学习(MARL)算法复现,包括QMIX,VDN,QTRAN、MAVEN+源码(毕业设计&课程设计&项目开发)

- 【重磅,更新!】教学成果、一流学科申报书范本、最全教改、课程思政(内附清单)

信息提交成功

信息提交成功

评论0