SOLOMON SYSTECH

SEMICONDUCTOR TECHNICAL DATA

This document contains information on a new product. Specifications and information herein are subject to change

without notice.

http://www.solomon-systech.com

SSD1305 Rev 1.8 P 1/71 Jul 2007

Copyright © 2007 Solomon Systech Limited

SSD1305

Advance Information

132 x 64 Dot Matrix

OLED/PLED Segment/Common Driver with Controller

Solomon Systech Jul 2007 P 2/71 Rev 1.8 SSD1305

CONTENTS

1 GENERAL DESCRIPTION.................................................................................................... 7

2 FEATURES ............................................................................................................................... 7

3 ORDERING INFORMATION................................................................................................ 7

4 BLOCK DIAGRAM................................................................................................................. 8

5 DIE PAD FLOOR PLAN......................................................................................................... 9

6 PIN ARRANGEMENT .......................................................................................................... 12

6.1 SSD1305T6R1 PIN ASSIGNMENT.........................................................................................................................12

6.2 SSD1305T7R1 PIN ASSIGNMENT.........................................................................................................................14

7 PIN DESCRIPTION............................................................................................................... 16

8 FUNCTIONAL BLOCK DESCRIPTIONS ......................................................................... 18

8.1 MCU INTERFACE SELECTION...............................................................................................................................18

8.1.1 MCU Parallel 6800-series Interface...............................................................................................................18

8.1.2 MCU Parallel 8080-series Interface...............................................................................................................19

8.1.3 MCU Serial Interface......................................................................................................................................21

8.1.4 MCU I

2

C Interface..........................................................................................................................................21

8.2 COMMAND DECODER ..........................................................................................................................................24

8.3 OSCILLATOR CIRCUIT AND DISPLAY TIME GENERATOR......................................................................................25

8.4 FR SYNCHRONIZATION ........................................................................................................................................26

8.5 RESET CIRCUIT ....................................................................................................................................................26

8.6 SEGMENT DRIVERS / COMMON DRIVERS .............................................................................................................27

8.7 GRAPHIC DISPLAY DATA RAM (GDDRAM)......................................................................................................29

8.8 AREA COLOR DECODER.......................................................................................................................................30

8.9 SEG/COM DRIVING BLOCK ................................................................................................................................31

8.10 POWER ON AND OFF SEQUENCE .........................................................................................................................32

8.11 DC-DC CONVERTER ...........................................................................................................................................33

9 COMMAND TABLE.............................................................................................................. 35

9.1 DATA READ / WRITE ...........................................................................................................................................41

10 COMMAND DESCRIPTIONS ............................................................................................. 42

10.1 FUNDAMENTAL COMMAND .................................................................................................................................42

10.1.1 Set Lower Column Start Address for Page Addressing Mode (00h~0Fh) ......................................................42

10.1.2 Set Higher Column Start Address for Page Addressing Mode (10h~1Fh) .....................................................42

10.1.3 Set Memory Addressing Mode (20h)...............................................................................................................42

10.1.4 Set Column Address (21h) ..............................................................................................................................43

10.1.5 Set Page Address (22h)...................................................................................................................................44

10.1.6 Set Display Start Line (40h~7Fh)...................................................................................................................45

10.1.7 Set Contrast Control for BANK0 (81h)...........................................................................................................45

10.1.8 Set Brightness for Area Color Banks (82h).....................................................................................................45

10.1.9 Set Look Up Table (LUT) (91h).....................................................................................................................45

10.1.10 Set Bank Color of BANK1 to BANK16 (PAGE0) (92h) ..............................................................................46

10.1.11 Set Bank Color of BANK17 to BANK32 (PAGE0) (93h) ............................................................................46

10.1.12 Set Segment Re-map (A0h/A1h)..................................................................................................................46

10.1.13 Entire Display ON (A4h/A5h)...................................................................................................................46

10.1.14 Set Normal/Inverse Display (A6h/A7h).......................................................................................................46

10.1.15 Set Multiplex Ratio (A8h)............................................................................................................................46

10.1.16 Reserved (AAh) ...........................................................................................................................................46

10.1.17 Dim Mode setting (ABh) .............................................................................................................................46

SSD1305 Rev 1.8 P 3/71 Jul 2007 Solomon Systech

10.1.18 Master Configuration (ADh).......................................................................................................................46

10.1.19 Set Display ON/OFF (ACh/AEh/AFh)........................................................................................................47

10.1.20 Set Page Start Address for Page Addressing Mode (B0h~B7h)..................................................................47

10.1.21 Set COM Output Scan Direction (C0h/C8h)...............................................................................................47

10.1.22 Set Display Offset (D3h).............................................................................................................................47

10.1.23 Set Display Clock Divide Ratio/ Oscillator Frequency (D5h)....................................................................50

10.1.24 Set Area Color Mode ON/OFF & Low Power Display Mode (D8h)..........................................................50

10.1.25 Set Pre-charge Period (D9h)......................................................................................................................50

10.1.26 Set COM Pins Hardware Configuration (DAh)..........................................................................................51

10.1.27 Set V

COMH

Deselect Level (DBh) .................................................................................................................53

10.1.28 Enter Read Modify Write (E0h) ..................................................................................................................53

10.1.29 NOP (E3h) ..................................................................................................................................................54

10.1.30 Exit Read Modify Write (EEh) ....................................................................................................................54

10.1.31 Status register Read....................................................................................................................................54

10.2 GRAPHIC ACCELERATION COMMAND..................................................................................................................55

10.2.1 Horizontal Scroll Setup (26h/27h)..................................................................................................................55

10.2.2 Continuous Vertical and Horizontal Scroll Setup (29h/2Ah)..........................................................................56

10.2.3 Deactivate Scroll (2Eh)...................................................................................................................................57

10.2.4 Activate Scroll (2Fh).......................................................................................................................................57

10.2.5 Set Vertical Scroll Area(A3h) .........................................................................................................................58

11 MAXIMUM RATINGS.......................................................................................................... 59

12 DC CHARACTERISTICS..................................................................................................... 60

13 AC CHARACTERISTICS..................................................................................................... 61

14 APPLICATION EXAMPLE.................................................................................................. 66

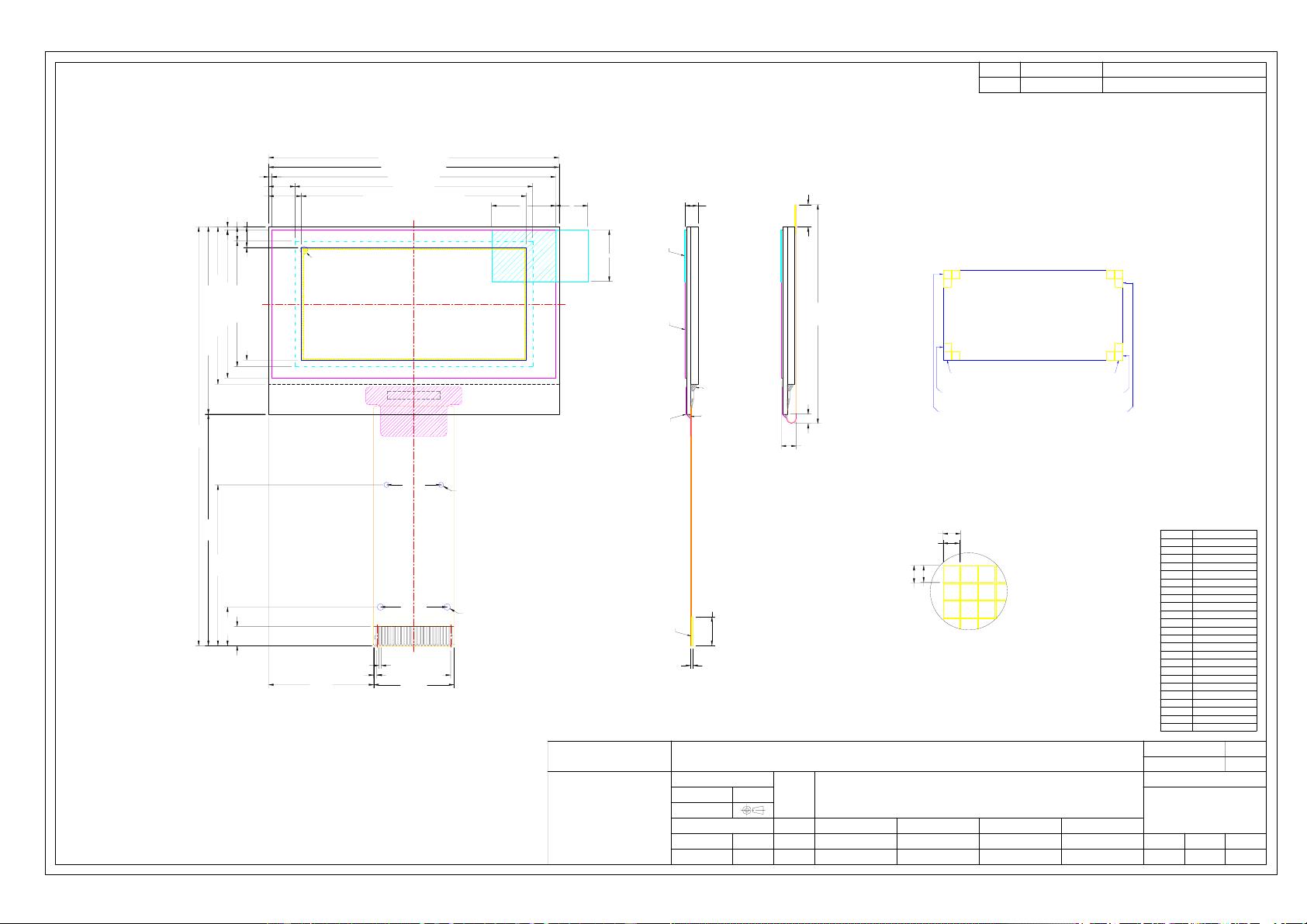

15 PACKAGE INFORMATION................................................................................................ 67

15.1 SSD1305Z DIE TRAY INFORMATION...................................................................................................................67

15.2 SSD1305T6R1 DETAIL DIMENSION ....................................................................................................................68

15.3 SSD1305T7R1 DETAIL DIMENSION ....................................................................................................................70

Solomon Systech Jul 2007 P 4/71 Rev 1.8 SSD1305

TABLES

TABLE 3-1 : ORDERING INFORMATION................................................................................................... 7

TABLE 5-1 : SSD1305Z BUMP DIE PAD COORDINATES ....................................................................... 11

TABLE 6-1 : SSD1305T6R1 PIN ASSIGNMENT TABLE......................................................................... 13

TABLE 6-2 : SSD1305T7R1 PIN ASSIGNMENT .................................................................................... 15

TABLE 7-1 : PIN DESCRIPTION ............................................................................................................. 16

TABLE 7-2 : MCU BUS INTERFACE PIN SELECTION ............................................................................. 17

TABLE 8-1 : MCU INTERFACE ASSIGNMENT UNDER DIFFERENT BUS INTERFACE MODE........................ 18

TABLE 8-2 : CONTROL PINS OF 6800 INTERFACE .................................................................................. 18

TABLE 8-3 : CONTROL PINS OF 8080 INTERFACE (FORM 1) .................................................................. 20

TABLE 8-4 : CONTROL PINS OF 8080 INTERFACE (FORM 2) .................................................................. 20

TABLE 8-5 : CONTROL PINS OF SERIAL INTERFACE .............................................................................. 21

TABLE 8-6 : PASSIVE COMPONENT SELECTION ..................................................................................... 34

TABLE 9-1: COMMAND TABLE............................................................................................................. 35

TABLE 9-2 : READ COMMAND TABLE .................................................................................................. 41

TABLE 9-3 : ADDRESS INCREMENT TABLE (AUTOMATIC)..................................................................... 41

TABLE 10-1 : EXAMPLE OF SET DISPLAY OFFSET AND DISPLAY START LINE WITH NO REMAP ........... 48

TABLE 10-2 :EXAMPLE OF SET DISPLAY OFFSET AND DISPLAY START LINE WITH REMAP ................. 49

TABLE 10-3 : COM PINS HARDWARE CONFIGURATION....................................................................... 51

TABLE 10-4 : EXAMPLE OF READ MODIFY WRITE MODE .................................................................... 54

TABLE 11-1 : MAXIMUM RATINGS (VOLTAGE REFERENCED TO V

SS

) .................................................. 59

TABLE 12-1 : DC CHARACTERISTICS ................................................................................................... 60

TABLE 13-1 : AC CHARACTERISTICS ................................................................................................... 61

TABLE 13-2 : 6800-SERIES MCU PARALLEL INTERFACE TIMING CHARACTERISTICS.......................... 62

TABLE 13-3 : 8080-SERIES MCU PARALLEL INTERFACE TIMING CHARACTERISTICS.......................... 63

TABLE 13-4 : SERIAL INTERFACE TIMING CHARACTERISTICS .............................................................. 64

TABLE 13-5 :I

2

C INTERFACE TIMING CHARACTERISTICS ..................................................................... 65

SSD1305 Rev 1.8 P 5/71 Jul 2007 Solomon Systech

FIGURES

FIGURE 4-1 : SSD1305 BLOCK DIAGRAM .............................................................................................. 8

FIGURE 5-1 : SSD1305Z DIE DRAWING................................................................................................. 9

FIGURE 5-2 : SSD1305Z ALIGNMENT MARKS DIMENSION .................................................................. 10

FIGURE 6-1 : SSD1305T6R1 PIN ASSIGNMENT ................................................................................... 12

FIGURE 6-2 : SSD1305T7R1 PIN ASSIGNMENT ................................................................................... 14

FIGURE 8-1 : DATA READ BACK PROCEDURE - INSERTION OF DUMMY READ......................................... 19

FIGURE 8-2 : EXAMPLE OF WRITE PROCEDURE IN 8080 PARALLEL INTERFACE MODE .......................... 19

FIGURE 8-3 : EXAMPLE OF READ PROCEDURE IN 8080 PARALLEL INTERFACE MODE............................ 19

FIGURE 8-4 : DISPLAY DATA READ BACK PROCEDURE - INSERTION OF DUMMY READ .......................... 20

FIGURE 8-5 : WRITE PROCEDURE IN SPI MODE..................................................................................... 21

FIGURE 8-6 : I2C-BUS DATA FORMAT................................................................................................... 22

FIGURE 8-7 : DEFINITION OF THE START AND STOP CONDITION........................................................... 23

FIGURE 8-8 : DEFINITION OF THE ACKNOWLEDGEMENT CONDITION..................................................... 24

FIGURE 8-9 : DEFINITION OF THE DATA TRANSFER CONDITION ........................................................... 24

FIGURE 8-10 : OSCILLATOR CIRCUIT AND DISPLAY TIME GENERATOR ............................................... 25

FIGURE 8-11 : SEGMENT OUTPUT WAVEFORM IN THREE PHASES......................................................... 27

FIGURE 8-12 : SEGMENT OUTPUT WAVEFORM FOR TWO DIFFERENT COLORS LUT SETTING................ 27

FIGURE 8-13 : EXAMPLE OF SEGMENT OUTPUT WAVEFORM OF MONOCHROME DISPLAY SECTION

UNDER MONOCHROME MODE

......................................................................................................... 28

FIGURE 8-14 : EXAMPLE OF SEGMENT OUTPUT WAVEFORM OF AREA COLOR DISPLAY SECTION UNDER

AREA COLOR MODE

........................................................................................................................ 28

FIGURE 8-15 : GDDRAM PAGES STRUCTURE OF SSD1305 ................................................................. 29

FIGURE 8-16 : ENLARGEMENT OF GDDRAM (NO ROW RE-MAPPING AND COLUMN-REMAPPING) ....... 29

FIGURE 8-17 : EXAMPLE OF AREA COLOR ASSIGNMENT ON A 132X64 OLED PANEL ........................... 30

FIGURE 8-18 : I

REF

CURRENT SETTING BY RESISTOR VALUE ............................................................... 31

FIGURE 8-19 : THE POWER ON SEQUENCE ........................................................................................... 32

FIGURE 8-20 : THE POWER OFF SEQUENCE ......................................................................................... 32

FIGURE 8-21 : DC-DC VOLTAGE CONVERTER CIRCUIT ........................................................................ 33

FIGURE 10-1 : ADDRESS POINTER MOVEMENT OF PAGE ADDRESSING MODE ....................................... 42

FIGURE 10-2 : EXAMPLE OF GDDRAM ACCESS POINTER SETTING IN PAGE ADDRESSING MODE (NO

ROW AND COLUMN

-REMAPPING) ................................................................................................... 42

FIGURE 10-3 : ADDRESS POINTER MOVEMENT OF HORIZONTAL ADDRESSING MODE........................... 43

FIGURE 10-4 : ADDRESS POINTER MOVEMENT OF VERTICAL ADDRESSING MODE ............................... 43

FIGURE 10-5 : EXAMPLE OF COLUMN AND ROW ADDRESS POINTER MOVEMENT................................ 44

FIGURE 10-6 : SEGMENT CURRENT VS CONTRAST SETTING .................................................................. 45

FIGURE 10-7 :TRANSITION BETWEEN DIFFERENT MODES ..................................................................... 47

FIGURE 10-8 : TYPICAL OSCILLATOR FREQUENCY ADJUSTMENT BY D5 COMMAND (V

DD

=2.8V)........ 50

FIGURE 10-9 : HORIZONTAL SCROLL EXAMPLE: SCROLL RIGHT BY 4 COLUMNS ................................ 55

FIGURE 10-10 : HORIZONTAL SCROLL EXAMPLE: SCROLL LEFT BY 2 COLUMNS ................................. 55

FIGURE 10-11 : HORIZONTAL SCROLLING SETUP EXAMPLE .................................................................. 55

FIGURE 10-12 : CONTINUOUS VERTICAL AND HORIZONTAL SCROLLING SETUP EXAMPLES.................. 56

FIGURE 10-13 : CONTINUOUS VERTICAL AND HORIZONTAL SCROLLING EXAMPLE: WITH SETTING IN

MUX RATIO .................................................................................................................................. 57

FIGURE 10-14 : VERTICAL SCROLL AREA SETUP EXAMPLES ................................................................. 58

FIGURE 13-1 : 6800-SERIES MCU PARALLEL INTERFACE CHARACTERISTICS ....................................... 62

FIGURE 13-2 : 8080-SERIES PARALLEL INTERFACE CHARACTERISTICS (FORM 1) ................................. 63

FIGURE 13-3 : 8080-SERIES PARALLEL INTERFACE CHARACTERISTICS (FORM 2) ................................. 63

FIGURE 13-4 : SERIAL INTERFACE CHARACTERISTICS .......................................................................... 64

FIGURE 13-5 : I

2

C INTERFACE TIMING CHARACTERISTICS ................................................................... 65

评论0