ADC0832开发板程序.zip_adc0832

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

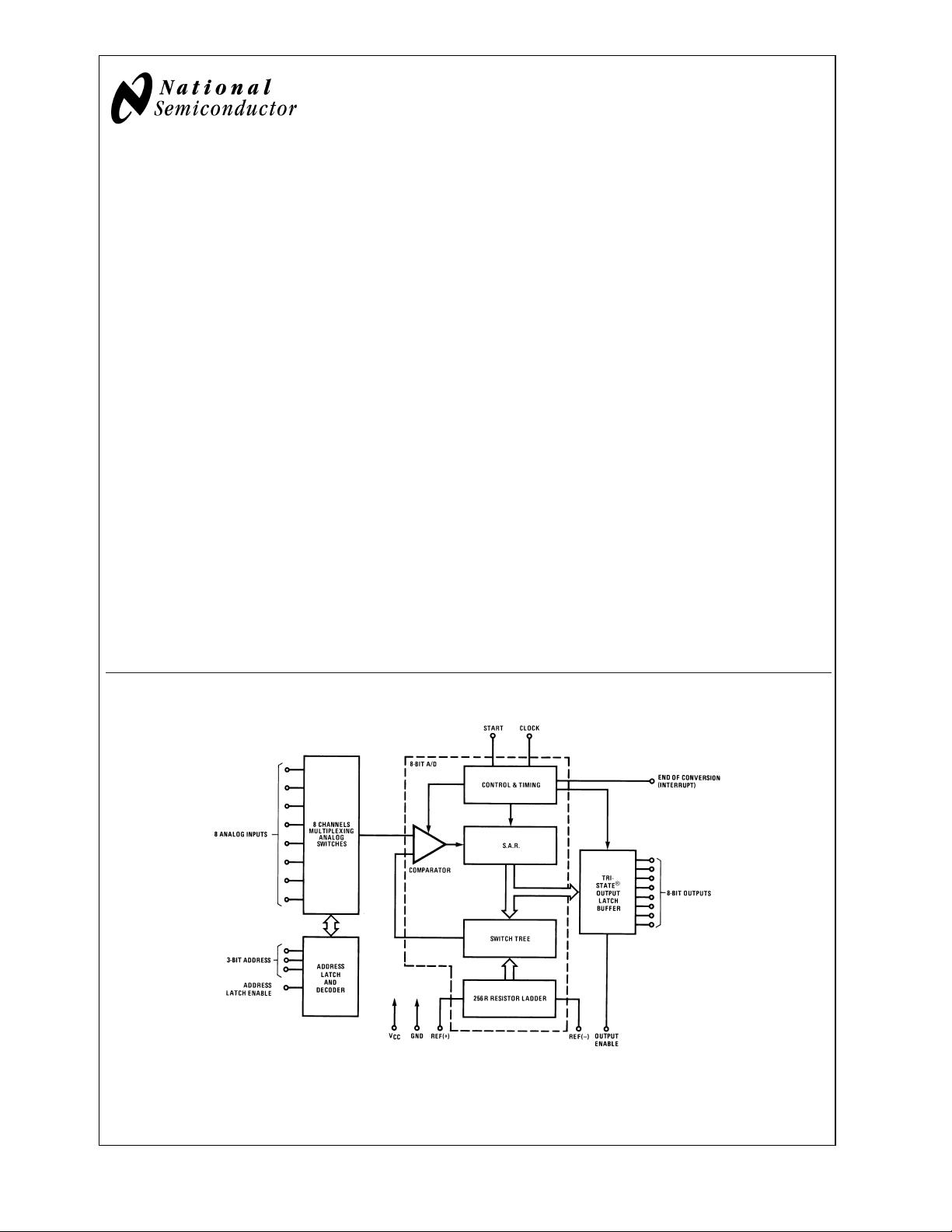

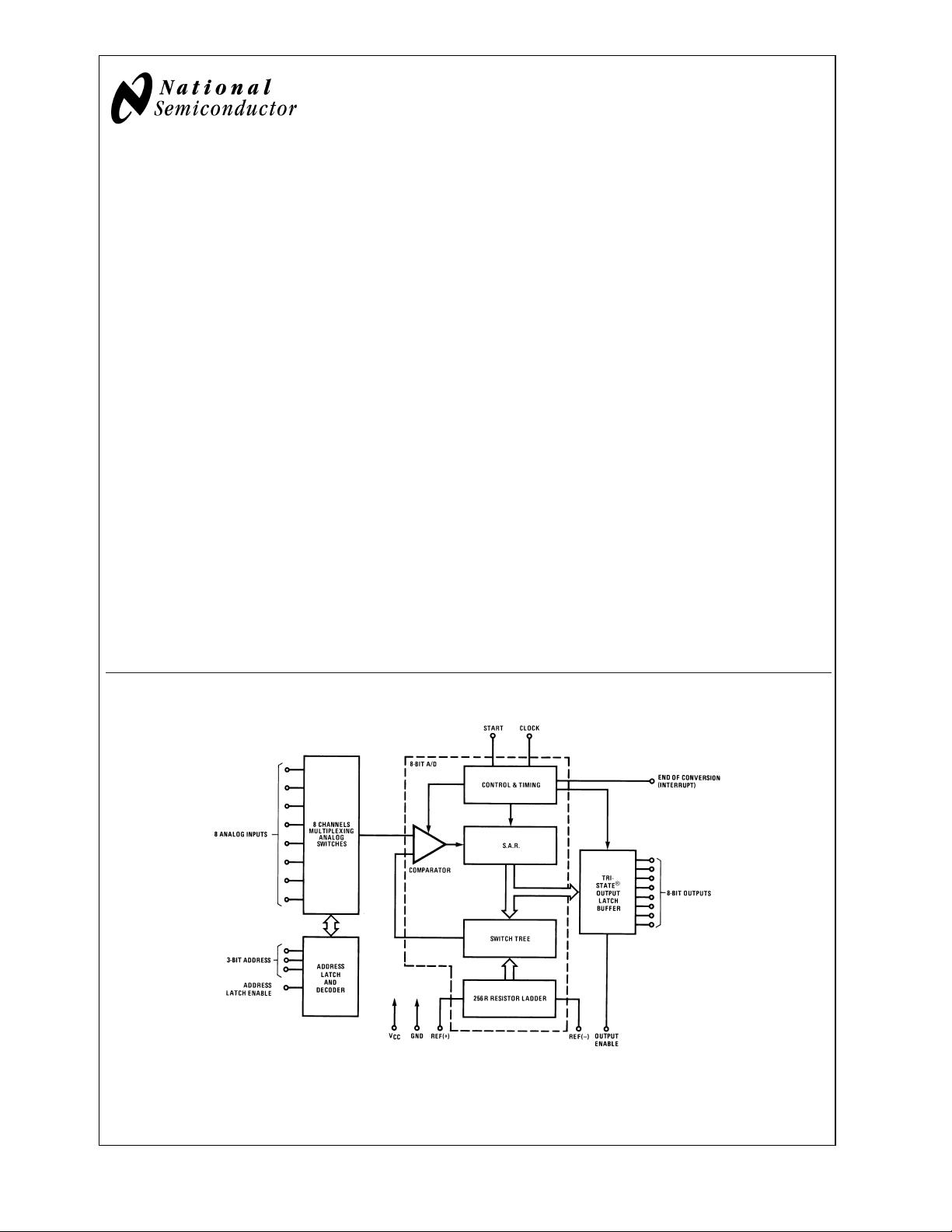

ADC0832是一款8位、单通道模拟数字转换器(ADC),在许多电子设计中都有广泛应用,特别是在需要将模拟信号转化为数字信号的系统中。这个"ADC0832开发板程序.zip_adc0832"压缩包显然是为了帮助用户理解和实践ADC0832的使用方法,通过具体的开发板测试程序来深入学习。 ADC0832的主要功能是将输入的模拟电压转换为相应的8位二进制数字。它有一个单一的输入通道,这意味着一次只能处理一个模拟信号。转换过程由转换启动引脚(START)触发,然后经过一定的时间延迟后,转换结果会通过数据输出引脚(DOUT)提供。转换速率通常在几微妙到几十微妙之间,具体取决于外部时钟源的频率。 在ADC0832的开发过程中,通常需要以下几个关键步骤: 1. **硬件连接**:将ADC0832与微控制器(如Arduino、AVR或STM32)连接,确保电源、时钟、启动和中断引脚正确连接。还需要设置适当的参考电压(VREF),这将决定输入模拟电压的范围。 2. **配置时钟**:根据设计需求配置外部时钟源,时钟频率决定了ADC的转换速率。较高的时钟频率意味着更快的转换速度,但可能会牺牲精度。 3. **编程**:编写微控制器的固件来控制ADC0832。这包括启动转换、读取转换结果、处理中断等操作。压缩包中的"开发板程序"应该包含了这些功能的实现代码。 4. **测试与调试**:通过连接模拟信号源,观察转换结果,验证ADC0832的性能和准确度。开发板程序应该包含了一系列的测试用例,用于检查不同输入电压下的转换效果。 5. **应用集成**:在实际项目中,ADC0832常用于温度传感器、音频信号处理、电机控制等各种场景。理解并熟练使用ADC0832的开发板程序能帮助开发者更好地将ADC0832集成到自己的系统中。 这个压缩包的使用者可以从程序中学习如何初始化ADC0832,如何触发转换,以及如何读取和解析转换结果。此外,可能还包含了错误处理和中断服务例程,这些都是实时系统中不可或缺的部分。通过深入研究并实践这个程序,开发者可以掌握ADC0832的关键操作,并且能够灵活地将其应用于各种实际工程中。

ADC0832开发板程序.zip (21个子文件)

ADC0832开发板程序.zip (21个子文件)  开发板程序

开发板程序  keil

keil  chengxu.__i 37B

chengxu.__i 37B chengxu.lnp 62B

chengxu.lnp 62B chengxu_Opt.Bak 1KB

chengxu_Opt.Bak 1KB chengxu.Opt 1KB

chengxu.Opt 1KB chengxu.plg 1KB

chengxu.plg 1KB chengxu 5KB

chengxu 5KB chengxu.LST 5KB

chengxu.LST 5KB STARTUP.LST 11KB

STARTUP.LST 11KB chengxu_Uv2.Bak 0B

chengxu_Uv2.Bak 0B chengxu.Uv2 2KB

chengxu.Uv2 2KB chengxu.OBJ 5KB

chengxu.OBJ 5KB STARTUP.A51 6KB

STARTUP.A51 6KB chengxu.c 3KB

chengxu.c 3KB STARTUP.OBJ 750B

STARTUP.OBJ 750B chengxu.hex 2KB

chengxu.hex 2KB chengxu.M51 8KB

chengxu.M51 8KB ourhc.PWI 768B

ourhc.PWI 768B ourhc.DSN 182KB

ourhc.DSN 182KB ADC0809.pdf 317KB

ADC0809.pdf 317KB Last Loaded ourhc.DBK 182KB

Last Loaded ourhc.DBK 182KB ADC0809中文资料.txt 2KB

ADC0809中文资料.txt 2KB- 1

- 粉丝: 95

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于k折交叉验证的支持向量机回归预测MATLAB程序,采用n折交叉验证确定损失参数C与核参数g;代码注释清楚 main为主程序,读取EXCEL数据,也可以自己数据集 很方便,容易上手

- 链表HuffmanTree.zip

- Xshell+Xmanager+Xftp全家桶-V8.0.0065 PC绿色特别版

- 《JavaScript》.pdf

- 基于椭圆拟合的多光斑重叠光斑中心提取方法

- OC-Dialect线上多语言(多列表) 4.SDK每个方法解析

- 扩展卡尔曼滤波soc估算 基于EKF算法的锂电池SOC 卡尔曼滤波估计电池soc ,simulink模型,对电池SOC参数进行辨识,充分考虑充放电倍率和环境温度,结合传统安时积分法和扩展卡尔曼滤波算法

- 基于springboot的墙绘产品展示交易平台的设计与实现源码(java毕业设计完整源码+LW).zip

- GBBO_Dataset.zip

- 基于springboot的网上租赁系统设计与实现源码(java毕业设计完整源码+LW).zip

- 强大的Lua引擎, 为mcu和物联网设备高度优化, 支持众多组件, 非常低的内存需求(最低16K RAM, 128K Flash)

- 2024年电赛H题代码

- 基于Web足球青训俱乐部管理后台系统开发源码(java毕业设计完整源码+LW).zip

- OC-Dialect线上多语言(多列表) 5.总结

- ACM考试题 ACM程序设计

- 基于springboot的师生健康信息管理系统源码(java毕业设计完整源码+LW).zip

信息提交成功

信息提交成功