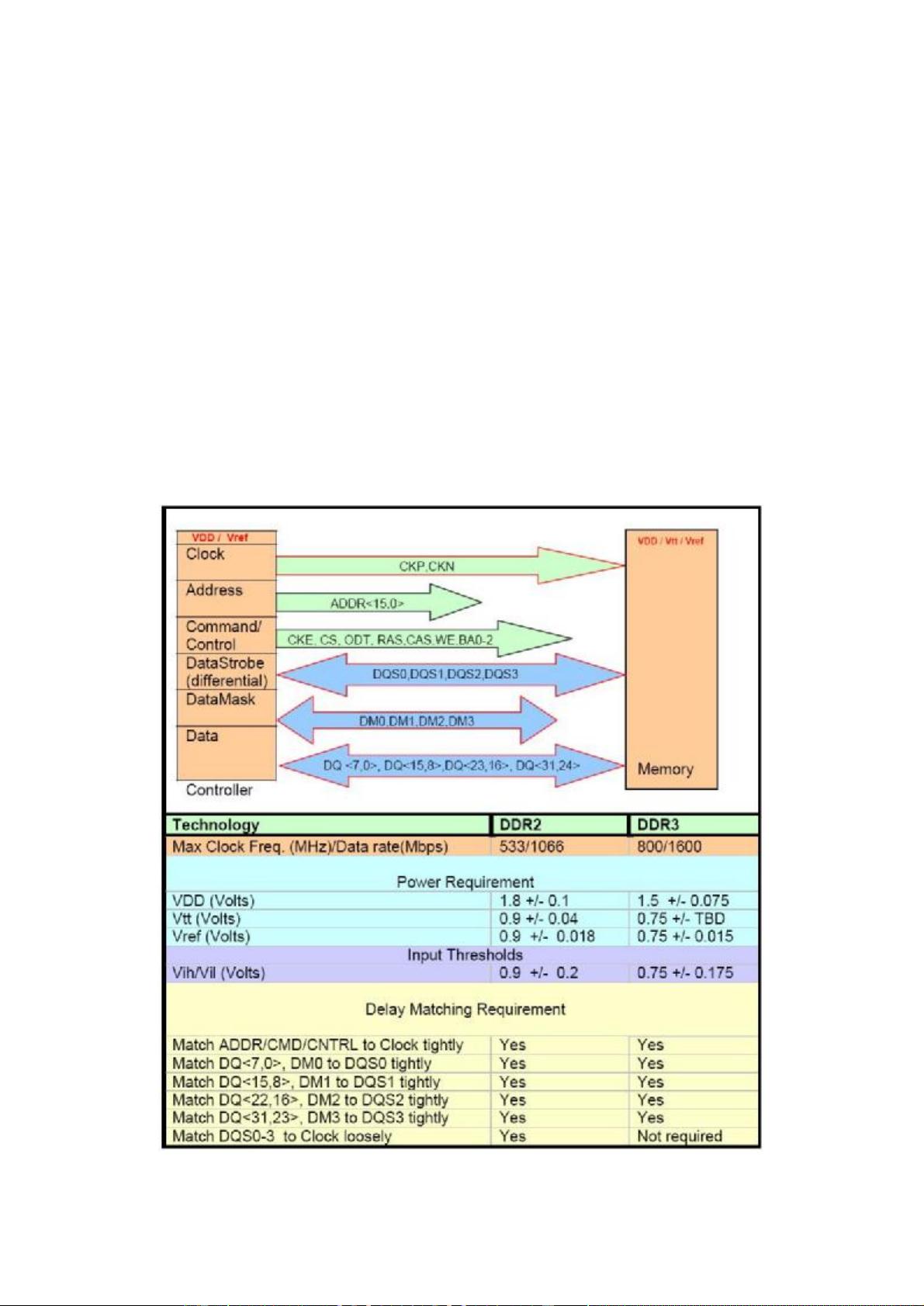

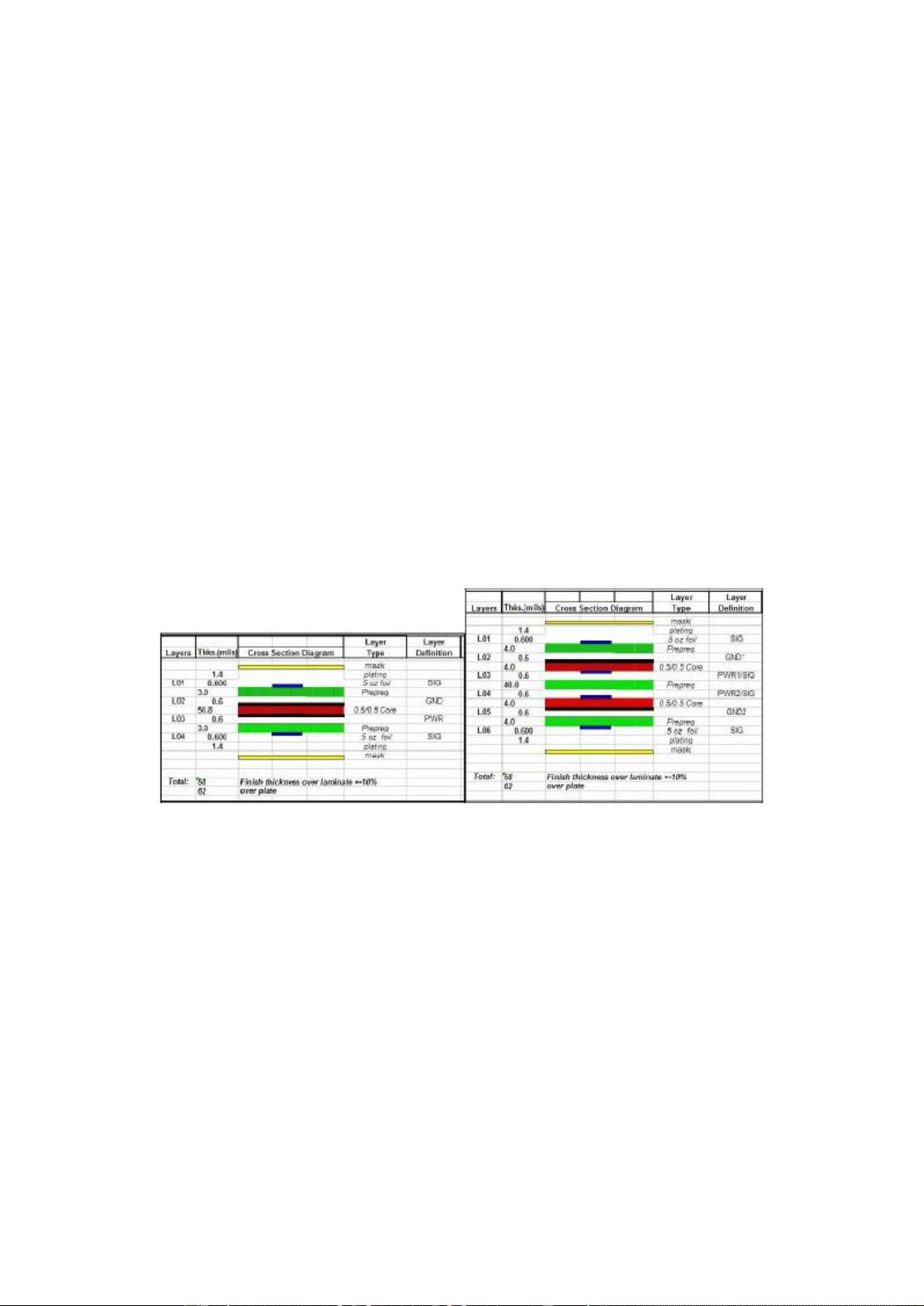

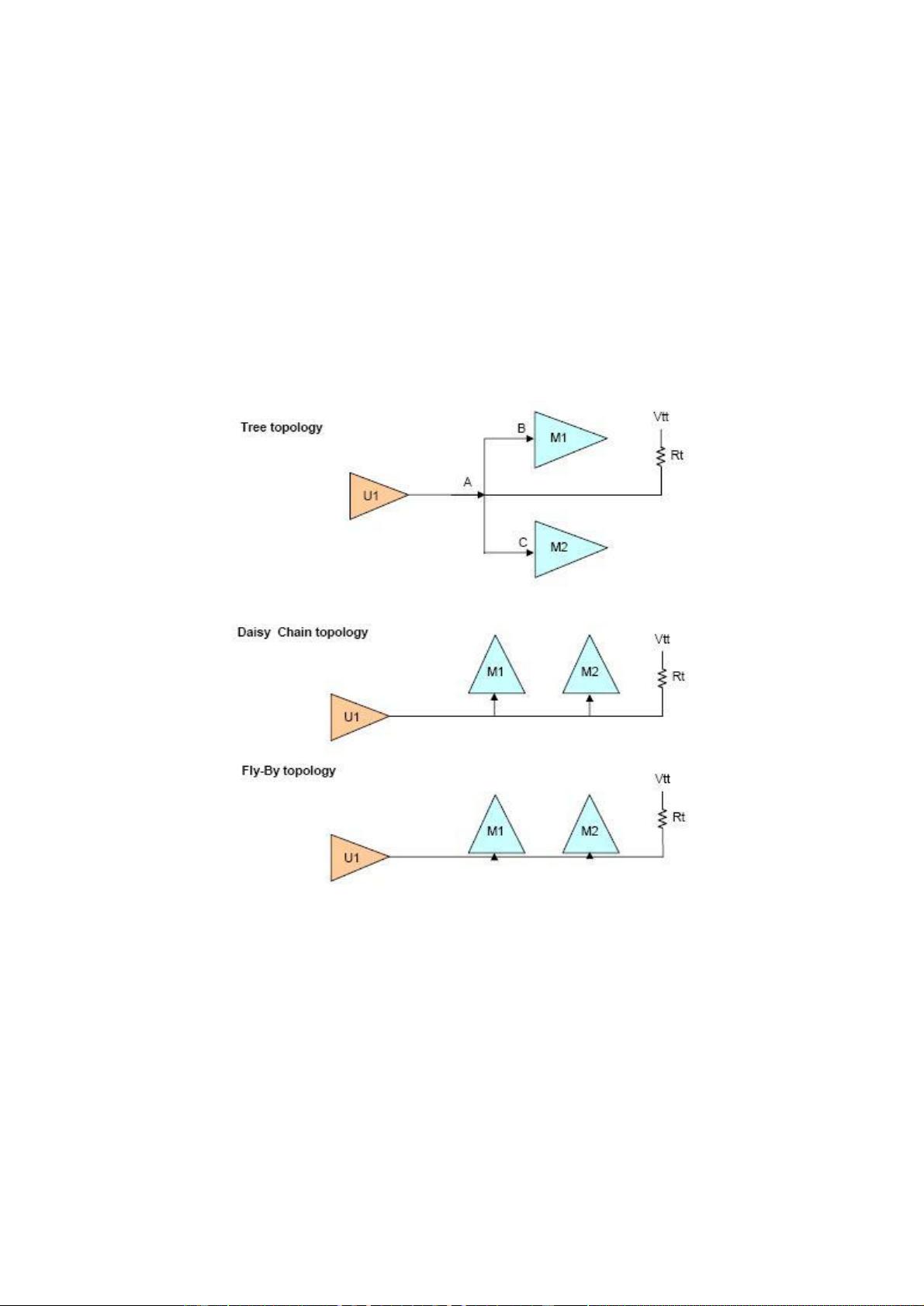

DDR2和DDR3内存技术是现代计算机及嵌入式系统中普遍使用的内存解决方案。它们的高效运行依赖于设计良好的印刷电路板(PCB)信号完整性。本文深入探讨了DDR2和DDR3在PCB设计中实现信号完整性的关键考量因素,包括PCB叠层结构、阻抗控制、互联通路拓扑、时延匹配、串扰、电源完整性和时序分析。这些因素共同决定了内存模块在高速传输下的性能表现。 DDR2和DDR3的速度范围广泛,从800Mbps到1600Mbps不等。设计者需要确保PCB上的信号时序精确匹配,以便维持信号波形的完整性。为此,要考虑到多个影响因素,比如PCB叠层设计、信号路径的阻抗、信号线的拓扑结构、时延匹配的精确性、避免串扰问题、保持电源完整性和精心设计的时序控制。 在PCB叠层方面,一般在4层板设计中,顶层和底层用以走信号线,中间层则分别用作电源(VDD)和地(GND)平面。这种结构有助于减少电磁干扰,并提高信号的传输质量。然而,对于6层板设计,因为电源层和地层的间距更小,从而提高了电源完整性(PI),可以实现更加复杂和优化的信号通路设计。 阻抗匹配是确保信号完整性的重要环节,尤其是在DDR2中,单端信号的阻抗通常维持在50欧姆,而差分信号的阻抗匹配电阻为100欧姆。在DDR3中,单端信号的阻抗匹配电阻在40到60欧姆之间,并根据仿真结果可能需要调整,而差分信号阻抗依然保持在100欧姆。 互联通路拓扑是指信号在PCB上布线的方式,不同的拓扑结构适用于不同类型的设计。对于DDR2和DDR3,点对点连接的信号线(如DQ、DM和DQS)不需要特殊的拓扑结构。而对于多片内存设计,如multi-rank DIMMs,就需要选择合适的拓扑结构,如菊花链式拓扑结构。这种结构在实现信号完整性和减小噪声方面表现良好。然而,实际设计中需要在信号完整性、布线长度和布线难度之间做出权衡。 时延匹配对高速信号来说是一个挑战,因为在布线时通常会有弯曲和穿过不同PCB层的过孔,这些都会导致信号路径长度不一致。为了解决时延匹配问题,设计师会使用trombone走线技术,通过增加走线长度来补偿过孔或弯曲走线带来的时延。然而,这种方法带来的时延匹配并不完美,尤其是在高频操作时,因此设计者还需考虑其他方法来优化时延匹配。 串扰是信号在高速传输时相互干扰的问题,它会导致信号质量下降。通过仔细控制信号线的布局、保持相邻信号线之间足够的间距以及使用适当的屏蔽技术,可以有效降低串扰。 电源完整性关注的是电源和地层的连续性以及整个系统的供电稳定性。设计师需要确保有足够的电源平面和地平面以支撑高速切换的电源需求,同时还要保持电源和地层之间的电气性能。 时序分析是验证信号完整性的一个关键环节。设计师必须检查所有的信号路径时序,以确保所有信号到达其目的地的时间是一致的。这一过程通常涉及到大量的仿真工作,使用EDA工具进行精确的时序分析和优化。 PCB设计人员在处理DDR2和DDR3内存模块设计时,需要细致考虑信号完整性涉及的各个方面。使用先进的EDA工具可以帮助设计者在设计初期发现潜在问题,并对设计进行必要的调整,以确保高速数据传输的稳定性和可靠性。

剩余14页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 白色大气的咨询管理企业网页模板下载.zip

- 白色大气的音乐专辑博客整站网站模板下载.zip

- 白色大气风的商务企业网站模板下载.zip

- 白色大气风的集团企业官网整站模板下载.rar

- 白色大气风格的Advisor银行类网站模板下载.zip

- 白色大气风格的CSS+XHTML商务模板.zip

- 白色大气风格的APP定制开发网站模板下载.zip

- 白色大气风格的bootstrap企业网站模板.zip

- 白色大气风格的CSS3模板下载.zip

- 白色大气风格的CSS3网站模板下载.zip

- 白色大气风格的CSS3个人博客模板下载.zip

- 白色大气风格的CSS网站商务模板.zip

- 白色大气风格的HTML商务模板下载.zip

- 白色大气风格的html商务模板.zip

- 白色大气风格的KTV美女麦霸网站模板下载.zip

- 白色大气风格的VI广告设计企业网站源码下载.zip

信息提交成功

信息提交成功