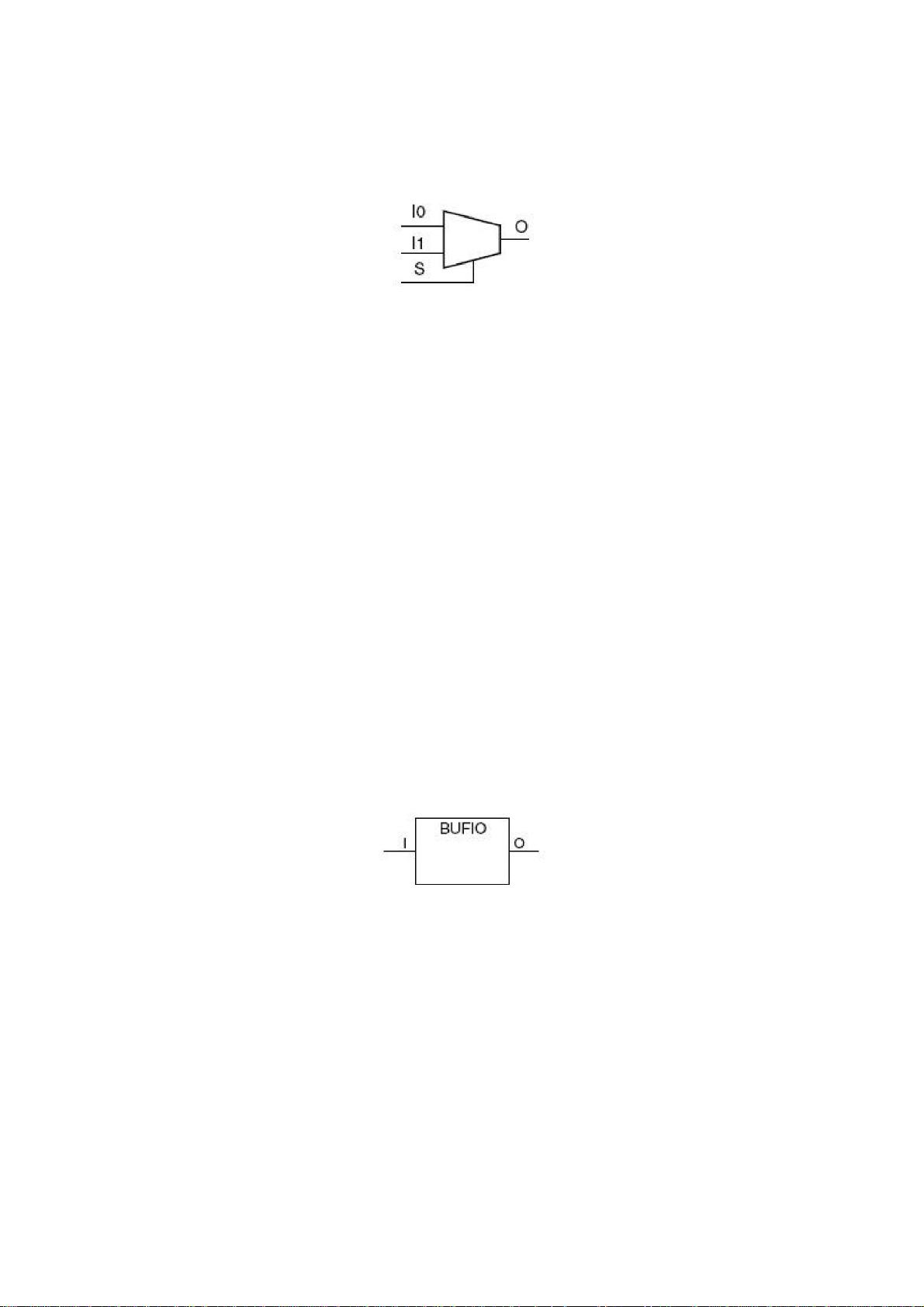

Xilinx 原语的使用方法 1

3.4 Xilinx 公司原语的使用方法

原语,其英文名字为 Primitive,是 Xilinx 针对其器件特征开发的一系列常用模

块的名字,用户可以将其看成 Xilinx 公司为用户提供的库函数,类似于 C++

中的“cout”等关键字,是芯片中的基本元件,代表 FPGA 中实际拥有的硬件逻

辑单元,如 LUT,D 触发器,RAM 等,相当于软件中的机器语言。在实现过

程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否

则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方

式,其和 HDL 语言的关系,类似于汇编语言和 C 语言的关系。

Xilinx 公司提供的原语,涵盖了 FPGA 开发的常用领域,但只有相应配置的硬

件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在

Verilog 中使用原语非常简单,将其作为模块名直接例化即可。本节以 Virtex-4

平台介绍各类原语,因为该系列的原语类型是最全面的。其它系列芯片原语的

使用方法是类似的。

Xilinx 公司的原语按照功能分为 10 类,包括:计算组件、I/O 端口组件、寄存

器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM

组件、Slice/CLB 组件以及 G 比特收发器组件。下面分别对其进行详细介绍。

3.4.1 计算组件

计算组件指的就是 DSP48 核,也有人将其称为硬件乘法器,功能描述如表 3-6

所示。

表 3-6 计算组件清单

DSP48 其结构为一个 18*18 比特的有符号乘法器,且在后面还级联了一个

带有可配置流水线的 3 输入加法器

DSP48 核由一个 18 比特的乘法后面级联一个 48 比特的加法器,乘法器和加

法器的应用位宽分别可以在 18、48 比特内任意调整。其在乘加模块中有广

泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省

逻辑资源且工作在高速模式下。其在 Verilog 中的例化模版为:

module fpga_v4_dsp48(

BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA,

CEB,

CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE,

PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP,

评论5

最新资源