没有合适的资源?快使用搜索试试~ 我知道了~

GTX/GTH高速收发模块The 7 series FPGAs GTX and GTH transceivers are power-efficient transceivers, supporting line rates from 500 Mb/s to 12.5 Gb/s for GTX transceivers and 13.1 Gb/s for GTH transceivers. The GTX/GTH transceiver is highly configurable and tightly integrated with the programmable logic resources of the FPGA. Table 1-1 summarizes the features by functional group that support a wide variety of applications

资源推荐

资源详情

资源评论

7 Series FPGAs

GTX/GTH Transceivers

User Guide

UG476 (v1.12) December 19, 2016

7 Series FPGAs GTX/GTH Transceivers User Guide www.xilinx.com UG476 (v1.12) December 19, 2016

Notice of Disclaimer

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the

maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL

WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF

MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable

(whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature

related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect,

special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as

a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of

the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to

the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior

written consent. Certain products are subject to the terms and conditions of Xilinx’s limited warranty, please refer to Xilinx’s Terms of

Sale which can be viewed at http://www.xilinx.com/legal.htm#tos

; IP cores may be subject to warranty and support terms contained in

a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring

fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx’s

Terms of Sale which can be viewed at http://www.xilinx.com/legal.htm#tos

.

AUTOMOTIVE APPLICATIONS DISCLAIMER

AUTOMOTIVE PRODUCTS (IDENTIFIED AS “XA” IN THE PART NUMBER) ARE NOT WARRANTED FOR USE IN THE DEPLOYMENT

OF AIRBAGS OR FOR USE IN APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE (“SAFETY APPLICATION”) UNLESS THERE

IS A SAFETY CONCEPT OR REDUNDANCY FEATURE CONSISTENT WITH THE ISO 26262 AUTOMOTIVE SAFETY STANDARD

(“SAFETY DESIGN”). CUSTOMER SHALL, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE PRODUCTS,

THOROUGHLY TEST SUCH SYSTEMS FOR SAFETY PURPOSES. USE OF PRODUCTS IN A SAFETY APPLICATION WITHOUT A

SAFETY DESIGN IS FULLY AT THE RISK OF CUSTOMER, SUBJECT ONLY TO APPLICABLE LAWS AND REGULATIONS GOVERNING

LIMITATIONS ON PRODUCT LIABILITY.

© Copyright 2011–2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands

included herein are trademarks of Xilinx in the United States and other countries. CPRI is a trademark of Siemens AG. PCI, PCIe and

PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

Revision History

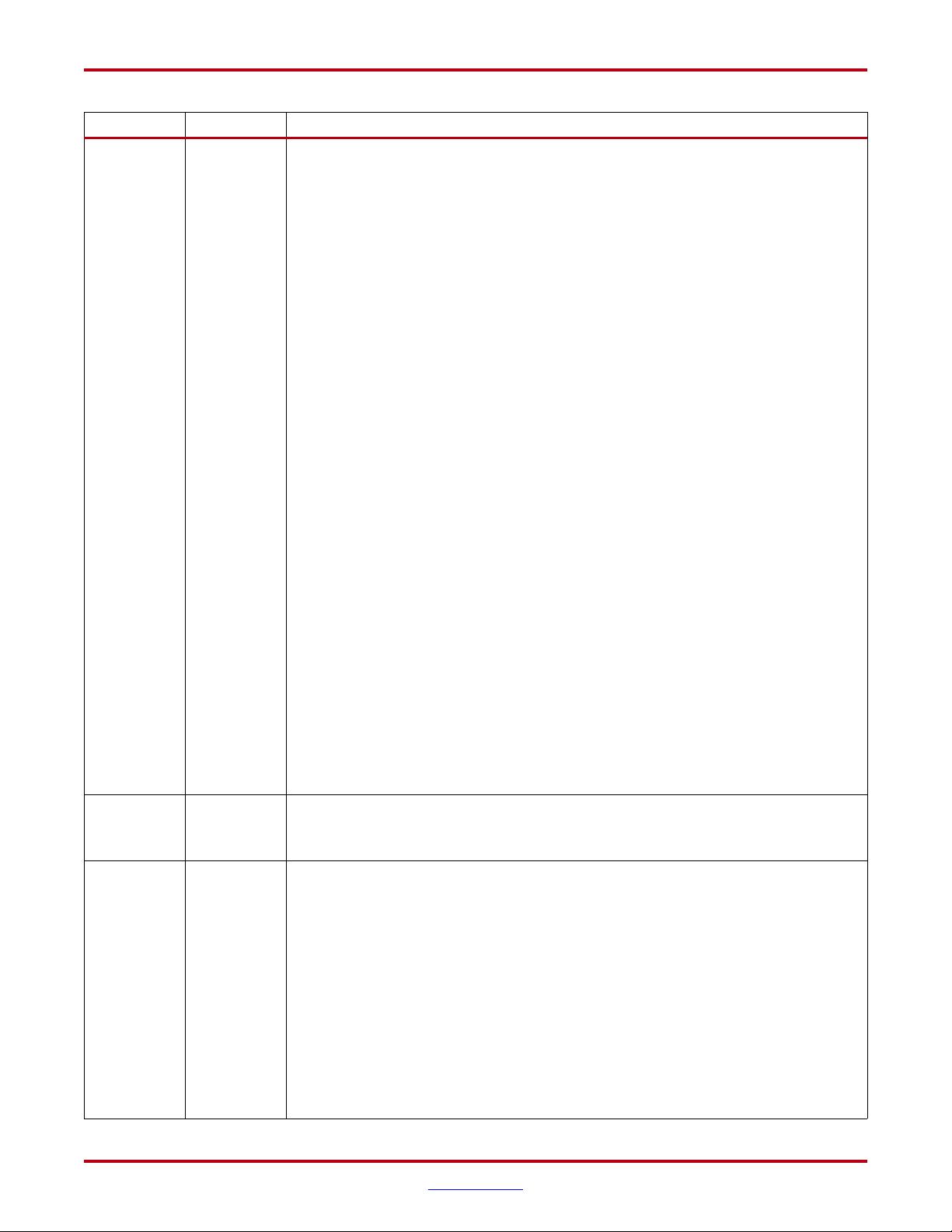

The following table shows the revision history for this document.

Date Version Revision

03/01/2011 1.0 Initial Xilinx release.

03/28/2011 1.1 Chapter 1, Removed Table 1-4: GTX Transceiver Channels by Device/Package (Kintex-7

FPGAs) and added link to UG475: 7 Series FPGAs Packaging and Pinout Specifications.

Updated Table B-1.

UG476 (v1.12) December 19, 2016 www.xilinx.com 7 Series FPGAs GTX/GTH Transceivers User Guide

07/08/2011 1.2 Chapter 1, updated PCS and PMA features in Table 1-1.

Chapter 2, revised ODIV2 attribute in Table 2-1 and removed REFCLK_CTRL from

Table 2-2. Revised Reference Clock Selection and Distribution. Updated line rate and

lock range in Channel PLL. Updated D factor in Table 2-8. Revised description of

CPLLLOCKDETCLK in Table 2-9. Renamed CPLL_RXOUT_DIV to RXOUT_DIV and

CPLL_TXOUT_DIV to TXOUT_DIV and updated their descriptions in Table 2-10.

Updated line rate in Quad PLL. Revised VCO in Figure 2-11. Updated N valid setting

and added D factor to Table 2-13. Updated QPLLLOCKDETCLK description in

Table 2-14. Updated QPLL_CFG description in Table 2-15. Added RXOUT_DIV and

TXOUT_DIV attributes to Table 2-15. Added CFGRESET and PCSRSVDOUT ports to

Table 2-24. Corrected GTTXRESET name in Figure 2-16. Revised PLL Power Down.

Chapter 3, updated line rate in TXUSRCLK and TXUSRCLK2 Generation. Added Using

TXOUTCLK to Drive the TX Interface. Deleted TXRUNDISP[7:0] port from Table 3-7.

Added RX to and updated description of GEARBOX_MODE in Table 3-9. Added

Enabling the TX Gearbox, TX Gearbox Bit and Byte Ordering, TX Gearbox Operating

Modes, External Sequence Counter Operating Mode, Internal Sequence Counter

Operating Mode (GTX Transceiver Only), Table 3-10, and Table 3-11. Updated

TXPHALIGNDONE description in Table 3-17. Updated Figure 3-19 and its relevant

notes in Using TX Buffer Bypass in Single-Lane Auto Mode (GTX Transceiver Only).

Added Using TX Buffer Bypass in Multi-Lane Manual Mode (GTX and GTH

Transceivers). Updated TX Polarity Control. Updated Figure 3-28. Renamed

CPLL_TXOUT_DIV to TXOUT_DIV in Serial Clock Divider, Table 3-25, and Table 3-26.

Added TXDLYBYPASS to Table 3-26. Changed TXPOSTCURSOR range in Figure 3-29.

Chapter 4, updated programmable voltage values in Table 4-2. Added GTX and GTH

Use Modes—RX Termination. Updated RXOOBRESET and added

RXELECIDLEMODE[1:0] to Table 4-7. Updated Figure 4-23. Renamed

CPLL_RXOUT_DIV to RXOUT_DIV in Table 4-23. Updated bullets in Parallel Clock

Divider and Selector. Added RXDLYBYPASS toTable 4-24. Renamed

CPLL_RXOUT_DIV to RXOUT_DIV in Table 4-24 and Table 4-25. Added Eye Scan

Architecture, Figure 4-26, Figure 4-27, and Figure 4-28. Added Ports and Attributes and

Table 4-26, and Table 4-27. Updated Manual Alignment and Figure 4-36, and added

Figure 4-37. Updated RXSLIDE description in Table 4-32. Updated description of

SHOW_REALIGN_COMMA, RXSLIDE_MODE, and RXSLIDE_AUTO_WAI T, and

renamed RXRECCLK to RXOUTCLK and SHOW_ALIGN_COMMA to

SHOW_REALIGN_COMMA in Table 4-33. Revised RX Running Disparity. Replaced

RX8B10BEN description in and deleted RXRUNDISP[7:0} from Table 4-34. Added RX

CDR to Figure 4-40. Revised RXPHALIGNDONE description in Table 4-36. Revised

Using RX Buffer Bypass in Single-Lane Auto Mode (GTX Transceiver Only) and

updated Figure 4-41. Added Using RX Buffer Bypass in Multi-Lane Manual Mode (GTX

and GTH Transceivers). Added RX CDR to Figure 4-49. Revised descriptions of

CLK_COR_MAX_LAT, CLK_COR_MIN_LAT, and CLK_COR_SEQ_LEN in Table 4-44.

Modified Using RX Clock Correction, added Enabling Clock Correction, modified

Setting RX Elastic Buffer Limits and renamed CLK_COR_ADJ_LEN to

CLK_COR_SEQ_LEN, added Setting Clock Correction Sequences, Clock Correction

Options, and Monitoring Clock Correction. Modified RXCHBONDLEVEL description

in Table 4-47

. Added Using RX Channel Bonding, Enabling Channel Bonding. Added

Setting Channel Bonding Sequences. Added Setting the Maximum Skew.

Date Version Revision

7 Series FPGAs GTX/GTH Transceivers User Guide www.xilinx.com UG476 (v1.12) December 19, 2016

07/08/2011 1.2

(Continued)

Added Precedence between Channel Bonding and Clock Correction. Revised

description of RXGEARBOXSLIP in Table 4-49. Replaced description of

GEARBOX_MODE in Table 4-50. Added Enabling the RX Gearbox. Added RX Gearbox

Operating Modes. Added RX Gearbox Block Synchronization. Renamed to RXRECCLK

to RXOUTCLK in RXUSRCLK and RXUSRCLK2 Generation. Updated description of

RX_INT_DATAWIDTH in Table 4-55.

Chapter 5, added Figure 5-2. Added Analog Power Supply Pins, Table 5-2, and

Table 5-3. Updated Figure 5-9. Revised Unused Reference Clocks. Deleted LVDS section.

Revised Printed Circuit Board and added Table 5-6. Added PCB Design Checklist and

Table 5-7.

Chapter 6, added Gen3 to RX Buffer in Table 6-1. Added TXCHARDISPMODE[0] to

Table 6-2. Updated description of TXDEEMPH and RXELECIDLE in Table 6-2. Updated

PCI Express Use Mode and Gen3 for RXBUF_EN and RX_XCLK_SEL in Table 6-4,

added PIPE Control Signal and Table 6-5. Updated Reference Clock and Table 6-6, and

added Table 6-7. Modified Parallel Clock (PCLK), added Figure 6-1, added introductory

paragraph to and modified Figure 6-2. Revised Rate Change between Gen1 and Gen2

Speeds. Updated Figure 6-6. Revised Using DRP During Rate Change to Enter or Exit

Gen3 Speed. Updated Gen3 for RXBUF_EN and RX_XCLK_SEL in Table 6-8. Updated

PCI Express Channel Bonding, and added Binary-Tree Example. Added XAUI Use

Model and Table 6-11 through Table 6-14

.

Appendix A, Placement Information by Package, updated content.

Appendix B, Placement Information by Device, expanded Table B-1.

Appendix D, DRP Address Map of the GTX/GTH Transceiver, removed CPLL_ from

CPLL_RXOUT_DIV and CPLL_TXOUT_DIV in Table D-2.

Renamed CPLL_TXOUT_DIV to TXOUT_DIV and CPLL_RXOUT_DIV to RXOUT_DIV

throughout. Removed CPLL and CPLL_ prefix throughout. Renamed PLL to CPLL

throughout.

07/28/2011 1.2.1 Reformatted Table 3-17, Table 3-30, and Table 4-10.

11/16/2011 1.3 Appendix A, Placement Information by Package, added Virtex-7 FPGA packages.

Appendix B, Placement Information by Device, added Table B-2.

04/04/2012 1.4 Added GTH transceivers throughout.

Chapter 1: Updated Table 1-1.

Chapter 2: Updated description of O and ODIV2 ports in Table 2-1. Updated

CLKSWING_CFG type to Binary in Table 2-2. Updated CLKSWING_CFG setting in

Table 2-3. Updated Channel PLL and Quad PLL. Updated Figure 2-15. Updated

GTX/GTH Transceiver TX Reset in Response to Completion of Configuration. Updated

Figure 2-20. Updated GTX/GTH Transceiver RX Reset in Response to Completion of

Configuration. In Table 2-33, updated RXPD[1:0] clock domain to Async. Added Digital

Monitor.

Chapter 3: Updated Figure 3-1. Added BUFH to Figure 3-4 and Figure 3-5, and notes for

each figure. Updated Running Disparity. Updated TX Gearbox. Updated Figure 3-14. In

Table 3-17, updated description of TXPHDLYPD and added TXSYNCMODE,

TXSYNCALLIN, TXSYNCIN, TXSYNCOUT, and TXSYNCDONE. Added

TXSYNC_MULTI_LANE, TXSYNC_SKIP_DA, and TXSYNC_OVRD to Table 3-18.

Updated notes after Figure 3-23. Added TX Phase Interpolator PPM Controller.

Updated Figure 3-28, including notes 2 and 6. In Table 3-28, updated descriptions of

TXDIFFCTRL[3:0], TXELECIDLE, TXINHIBIT, TXPOSTCURSOR[4:0],

TXPRECURSOR[4:0], and GTXTXP/GTXTXN. In Table 3-32, updated RXPD[1:0] clock

domain to Async.

Date Version Revision

UG476 (v1.12) December 19, 2016 www.xilinx.com 7 Series FPGAs GTX/GTH Transceivers User Guide

04/04/2012 1.4

(Cont’d)

Chapter 4: Updated Table 4-2. Updated GTX and GTH Use Modes—RX Termination

and RX Equalizer (DFE and LPM). In Table 4-11 and Table 4-15, replaced

RXDFEOSHOLD, RXDFEOSOVRDEN, and RX_DFE_OS_CFG with RXOSHOLD,

RXOSOVRDEN, and RX_OS_CFG, respectively. In Table 4-11, merged RX_DFE_LPM

and HOLD_DURING_EIDLE into RX_DFE_LPM_HOLD_DURING_EIDLE, and

removed IAS_CFG. Added GTX Use Modes, including Figure 4-20, Table 4-12, and

Table 4-13. Updated Figure 4-23, including note 2. In Table 4-26, added RXLPMEN. In

Table 4-27, removed A_RXLPMEN, updated ES_EYE_SCAN_EN, and added

PMA_RSV2[5], USE_PCS_CLK_PHASE_SEL, and ES_CLK_PHASE_SEL. Updated

description of RX_PRBS_ERR_CNT in Table 4-31. Updated Alignment Status Signals

and Manual Alignment. Updated description of RXBYTEISALIGNED in Table 4-32.

Added COMMA_ALIGN_LATENCY to Table 4-33. Added sentence about use of

RXSLIDE_MODE to RX Buffer Bypass. In Table 4-36, updated description of

RXPHDLYPD, and added RXSYNCMODE, RXSYNCALLIN, RXSYNCIN,

RXSYNCOUT, and RXSYNCDONE. In Table 4-37, added RXSYNC_MULTI_LANE,

RXSYNC_SKIP_DA, and RXSYNC_OVRD. Updated Using RX Buffer Bypass in

Single-Lane Auto Mode (GTX Transceiver Only) heading. Updated notes after

Figure 4-45. Updated description of FTS_LANE_DESKEW_CFG in Table 4-48. Updated

Functional Description, page 283. In Table 4-49, updated descriptions of

RXDATAVALID, RXGEARBOXSLIP, RXHEADER, RXHEADERVALID, and

RXSTARTOFSEQ, and added RXSLIDE. Updated description of GEARBOX_MODE in

Table 4-50. Added normal mode to RX Gearbox Operating Modes. Updated Figure 4-65

and RX Gearbox Block (GTH Transceiver).

Chapter 5: Updated Table 5-1, Table 5-6, and Table 5-7. Added LVDS, including

Figure 5-8. In Figure 5-9

, updated value of capacitors from 0.01 μF to 0.1 μF.

Chapter 6: Updated Functional Description, including Table 6-1. Updated description of

RXELECIDLE in Table 6-2. Updated [TX/RX]RATE[2:0] setting in Table 6-4. Updated

[TX/RX]OUT_DIV setting in Table 6-6. Updated QPLL_FBDIV setting in Table 6-7.

PCLK frequency in Parallel Clock (PCLK). Updated Rate Change to Enter or Exit Gen3

Speed. Updated PCI Express Clock Correction. In Table 6-12, updated value of

[TX/RX]_CLK25_DIV from 2 to 7.

Appendix A: Added sentence about leaded package options to first paragraph. Added

GTH Transceiver Package Placement Diagrams.

Appendix B: Added Table B-3.

Appendix D: Updated Table D-1 and Table D-2. Added Table D-3 and Table D-4.

05/07/2012 1.5 Chapter 5: Updated recommendations for MGTVCCAUX_G[N] in Table 5-7.

Appendix A: Corrected labels in Figure A-50, Figure A-61, Figure A-63, Figure A-91,

and Figure A-92.

09/11/2012 1.6 Chapter 2: Updated Figure 2-1. Updated CLKSWING_CFG in Table 2-2. Added

GTREFCLKMONITOR to Table 2-4. Added OUTREFCLK_SEL_INV to Table 2-5.

Added REFCLKOUTMONITOR to Table 2-6. Added Single External Reference Clocks

Use Model and Multiple External Reference Clocks Use Model. Updated Channel PLL

and Quad PLL. Added note to Table 2-10. Added QPLL Settings for Common Protocols.

Updated Table 2-12

. Removed QPLL_CFG from Attribute column for Factor N in

Table 2-13. Added Table 2-27 and descriptions of reset situations. Updated description

of RXRESETDONE in Table 2-28. Replaced RXCDRRESET_TIME with

RXCDRPHRESET_TIME in Table 2-29. Added Table 2-32 and descriptions of reset

situations. Updated description of loopback modes in Loopback. Updated description

of DMONITOR_CFG[23:0] and added RX_DEBUG_CFG, PCS_RSVD_ATTR[6], and

CFOK_CFG[41] to Table 2-41. Updated Verilog code in Capturing the Digital Monitor

Output. In Interpreting the Digital Monitor Output, added bullet for RXDFELF[3:0] and

updated

RXDFEAGC[3:0] for GTX and GTH transceivers.

Date Version Revision

剩余505页未读,继续阅读

资源评论

weixin_41681791

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功