没有合适的资源?快使用搜索试试~ 我知道了~

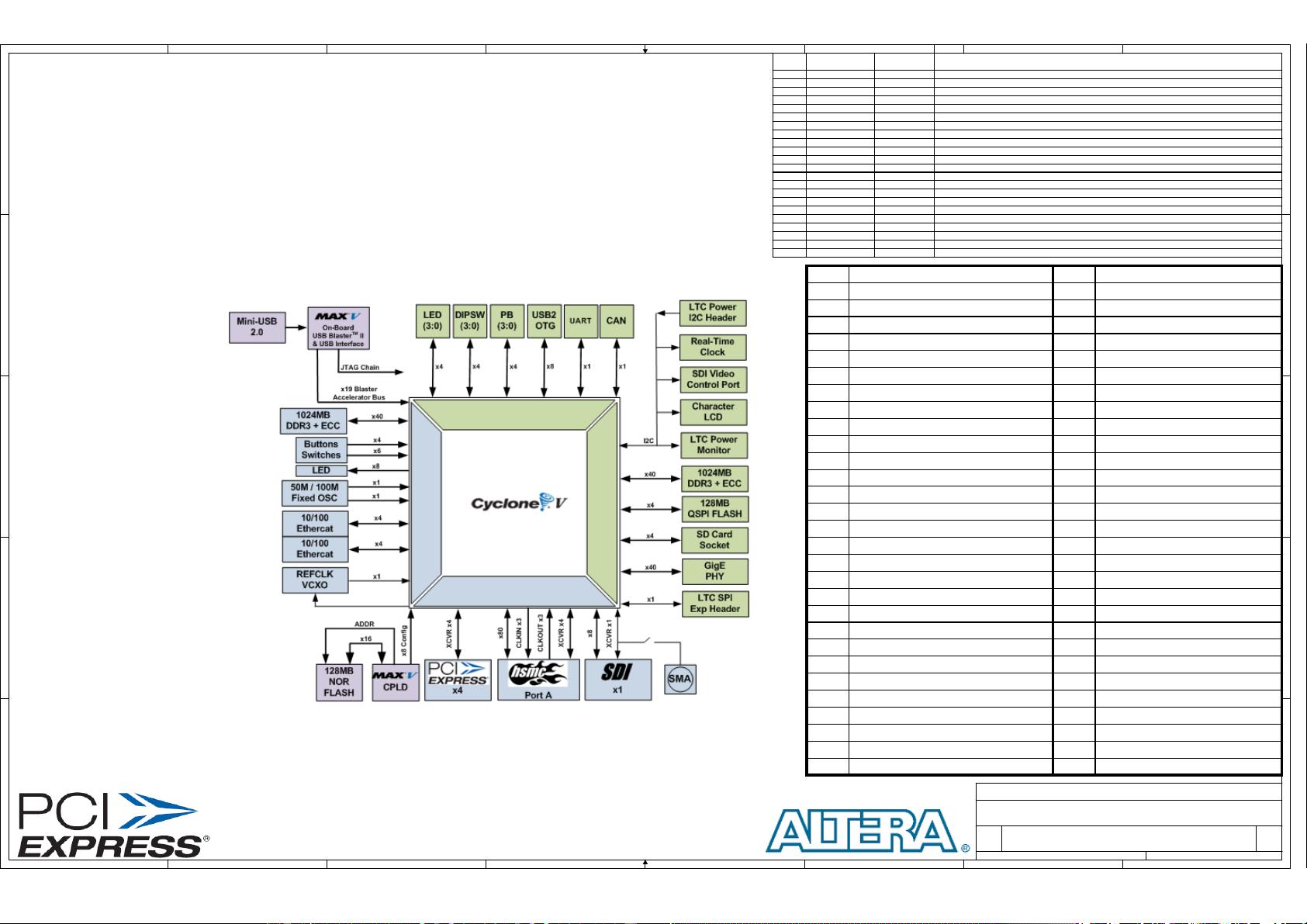

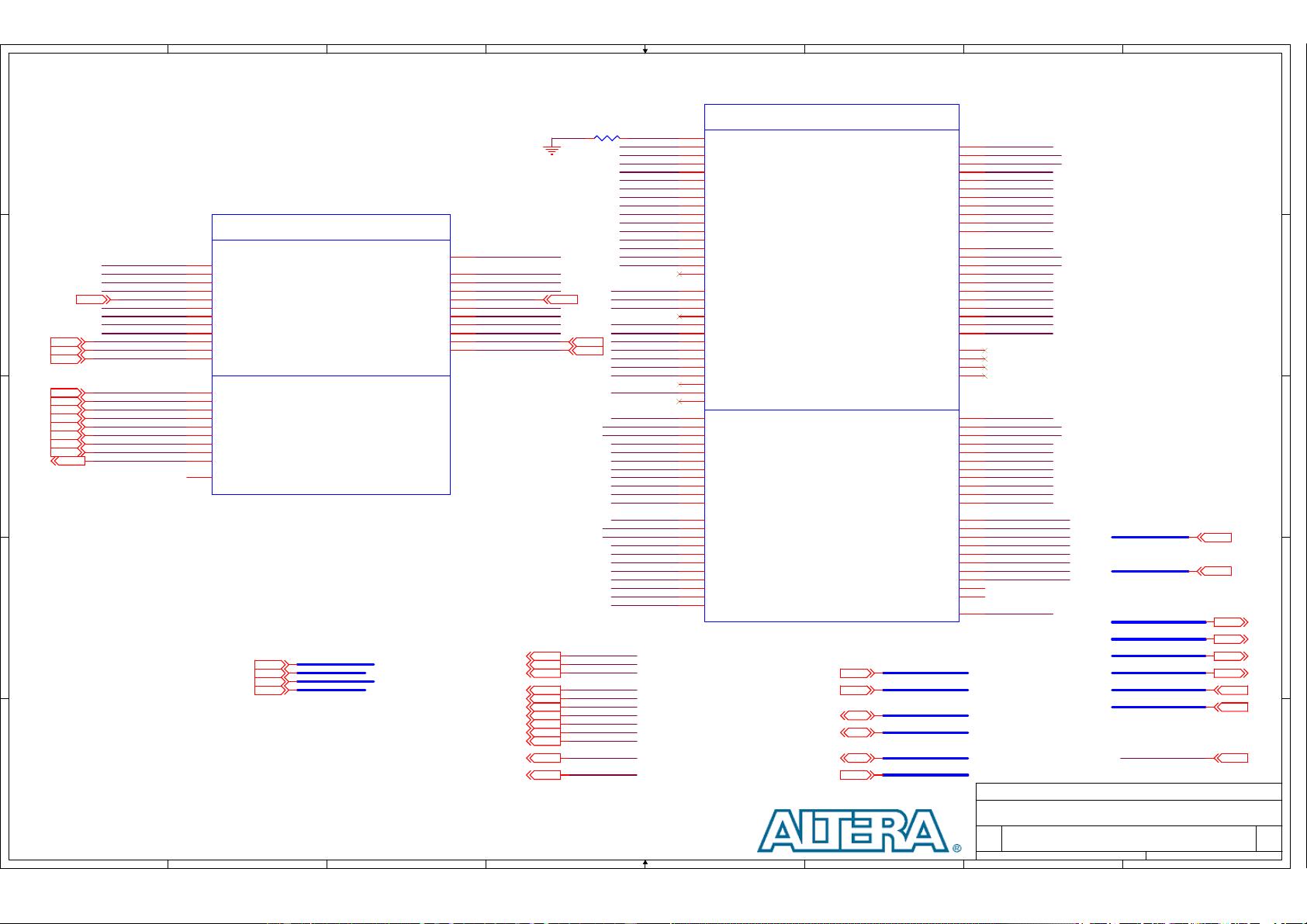

Cyclone V 官方开发板原理图

温馨提示

试读

41页

Cyclone V 官方开发板原理图,Cadence,适合FPGA开发者参考

资源详情

资源评论

资源推荐

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

E E

D D

C C

B B

A A

DESCRIPTION

REV

DATE PAGES

PAGE

DESCRIPTION

2

NOTES:

Title, Notes, Block Diag, Rev. History

1

3

4

7

8

Cyclone V GX SoC Bank 7

9

Cyclone V GX SoC Bank 8

10

11

12

13

14

15

16

PLL

17

JTAG

18

19

20

21

5M2210 System Controller

22

23

24

25

5

6

SDI Cable Driver , SMA & SMB

1543 Parts, 88 Library Parts, 1330 Nets, 6643 Pins

D1 07/29/2013 All INITIAL REVISION A RELEASE

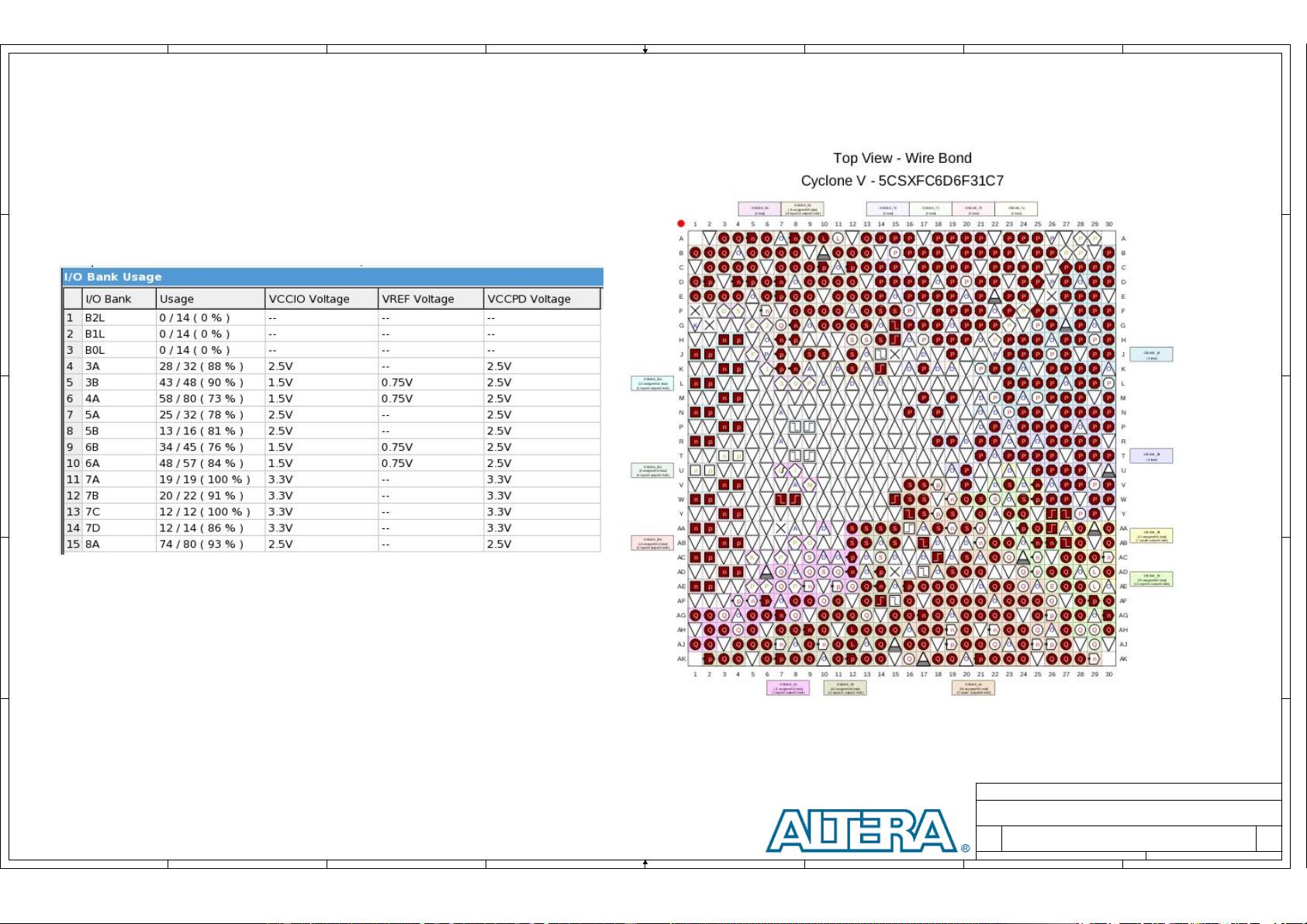

FPGA Package Top

Cyclone V SoC FPGA Development Kit Board

1. Project Drawing Numbers:

Raw PCB

Gerber Files

PCB Design Files

Assembly Drawing

Fab Drawing

Schematic Drawing

PCB Film

Bill of Materials

Schematic Design Files

Functional Specification

PCB Layout Guidelines

Assembly Rework

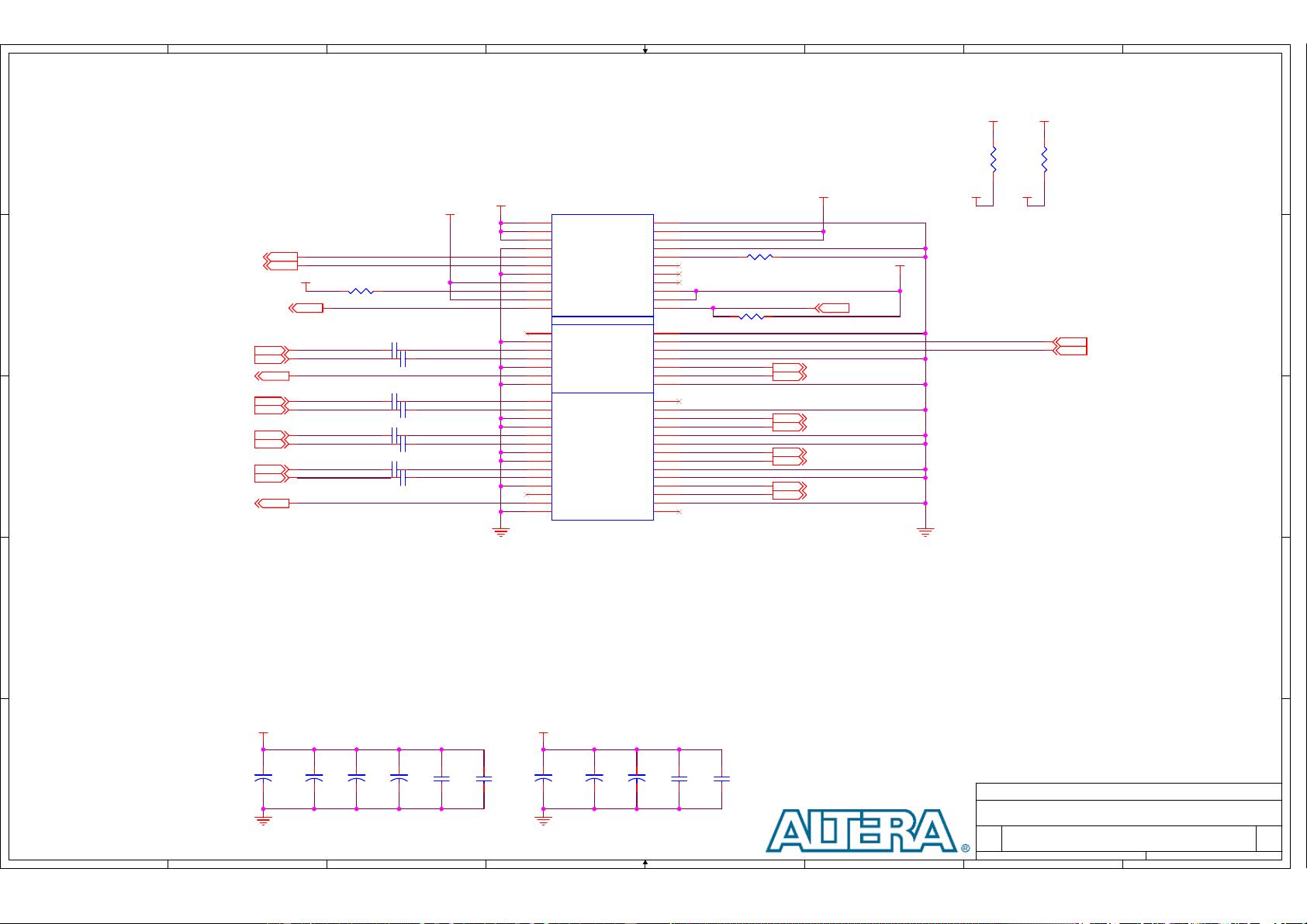

PCI Express Edge Connector

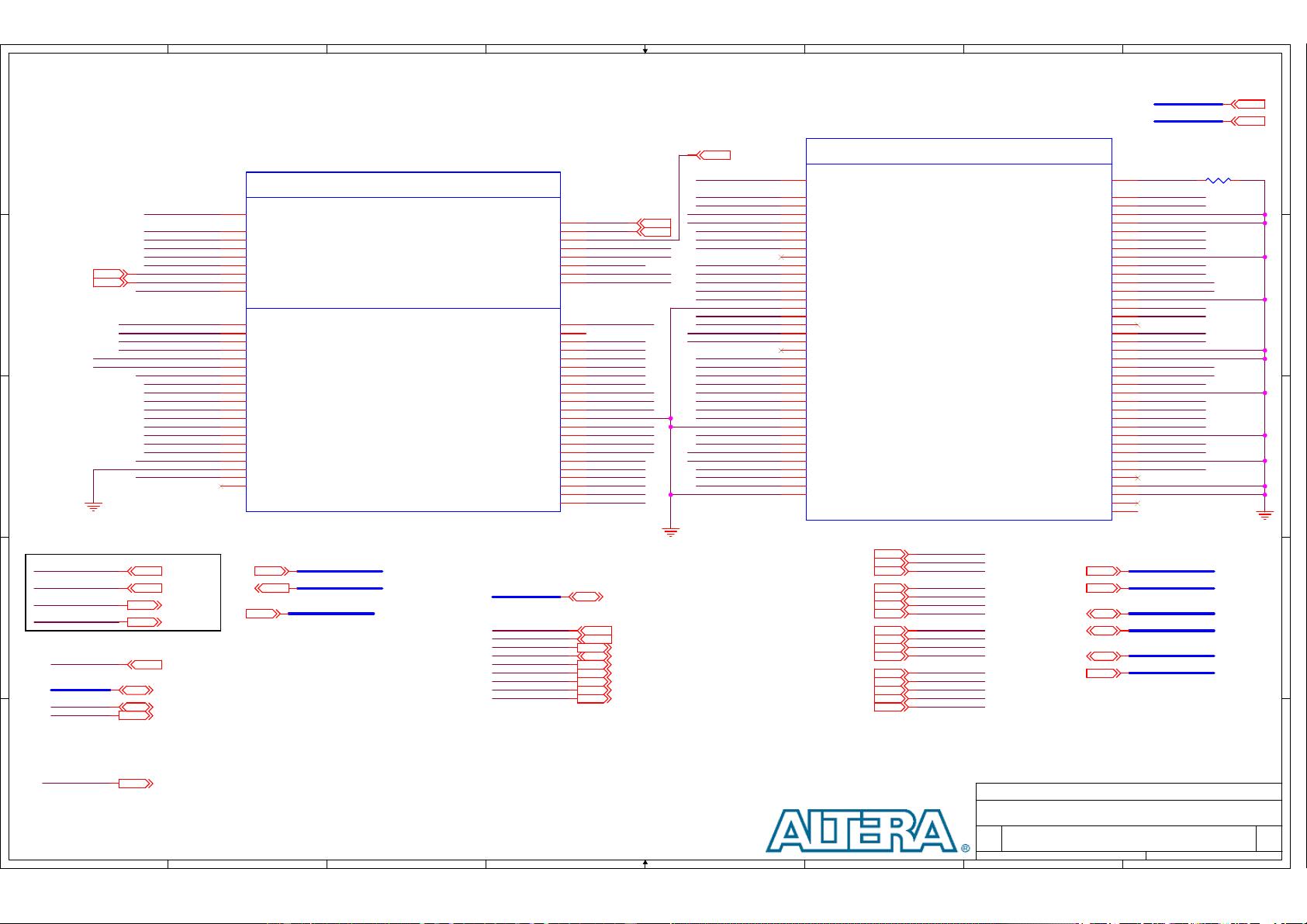

Cyclone V GX SoC Bank 5,6

Cyclone V GX SoC Bank 3,4

Cyclone V GX SoC Transceiver Banks

2.

100-0321003-D1

110-0321003-D1

120-0321003-D1

130-0321003-D1

140-0321003-D1

150-0321003-D1

160-0321003-D1

170-0321003-D1

180-0321003-D1

210-0321003-D1

220-0321003-D1

320-0321003-D1

26

27

28

29

PAGE

DESCRIPTION

HSMC PORT A

10/100/1000 Ethernet - HPS

Cyclone V GX SoC Clocks

Cyclone V GX SoC Configuration

1024MB DDR3 ( x32 ) - FPGA

FLASH , EPCQ

10/100M Ethernet - FPGA

1024MB DDR3 ( x32 + ECC ) - HPS

QSPI FLASH & RESET Circuit

USB2.0 & Micro SD Card

User I/O , RTC

UART , CAN

On - Board USB Blaster II

FPGA Power Monitor

HPS Power Monitor

Power 1 - DC I/P & 12V , 3.3V O/P

Power 2

Power 3 - 1.5V FPGA

30

31

Power 3 - 2.5V FPGA

32

Power 3 - 2.5V HPS

33

Power 3 - 1.5V & 1.5V HPS

34

Power 3 - 3.3V HPS

35

Power 1.1V_HPS , 5.0V , 1.8V

36

Power 4 - Linear Regulators

37

Power 6 - Power & Temp Monitor

38

CycloneV GX SOC Power

39

CycloneV GX SOC Ground

40 Decoupling

41

Changes History

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

141Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

141Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

141Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

E E

D D

C C

B B

A A

FPGA Package Top View

XCVR BANK QR2

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

241Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

241Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

241Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

E E

D D

C C

B B

A A

PCI Express Connector

PCIE_TX_C_P0

PCIE_TX_C_N0

PCIE_TX_C_N1

PCIE_TX_C_P1

PCIE_TX_C_N2

PCIE_TX_C_P2

PCIE_TX_C_N3

PCIE_TX_C_P3

PCIE_SMBCLK

PCIE_SMBDAT

3.3V

12V3.3V

3.3V_EXP 12V_EXP12V_EXP

12V_EXP

3.3V_EXP

3.3V_EXP

12V_EXP 3.3V_EXP

PCIE_PERSTn(4,11)

PCIE_TX_P0(8)

PCIE_TX_N0 (8)

PCIE_TX_P1(8)

PCIE_TX_N1 (8)

PCIE_TX_N2 (8)

PCIE_TX_P2(8)

PCIE_TX_P3(8)

PCIE_TX_N3 (8)

PCIE_PRSNT2_X1 (9)

PCIE_PRSNT2_X4 (9)

PCIE_REFCLK_SYN_N(10)

PCIE_REFCLK_SYN_P(10)

PCIE_WAKEn (11)

PCIE_SMBCLK(9)

PCIE_SMBDAT(9)

PCIE_RX_N0(8)

PCIE_RX_P0(8)

PCIE_RX_N1(8)

PCIE_RX_P1(8)

PCIE_RX_P2(8)

PCIE_RX_N2(8)

PCIE_RX_N3(8)

PCIE_RX_P3(8)

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

341Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

341Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

341Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

C232

220uF

16V

C678

22uF

25V

C215

220uF

16V

R262 4.70K, 1%

C684

22uF

25V

C662 0.1uF

C673 0.1uF

C656 0.1uF

R271 4.7K

KEY

X4

X1

J25

PCIE-064-02-F-D-TH

+12V

B1

+12V

B2

+12V

B3

GND

B4

SMCLK

B5

SMDAT

B6

GND

B7

+3_3V

B8

JTAG_TRSTN

B9

+3_3VAUX

B10

WAKE_N

B11

RSVD1

B12

GND

B13

PET0P

B14

PET0N

B15

GND

B16

PRSNT2_N_X1

B17

GND

B18

PET1P

B19

PET1N

B20

GND

B21

GND

B22

PET2P

B23

PET2N

B24

GND

B25

GND

B26

PET3P

B27

PET3N

B28

GND

B29

RSVD3

B30

PRSNT2_N_X4

B31

GND

B32

PRSNT1_N

A1

+12V

A2

+12V

A3

GND

A4

JTAG_TCK

A5

JTAG_TDI

A6

JTAG_TDO

A7

JTAG_TMS

A8

+3_3V

A9

+3_3V

A10

PERST_N

A11

GND

A12

REFCLK+

A13

REFCLK-

A14

GND

A15

PER0P

A16

PER0N

A17

GND

A18

RSVD2

A19

GND

A20

PER1P

A21

PER1N

A22

GND

A23

GND

A24

PER2P

A25

PER2N

A26

GND

A27

GND

A28

PER3P

A29

PER3N

A30

GND

A31

RSVD4

A32

C649 0.1uF

C231

47uF

20V

C650 0.1uF

C687

22uF

25V

C235

47uF

20V

C683

22uF

25V

R547

0_Ohms

C637 0.1uF

R255 4.70K, 1%

C238

47uF

20V

C638 0.1uF

R554

0_Ohms

C670 0.1uF

C237

220uF

16V

C236

47uF

20V

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

E E

D D

C C

B B

A A

Cyclone V GX SoC Bank 3 & 4

PCIE INTERFACE

HSMC LVCMOS INTERFACE

2.5 Volt

1.5 Volt

1.5 Volt

LVCMOS Only

DDR3_FPGA_CLK_P

DDR3_FPGA_CASn

DDR3_FPGA_RASn

DDR3_FPGA_WEn

DDR3_FPGA_CSn

DDR3_FPGA_BA2

DDR3_FPGA_BA1

DDR3_FPGA_BA0

DDR3_FPGA_CLK_N

DDR3_FPGA_A7

DDR3_FPGA_A8

DDR3_FPGA_A13

DDR3_FPGA_A6

DDR3_FPGA_A12

DDR3_FPGA_A9

DDR3_FPGA_A14 DDR3_FPGA_A4

DDR3_FPGA_A10

DDR3_FPGA_A5

DDR3_FPGA_A11

DDR3_FPGA_A1

DDR3_FPGA_A0

DDR3_FPGA_DM1

DDR3_FPGA_DM0

DDR3_FPGA_ODT

DDR3_FPGA_RESETn

DDR3_FPGA_CKE

DDR3_FPGA_DM2

DDR3_FPGA_DM3

DDR3_FPGA_DQ7

DDR3_FPGA_DQ0

DDR3_FPGA_DQS_P0

DDR3_FPGA_DQ13

DDR3_FPGA_DQ14

DDR3_FPGA_DQ8

DDR3_FPGA_DQ2

DDR3_FPGA_DQS_P1

DDR3_FPGA_DQS_N1

DDR3_FPGA_DQS_N0

DDR3_FPGA_DQ10

DDR3_FPGA_DQ4

DDR3_FPGA_DQ15

DDR3_FPGA_DQ9

DDR3_FPGA_DQ3

DDR3_FPGA_DQ1

DDR3_FPGA_DQ12

DDR3_FPGA_DQ6

DDR3_FPGA_DQ11

DDR3_FPGA_DQ5

DDR3_FPGA_DQ23

DDR3_FPGA_DQ16

DDR3_FPGA_DQS_P2

DDR3_FPGA_DQ29

DDR3_FPGA_DQ30

DDR3_FPGA_DQ24

DDR3_FPGA_DQ18

DDR3_FPGA_DQS_P3

DDR3_FPGA_DQS_N3

DDR3_FPGA_DQS_N2

DDR3_FPGA_DQ26

DDR3_FPGA_DQ20

DDR3_FPGA_DQ31

DDR3_FPGA_DQ25

DDR3_FPGA_DQ19

DDR3_FPGA_DQ17

DDR3_FPGA_DQ28

DDR3_FPGA_DQ22

DDR3_FPGA_DQ27

DDR3_FPGA_DQ21

HSMA_D0

HSMA_D1

HSMA_D2

HSMA_D3

HSMA_SDA

HSMA_SCL

USER_DIPSW_FPGA1

USER_DIPSW_FPGA3

USER_DIPSW_FPGA0

USER_DIPSW_FPGA2

USER_PB_FPGA0

USER_PB_FPGA1

USB_B2_DATA[7:0]

USB_FULL

USB_EMPTY

USB_SCL

USB_SDA

USB_B2_CLK

USB_RESETn

USB_OEn

USB_RDn

USB_WRn

DDR3_FPGA_DM3

DDR3_FPGA_DM2

DDR3_FPGA_CLK_P

DDR3_FPGA_CASn

DDR3_FPGA_RASn

DDR3_FPGA_WEn

DDR3_FPGA_CSn

DDR3_FPGA_BA2

DDR3_FPGA_ODT

DDR3_FPGA_RESETn

DDR3_FPGA_BA1

DDR3_FPGA_CKE

DDR3_FPGA_BA0

DDR3_FPGA_CLK_N

DDR3_FPGA_DM0

DDR3_FPGA_DM1

HSMA_PRSNTn

USB_B2_DATA0

USB_B2_DATA1

USB_B2_DATA2

USB_B2_DATA3

USB_B2_DATA4

USB_B2_DATA5

USB_B2_DATA6

USB_B2_DATA7

USB_FULL

USB_EMPTY

USB_SCL

USB_SDA

USB_B2_CLK

USB_RESETn

USB_OEn

USB_RDn

USB_WRn

RZQIN_1_5V

USER_LED_FPGA0

PCIE_PERSTn

HSMA_CLK_OUT_P1

HSMA_CLK_OUT_N1

HSMA_CLK_IN_P1

HSMA_CLK_IN_N1

HSMA_SDA(17)

HSMA_SCL(17)

HSMA_D[3:0](17)

ENET2_RX_D[3..0](5,19)

ENET2_TX_D[3..0](5,19)

HSMA_PRSNTn(16,17,23)

USB_B2_DATA[7:0] (25)

USB_FULL (25)

USB_EMPTY (25)

USB_SDA (25)

USB_RESETn (25)

USB_OEn (25)

USB_RDn (25)

USB_WRn (25)

USB_SCL (25)

USB_B2_CLK (16,25)

DDR3_FPGA_DM[3:0] (13)

DDR3_FPGA_BA[2:0] (13)

DDR3_FPGA_DQS_P[3:0] (13)

DDR3_FPGA_DQS_N[3:0] (13)

DDR3_FPGA_A[14:0] (9,13)

DDR3_FPGA_DQ[31:0] (13)

DDR3_FPGA_CKE(13)

DDR3_FPGA_CLK_P(13)

DDR3_FPGA_CLK_N(13)

DDR3_FPGA_DM2(13)

DDR3_FPGA_DM3(13)

DDR3_FPGA_CSn(13)

DDR3_FPGA_WEn(13)

DDR3_FPGA_RASn(13)

DDR3_FPGA_CASn(13)

DDR3_FPGA_BA0(13)

DDR3_FPGA_BA1(13)

DDR3_FPGA_BA2(13)

DDR3_FPGA_RESETn(13)

DDR3_FPGA_ODT(13)

DDR3_FPGA_DM1(13)

DDR3_FPGA_DM0(13)

USER_DIPSW_FPGA[3:0] (23)

USER_PB_FPGA[1:0] (23)

SDI_CLK148_UP (8)

SDI_CLK148_DN (8)

USER_LED_FPGA[3:0] (9,23)

P1TXERR(19)

P0TXERR(19)

ENET_DUAL_RESETn(19,21)

PCIE_PERSTn(3,11)

HSMA_CLK_OUT_P1(17)

HSMA_CLK_OUT_N1(17)

HSMA_CLK_IN_P1(17)

HSMA_CLK_IN_N1(17)

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

441Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

441Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

441Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Bank 4A

CYCLONE V GX SoC BANK 4

5CSXFC6D_F896

U21B

PART_NUMBER = 5CGXFC7D7F31C8NES

Manufacturer = Altera Corp

DIFFIO_TX_B61n,DQ8B,GND

AJ22

DIFFIO_RX_B42n,DQ6B,B_DQ_0

AF18

DIFFIO_RX_B62n,DQ8B,B_DQ_20

AF21

RZQ_0,DIFFIO_TX_B41n

AG17

DIFFIO_RX_B42p,DQ6B,B_DQ_1

AE17

DIFFIO_RX_B62p,DQ8B,B_DQ_21

AF20

DIFFIO_TX_B41p,DQ6B,B_DQ_2

AG16

DIFFIO_TX_B61p,DQ8B,B_DQ_22

AH23

DIFFIO_TX_B64n,DQ8B,B_DQ_23

AK24

DIFFIO_TX_B44n,DQ6B,B_DQ_3

AF16

DIFFIO_RX_B63n,GND

AA19

DIFFIO_RX_B43n,DQSn6B,B_DQS#_0

W16

DIFFIO_TX_B64p,DQ8B,B_DM_2

AK23

DIFFIO_RX_B63p,GND

Y18

DIFFIO_RX_B66n,DQ9B,B_DQ_24

AF24

DIFFIO_TX_B44p,B_ODT_0

AE16

DIFFIO_TX_B65n,GND

AJ25

DIFFIO_RX_B43p,DQS6B,B_DQS_0

V16

DIFFIO_RX_B46n,DQ6B,B_DQ_4

AH20

DIFFIO_RX_B66p,DQ9B,B_DQ_25

AF23

DIFFIO_TX_B45n,DQ6B,B_ODT_1

AK16

DIFFIO_TX_B65p,DQ9B,B_DQ_26

AJ24

DIFFIO_TX_B68n,DQ9B,B_DQ_27

AK26

DIFFIO_RX_B46p,DQ6B,B_DQ_5

AG21

DIFFIO_RX_B67n,DQSn9B,B_DQS#_3

AD19

DIFFIO_TX_B45p,DQ6B,B_DQ_6

AJ16

DIFFIO_TX_B68p,GND

AJ26

DIFFIO_RX_B67p,DQS9B,B_DQS_3

AC20

DIFFIO_RX_B70n,DQ9B,B_DQ_28

AE23

DIFFIO_TX_B48p,DQ6B,B_DM_0

AH17

DIFFIO_TX_B69n,DQ9B,GND

AH25

DIFFIO_TX_B48n,DQ6B,B_DQ_7

AH18

DIFFIO_RX_B50n,DQ7B,B_DQ_8

AK18

DIFFIO_RX_B70p,DQ9B,B_DQ_29

AE22

DIFFIO_TX_B69p,DQ9B,B_DQ_30

AG25

DIFFIO_TX_B72n,DQ9B,B_DQ_31

AK27

DIFFIO_RX_B71n,GND

W19

DIFFIO_TX_B72p,DQ9B,B_DM_3

AJ27

DIFFIO_RX_B71p,GND

V18

DIFFIO_RX_B74n,DQ10B,B_DQ_32

AD21

DIFFIO_TX_B73n,GND

AK29

DIFFIO_RX_B74p,DQ10B,B_DQ_33

AD20

DIFFIO_TX_B73p,DQ10B,B_DQ_34

AK28

DIFFIO_TX_B76n,DQ10B,B_DQ_35

AH27

DIFFIO_RX_B75n,DQSn10B,B_DQS#_4

AA20

DIFFIO_TX_B76p,GND

AG26

DIFFIO_RX_B75p,DQS10B,B_DQS_4

Y19

DIFFIO_RX_B78n,DQ10B,B_DQ_36

AC23

DIFFIO_TX_B77n,DQ10B,GND

AF26

DIFFIO_RX_B78p,DQ10B,B_DQ_37

AC22

DIFFIO_TX_B77p,DQ10B,B_DQ_38

AF25

DIFFIO_TX_B80n,DQ10B,B_DQ_39

AE24

DIFFIO_RX_B79n,GND

AB21

DIFFIO_TX_B80p,DQ10B,B_DM_4

AD24

DIFFIO_RX_B79p,GND

AA21

DIFFIO_TX_B60p,B_RESET#

AK21

DIFFIO_RX_B59n,DQSn8B,B_DQS#_2

AA18

DIFFIO_RX_B58n,DQ8B,B_DQ_16

AE19

DIFFIO_TX_B57n,GND

AH22

DIFFIO_TX_B52p,B_CKE_1

AJ19

DIFFIO_TX_B56p,DQ7B,B_DM_1

AG23

DIFFIO_RX_B54p,DQ7B,B_DQ_13

AF19

DIFFIO_RX_B58p,DQ8B,B_DQ_17

AE18

DIFFIO_TX_B53n,DQ7B,B_CKE_0

AJ21

DIFFIO_TX_B52n,DQ7B,B_DQ_11

AK19

DIFFIO_RX_B51p,DQS7B,B_DQS_1

V17

DIFFIO_TX_B57p,DQ8B,B_DQ_18

AG22

DIFFIO_TX_B53p,DQ7B,B_DQ_14

AJ20

DIFFIO_TX_B56n,DQ7B,B_DQ_15

AH24

DIFFIO_RX_B59p,DQS8B,B_DQS_2

Y17

DIFFIO_RX_B50p,DQ7B,B_DQ_9

AJ17

DIFFIO_TX_B60n,DQ8B,B_DQ_19

AK22

DIFFIO_TX_B49p,DQ7B,B_DQ_10

AG18

DIFFIO_RX_B51n,DQSn7B,B_DQS#_1

W17

DIFFIO_TX_B49n,GND

AH19

DIFFIO_RX_B54n,DQ7B,B_DQ_12

AG20

Bank 3A

Bank 3B

CYCLONE V GX SoC BANK 3

5CSXFC6D_F896

U21A

PART_NUMBER = 5CGXFC7D7F31C8NES

Manufacturer = Altera Corp

DIFFIO_TX_B12p

AF6

DIFFIO_RX_B14n,DQ2B

AJ2

DIFFIO_TX_B29n,DQ4B,B_A_11

AK9

DIFFIO_TX_B33n,GND

AJ10

DIFFIO_RX_B34p,DQ5B,B_BA_1

AJ11

DIFFIO_TX_B33p,DQ5B,B_BA_0

AH10

DIFFIO_TX_B36n,DQ5B,B_A_7

AK13

DIFFIO_RX_B35n,DQSn5B,B_CK#

AA15

DIFFIO_TX_B36p,B_A_6

AK12

DIFFIO_RX_B35p,DQS5B,B_CK

AA14

DIFFIO_RX_B38p,DQ5B,B_A_4

AG15

DIFFIO_RX_B38n,DQ5B,B_A_5

AH15

DIFFIO_TX_B40p,DQ5B,B_A_0

AJ14

DIFFIO_TX_B40n,DQ5B,B_A_1

AK14

DIFFIO_TX_B13n,DQ2B

AH5

DIFFIO_RX_B14p,DQ2B

AJ1

DIFFIO_TX_B13p,DQ2B

AG5

DIFFIO_TX_B16n,DQ2B

AH3

DIFFIO_RX_B15n

AD12

DIFFIO_TX_B16p,DQ2B

AG2

DIFFIO_RX_B15p

AC12

DIFFIO_TX_B28n,DQ4B,B_A_13

AK8

DIFFIO_RX_B27n,DQSn4B,B_CS#_1

AC14

DIFFIO_TX_B28p,B_A_12

AK7

DIFFIO_RX_B27p,DQS4B,B_CS#_0

AB15

DIFFIO_RX_B30n,DQ4B,B_A_9

AH14

DIFFIO_RX_B19n,DQSn3B

AB13

DIFFIO_RX_B11n,DQSn2B

AB12

DIFFIO_RX_B18n,DQ3B

AG11

DIFFIO_RX_B10n,DQ2B

AH2

DIFFIO_TX_B12n,DQ2B

AG6

DIFFIO_RX_B26n,DQ4B,B_A_15

AG13

DIFFIO_TX_B21n,DQ3B

AK4

DIFFIO_TX_B24n,DQ3B

AK6

DIFFIO_RX_B19p,DQS3B

AA13

DIFFIO_RX_B26p,DQ4B,B_A_14

AG12

DIFFIO_RX_B22p,DQ3B

AE13

DIFFIO_TX_B9n

AG7

DIFFIO_RX_B22n,DQ3B

AF13

DIFFIO_RX_B11p,DQS2B

AA12

DIFFIO_TX_B17n

AH9

DIFFIO_TX_B24p,DQ3B

AJ5

DIFFIO_TX_B20n,DQ3B

AK3

DIFFIO_TX_B20p

AK2

DIFFIO_TX_B25p,DQ4B,B_WE#

AJ6

DIFFIO_TX_B21p,DQ3B

AJ4

DIFFIO_TX_B17p,DQ3B

AG10

DIFFIO_TX_B25n,GND

AJ7

DIFFIO_RX_B18p,DQ3B

AF11

DIFFIO_TX_B8p,DQ1B

AF9

DIFFIO_RX_B10p,DQ2B

AG1

DIFFIO_RX_B23n

AE14

DIFFIO_TX_B9p,DQ2B

AF8

DIFFIO_RX_B23p

AD14

DIFFIO_RX_B30p,DQ4B,B_A_8

AH13

DIFFIO_TX_B29p,DQ4B,B_A_10

AJ9

DIFFIO_TX_B32n,DQ4B,B_RAS#

AH8

DIFFIO_TX_B32p,DQ4B,B_CAS#

AH7

DIFFIO_RX_B34n,DQ5B,B_BA_2

AK11

R449

100, 1%

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

E E

D D

C C

B B

A A

Cyclone V GX SoC Bank 5 & 6

Si571 VCXO

2.5 Volt

2.5 Volt

1.5 Volt

1.5 Volt

DDR3_HPS_DQS_P0

DDR3_HPS_DQS_P1

DDR3_HPS_DQS_N1

DDR3_HPS_DQS_N0

DDR3_HPS_DM1

DDR3_HPS_DM0

DDR3_HPS_CLK_P

DDR3_HPS_A7

DDR3_HPS_A3

DDR3_HPS_A8

DDR3_HPS_CASn

DDR3_HPS_RASn

DDR3_HPS_WEn

DDR3_HPS_A13

DDR3_HPS_A6

DDR3_HPS_A12

DDR3_HPS_A2

DDR3_HPS_A9

DDR3_HPS_CSn

DDR3_HPS_BA2

DDR3_HPS_RESETn

DDR3_HPS_BA1

DDR3_HPS_A14

DDR3_HPS_A4

DDR3_HPS_A10

DDR3_HPS_A5

DDR3_HPS_A11

DDR3_HPS_CKE

DDR3_HPS_BA0

DDR3_HPS_CLK_N

DDR3_HPS_A1

DDR3_HPS_A0

DDR3_HPS_DQ7

DDR3_HPS_DQ0

DDR3_HPS_DQ13

DDR3_HPS_DQ14

DDR3_HPS_DQ8

DDR3_HPS_DQ2

DDR3_HPS_DQ10

DDR3_HPS_DQ4

DDR3_HPS_DQ15

DDR3_HPS_DQ9

DDR3_HPS_DQ3

DDR3_HPS_DQ1

DDR3_HPS_DQ12

DDR3_HPS_DQ6

DDR3_HPS_DQ11

DDR3_HPS_DQ5

DDR3_HPS_DQ23

DDR3_HPS_DQ16

DDR3_HPS_DQS_P2

DDR3_HPS_DQ18

DDR3_HPS_DQS_P3

DDR3_HPS_DQS_N3

DDR3_HPS_DQS_N2

DDR3_HPS_DQ20

DDR3_HPS_DQ19

DDR3_HPS_DQ17

DDR3_HPS_DQ22

DDR3_HPS_DQ21

DDR3_HPS_DQ29

DDR3_HPS_DQ30

DDR3_HPS_DQ24

DDR3_HPS_DQ26

DDR3_HPS_DQ31

DDR3_HPS_DQ25

DDR3_HPS_DQ28

DDR3_HPS_DQ27

DDR3_HPS_DM3

DDR3_HPS_DM2

DDR3_HPS_DQ32

DDR3_HPS_DQ39

DDR3_HPS_DQS_P4

DDR3_HPS_DQS_N4

DDR3_HPS_DQ34

DDR3_HPS_DQ35

DDR3_HPS_DQ36

DDR3_HPS_DQ37

DDR3_HPS_DQ38

DDR3_HPS_DQ33

DDR3_HPS_DM4

DDR3_HPS_ODT

DDR3_HPS_CLK_P

DDR3_HPS_CASn

DDR3_HPS_RASn

DDR3_HPS_WEn

DDR3_HPS_CSn

DDR3_HPS_BA2

DDR3_HPS_BA1

DDR3_HPS_CKE

DDR3_HPS_BA0

DDR3_HPS_CLK_N

DDR3_HPS_ODT

DDR3_HPS_RESETn

ENET1_RX_D2

ENET1_RX_D3

ENET1_RX_D0

ENET1_RX_D1

ENET1_TX_D0

ENET1_TX_D1

ENET1_TX_D2

ENET1_TX_D3

ENET2_RX_D2

ENET2_RX_D0

ENET2_RX_D3

ENET2_RX_D1

ENET2_TX_D0

ENET2_TX_D2

ENET2_TX_D1

ENET2_TX_D3

USER_DIPSW_HPS0

USER_DIPSW_HPS2

USER_DIPSW_HPS1

USER_DIPSW_HPS3

USER_PB_HPS0

USER_PB_HPS1

USER_PB_HPS2

USER_PB_HPS3

HSMA_CLK_OUT_N[2:1](4,7,17)

HSMA_CLK_OUT_P[2:1](4,7,17)

HSMA_TX_D_P[16:0](7,17)

HSMA_TX_D_N[16:0](7,17)

HSMA_RX_D_P[16:0](7,17)

HSMA_RX_D_N[16:0](7,17)

SDI_CLK148_DN(4,8)

DDR3_HPS_DQS_P[4:0] (14)

DDR3_HPS_DQS_N[4:0] (14)

DDR3_HPS_DQ[39:0] (14)

DDR3_HPS_BA[2:0] (14)

DDR3_HPS_A[14:0] (14)

DDR3_HPS_DM[4:0] (14)

ENET1_TX_D[3..0] (19)

ENET1_RX_D[3..0] (19)

ENET1_TX_EN(19)

ENET1_RX_ERROR (19)

ENET1_RX_DV (19)

ENET1_RX_CLK (19)

ENET1_TX_CLK_FB(19)

ENET2_RX_ERROR (19)

ENET2_RX_DV (19)

ENET2_RX_CLK(19)

ENET2_TX_CLK_FB(19)

ENET2_TX_EN(19)

ENET2_TX_D[3..0] (19)

ENET2_RX_D[3..0] (19)

SDI_TX_EN(16,20)

SDI_TX_SD_HDn (20)

SDI_RSTI (20)

SDI_RX_EN (16,20)

SDI_RX_BYPASS (16,20)

SDI_FAULT (20)

DDR3_HPS_CLK_P(14)

DDR3_HPS_CLK_N(14)

DDR3_HPS_CKE(14)

DDR3_HPS_BA0(14)

DDR3_HPS_BA1(14)

DDR3_HPS_BA2(14)

DDR3_HPS_RASn(14)

DDR3_HPS_CASn(14)

DDR3_HPS_WEn(14)

DDR3_HPS_CSn(14)

DDR3_HPS_ODT(14)

DDR3_HPS_RESETn(14)

USER_DIPSW_HPS[3:0](23)

USER_PB_HPS[3:0](23)

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

541Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

541Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

Title

Size

Document Number Re v

Date: Sheet

of

D1

Cyclone V SoC FPGA Development Kit Board

B

541Thursday, November 21, 2013

150-0321003-D1 (6XX-44184R)

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

Copyright (c) 2013, Altera Corporation. All Rights Reserved.

CYCLONE V GX SoC BANK 5

Bank 5A

Bank 5B

5CSXFC6D_F896

U21C

PART_NUMBER = 5CGXFC7D7F31C8NES

Manufacturer = Altera Corp

DIFFIO_TX_R12p,DQ2R

AG28

RZQ_1,DIFFIO_TX_R1p,DQ1R

AG27

DIFFIO_RX_R4p,DQ1R

W20

DIFFIO_RX_R17n

V25

DIFFIO_TX_R18n,DQ3R

AC29

DIFFIO_RX_R19p,DQ3R

AB30

DIFFIO_TX_R20p,DQ3R

AB28

DIFFIO_RX_R19n,DQ3R

AA30

DIFFIO_TX_R20n,DQ3R

AA28

DIFFIO_TX_R24p,DQ3R

AD30

RZQ_2,DIFFIO_TX_R24n

AC30

DIFFIO_RX_R11n,DQ2R

Y24

DIFFIO_RX_R4n,DQ1R

Y21

DIFFIO_TX_R12n,DQ2R

AF28

DIFFIO_TX_R7p,DQ1R

AA25

DIFFIO_RX_R8p,DQ1R

AB22

DIFFIO_RX_R13p,DQS2R

V23

DIFFIO_TX_R7n

AB26

DIFFIO_TX_R14p

AF29

DIFFIO_RX_R8n,DQ1R

AB23

DIFFIO_RX_R13n,DQSn2R

W24

DIFFIO_RX_R9p

AA24

DIFFIO_TX_R14n,DQ2R

AF30

DIFFIO_TX_R10p,DQ2R

AE27

DIFFIO_RX_R15p,DQ2R

AD26

DIFFIO_RX_R9n

AB25

DIFFIO_TX_R16p,DQ2R

AH30

DIFFIO_TX_R10n,DQ2R

AE28

DIFFIO_RX_R15n,DQ2R

AC27

DIFFIO_RX_R11p,DQ2R

Y23

DIFFIO_TX_R16n

AG30

DIFFIO_RX_R17p

W25

DIFFIO_TX_R18p,DQ3R

AC28

R410100, 1%

CYCLONE V GX SoC BANK 6

Bank 6A

Bank 6B

5CSXFC6D_F896

U21D

PART_NUMBER = 5CGXFC7D7F31C8NES

Manufacturer = Altera Corp

HPS_DDR,HPS_A_13

C29

HPS_GI14

M25

HPS_DDR,HPS_A_14

H25

HPS_DDR,HPS_DM_0

K28

HPS_DDR,HPS_WE#

C28

HPS_DDR,HPS_DQ_7

J29

HPS_DDR,HPS_A_15

G25

HPS_DDR,HPS_DQ_5

L24

HPS_RZQ_0

D27

HPS_DDR,HPS_DQ_6

J30

HPS_DDR,HPS_DQ_4

L25

HPS_DDR,HPS_ODT_1

H29

HPS_DDR,HPS_DQS_0

N18

HPS_DDR,HPS_ODT_0

H28

HPS_DDR,HPS_DQS#_0

M19

HPS_DDR,HPS_DQ_3

G28

HPS_DDR,HPS_DQ_1

K22

HPS_DDR,HPS_DQ_2

H30

HPS_DDR,HPS_DQ_0

K23

HPS_DDR,HPS_A_0

F26

HPS_DDR,HPS_A_1

G30

HPS_DDR,HPS_A_4

J25

HPS_DDR,HPS_A_2

F28

HPS_DDR,HPS_A_5

J27

HPS_DDR,HPS_A_3

F30

HPS_DDR,HPS_CK

M23

HPS_GI11

M22

HPS_DDR,HPS_DM_1

M28

HPS_GI12

N23

HPS_DDR,HPS_A_6

F29

HPS_DDR,HPS_DQ_15

M30

HPS_DDR,HPS_CK#

L23

HPS_DDR,HPS_DQ_13

M27

HPS_DDR,HPS_A_7

E28

HPS_DDR,HPS_DQ_14

L28

HPS_DDR,HPS_BA_1

J24

HPS_DDR,HPS_BA_0

E29

HPS_DDR,HPS_BA_2

J23

HPS_DDR,HPS_DQ_12

M26

HPS_DDR,HPS_CAS#

E27

HPS_DDR,HPS_CKE_0

L29

HPS_DDR,HPS_RAS#

D30

HPS_DDR,HPS_DQS_1

N25

HPS_DDR,HPS_A_8

H27

HPS_DDR,HPS_CKE_1

L30

HPS_DDR,HPS_A_10

D29

HPS_DDR,HPS_DQS#_1

N24

HPS_DDR,HPS_A_9

G26

HPS_DDR,HPS_DQ_11

K27

HPS_DDR,HPS_A_11

C30

HPS_DDR,HPS_DQ_9

L26

HPS_DDR,HPS_CS#_0

H24

HPS_DDR,HPS_DQ_10

K29

HPS_DDR,HPS_A_12

B30

HPS_DDR,HPS_DQ_8

K26

HPS_DDR,HPS_CS#_1

K21

HPS_GI13

J26

HPS_DDR,HPS_DQS_4

T24

HPS_GI3

U20

HPS_DDR,HPS_DQ_36

T25

HPS_DDR,HPS_DQ_37

U25

HPS_DDR,HPS_DQS#_4

T23

HPS_DDR,HPS_DM_2

R28

HPS_DDR,HPS_DQ_32

W26

HPS_DDR,HPS_DQ_29

R26

HPS_DDR,HPS_DQ_26

T29

HPS_DDR,HPS_DM_4

W27

HPS_DDR,HPS_DQ_27

T28

HPS_GI7

V20

HPS_DDR,HPS_DQ_23

R29

HPS_GI6

T30

HPS_DDR,HPS_DQ_39

Y29

HPS_DDR,HPS_DQ_38

V27

HPS_GI8

P22

HPS_DDR,HPS_DQ_24

P24

HPS_DDR,HPS_DQ_34

U27

HPS_GI1

Y28

HPS_DDR,HPS_DQ_35

V28

HPS_GI2

V29

HPS_DDR,HPS_DQ_33

R24

HPS_GI4

T21

HPS_DDR,HPS_DQ_25

P25

HPS_DDR,HPS_DM_3

W30

HPS_DDR,HPS_DQ_31

W29

HPS_DDR,HPS_DQS#_2

R18

HPS_DDR,HPS_DQ_20

P26

HPS_GI9

P29

HPS_DDR,HPS_DQ_22

N27

HPS_DDR,HPS_RESET#

P30

HPS_DDR,HPS_DQ_21

P27

HPS_DDR,HPS_DQS_2

R19

HPS_DDR,HPS_DQ_19

N28

HPS_DDR,HPS_DQS#_3

R21

HPS_DDR,HPS_DQ_17

T26

HPS_DDR,HPS_DQ_16

U26

HPS_GI10

N30

HPS_DDR,HPS_DQ_18

N29

HPS_DDR,HPS_DQ_28

R27

HPS_GI5

U28

HPS_DDR,HPS_DQ_30

V30

HPS_DDR,HPS_DQS_3

R22

剩余40页未读,继续阅读

dodoshao

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2