没有合适的资源?快使用搜索试试~ 我知道了~

电子-VGA显示矩阵教学至简设计.pdf

需积分: 10 1 下载量 78 浏览量

2019-09-05

13:06:11

上传

评论

收藏 1.29MB PDF 举报

温馨提示

试读

20页

电子-VGA显示矩阵教学至简设计.pdf,单片机/嵌入式正点原子FPGA

资源推荐

资源详情

资源评论

VGA 显示矩阵

一、项目背景

请参考“VGA 显示颜色”案例中的项目背景内容。

二、设计目标

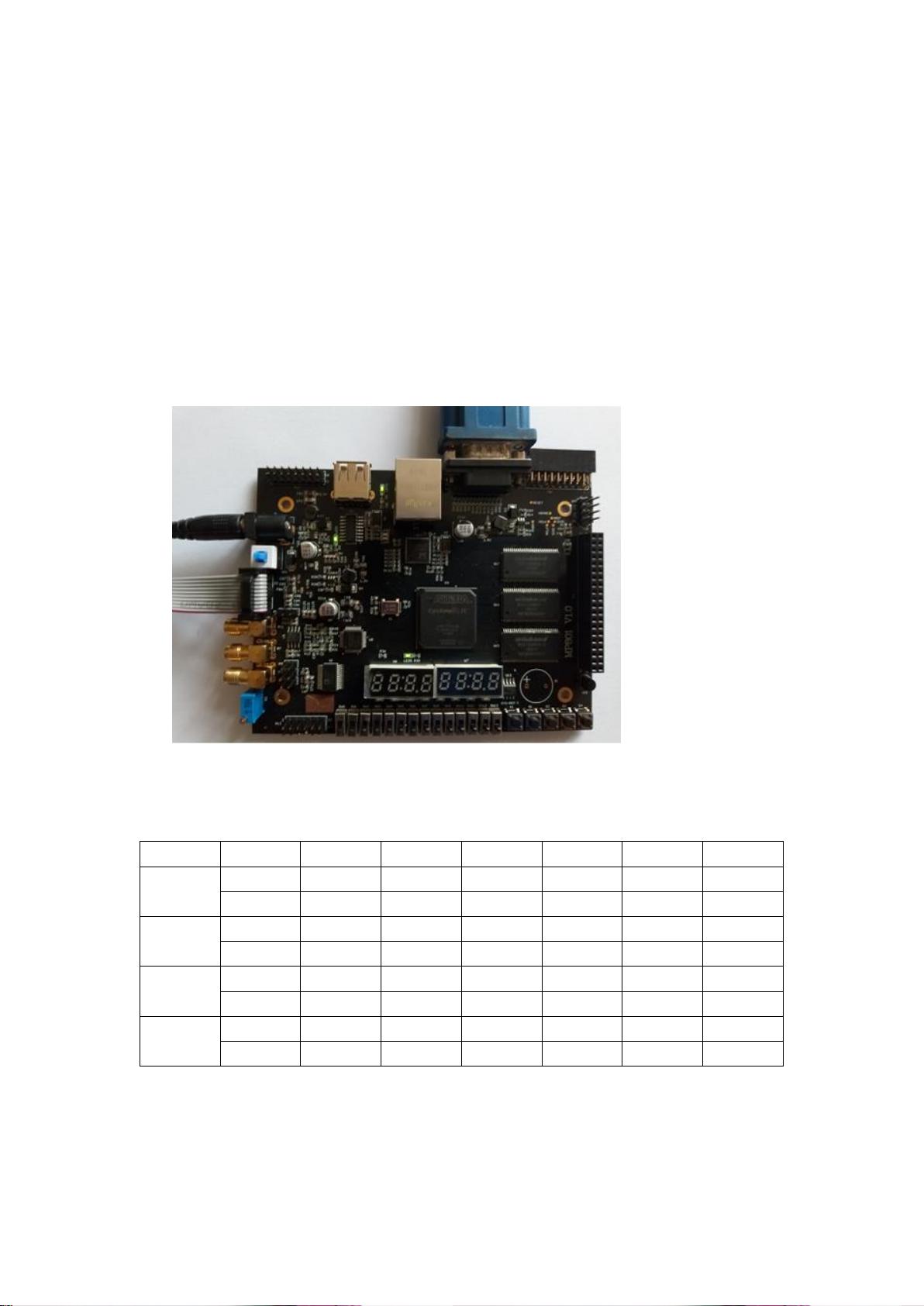

通过 VGA 连接线,将显示器和教学板的 VGA 接口相连。连接示意图如下。

然后 FPGA 产生 640*480 分辨率,刷新频率为 60Hz 的 VGA 时序,让显示器产生显示一幅完整

的矩阵图像,即下表中的第一种参数。提示:显示器一般都会自适应功能,无须设置就能识别不同分

辨率的图像。

分辨率

行/列

同步脉冲

显示后沿

显示区域

显示前沿

帧长

单位

640*480

/60Hz

行

96

48

640

16

800

基准时钟

列

2

33

480

10

525

行

800*600

/72Hz

行

120

64

800

56

1040

基准时钟

列

6

23

600

37

666

行

800*600

/60Hz

行

128

88

800

40

1056

基准时钟

列

4

23

600

1

628

行

1024*768

/60Hz

行

136

160

1024

24

1344

基准时钟

列

6

29

768

3

806

行

其中,行的单位为“基准时钟”,即频率为 25MHz、周期为 40ns 的时钟,注意列的单位为“行”。

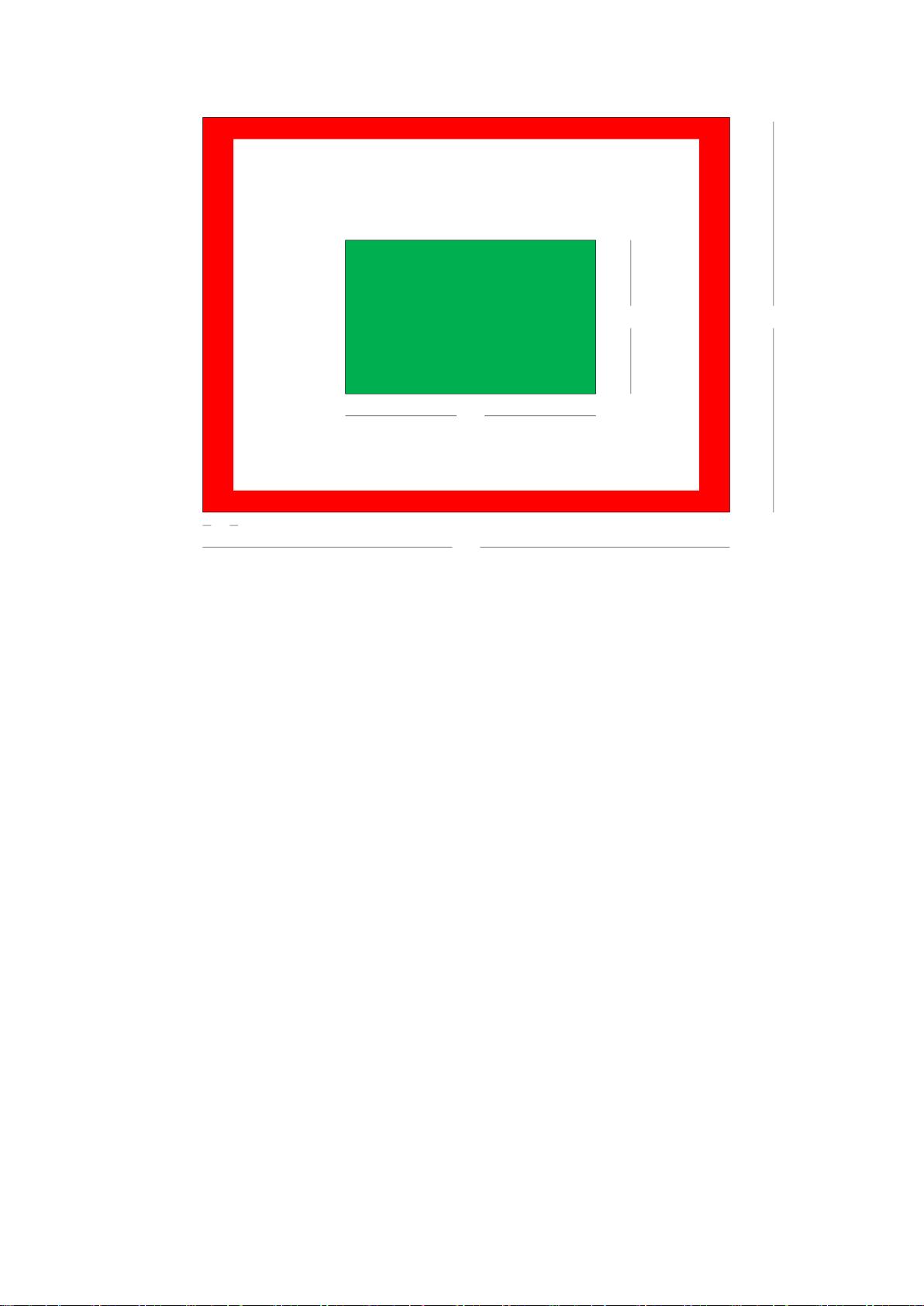

矩阵图像是在显示屏边缘上显示一个红色边框(边框宽为 20 像素),在屏幕的中央显示一个绿

色矩形(矩形长为 150 像素,高为 100 像素)。

640

20

150

100 480

上板效果图如下图所示,注意,不同显示器会有差别。

上板的演示视频,请登陆网址查看:www.mdy-edu.com/xxxx。

三、模块设计

架构设计

我们要实现的功能,概括起来就是 FPGA 产生 VGA 时序,即控制 VGA_R4~R0、VGA_G5~G

0、VGA_B4~B0、VGA_HSYNC 和 VGA_VSYNC,让显示器显示红色。其中,VGA_HSYNC 和 VG

A_VSYNC,FPGA 可根据时序产生高低电平。而颜色数据,由于是固定的红色,FPGA 也能自己产

生,不需要外部输入图像的数据。那么我们的 FPGA 工程,可以定义输出信号 hys 表示行同步,用输

出信号 vys 表示场同步,定义一个 16 位的信号 lcd_rgb,其中 lcd_rgb[15:11]表示 VGA_R4~0,、 lcd

_rgb[10:5]表示 VGA_G5~0,、 lcd_rgb[4:0]表示 VGA_B4~0。

我们还需要时钟信号和复位信号来进行工程控制。

综上所述,我们这个工程需要五个信号,时钟 clk,复位 rst_n,场同步信号 vys、行同步信号 h

ys 和 RGB 输出信号 lcd_rgb。

需要注意的是,输入进来的时钟 clk 是 50MHz,而从分辨率参数表可知道,行单位的基准时钟

是 25 MHz。为此我们需要根据 50MHz 来产生一个 25 MHz 的时钟,然后再用于产生 VGA 时序。

为了得到这个 25M 时钟,我们需要一个 PLL。PLL 可以认为是 FPGA 内的一个硬核,它的功能

是根据输入的时钟,产生一个或多个倍频和分频后的输出时钟,同时可以调整这些输出时钟的相位、

占空比等。

例如,输入进来是 50M 时钟,如果我需要一个 100M 时钟,那么从逻辑上、代码上是不可能产

生的,我们就必须用到 PLL 来产生了。

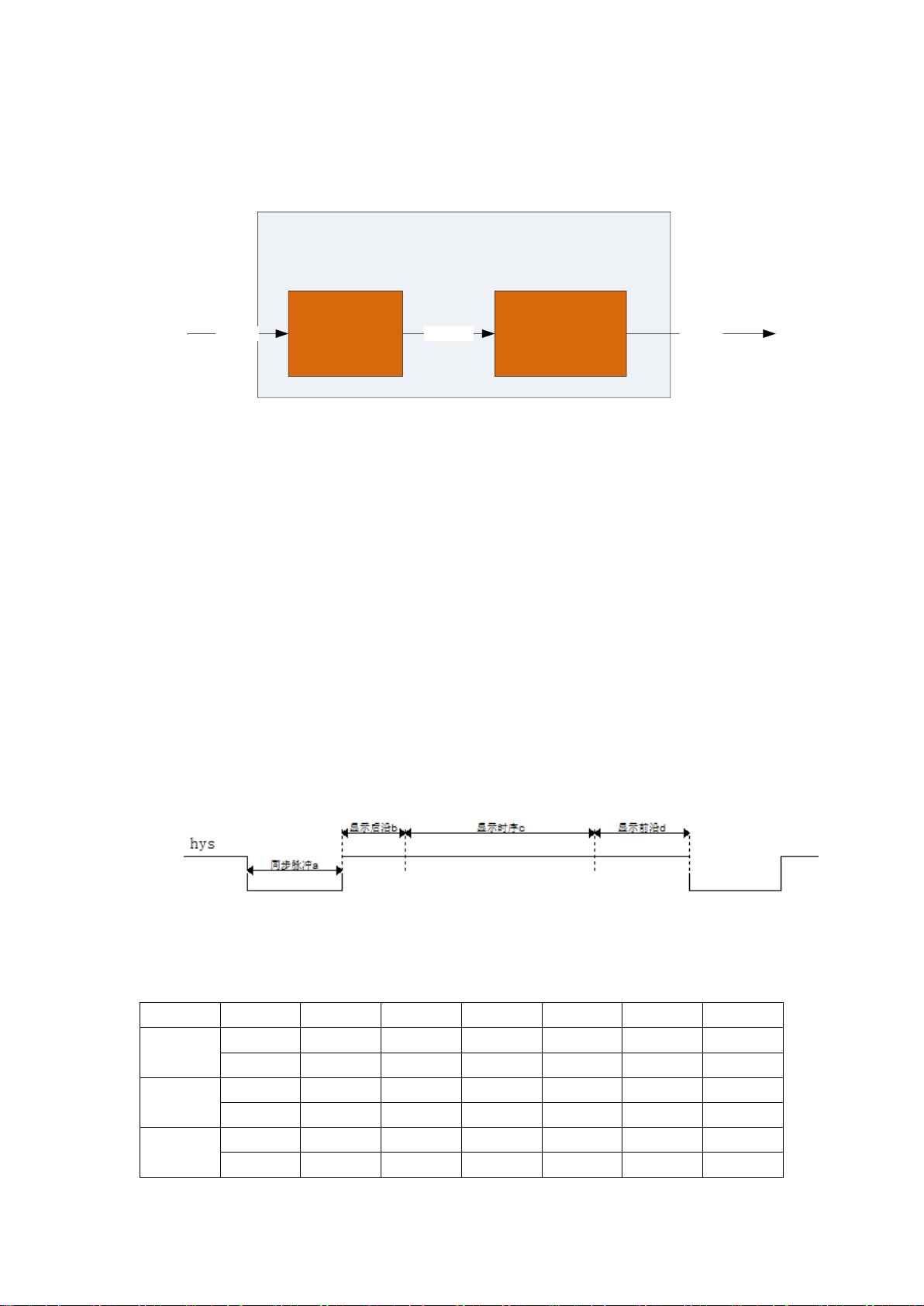

整个工程的结构图如下。

PLL模块 VGA驱动模块

顶层模块

Clk/50M Clk0/50M VGA信号

PLL 的生成方式过程,请看本案例的综合工程和上板一节的内容。

VGA 驱动模块设计

我们先分析功能。要控制显示器,让其产生红色,也就是让 FPGA 控制 VGA_R0~4、VGA_G0

~5、VGA_B0~4、VGA_VSYNC 和 VGA_HSYNC 信号。那么 VGA 驱动模块,可以定义输出信号 h

ys 表示行同步,用输出信号 vys 表示场同步,定义一个 16 位的信号 lcd_rgb,其中 lcd_rgb[15:11]表

示 VGA_R4~0,、 lcd_rgb[10:5]表示 VGA_G5~0,、 lcd_rgb[4:0]表示 VGA_B4~0。

同时该模块的工作时钟为 25M,同时需要一个复位信号。

综上所述,我们这个模块需要五个信号,25M 时钟 clk,复位 rst_n,场同步信号 vys、行同步信

号 hys 和 RGB 输出信号 lcd_rgb。

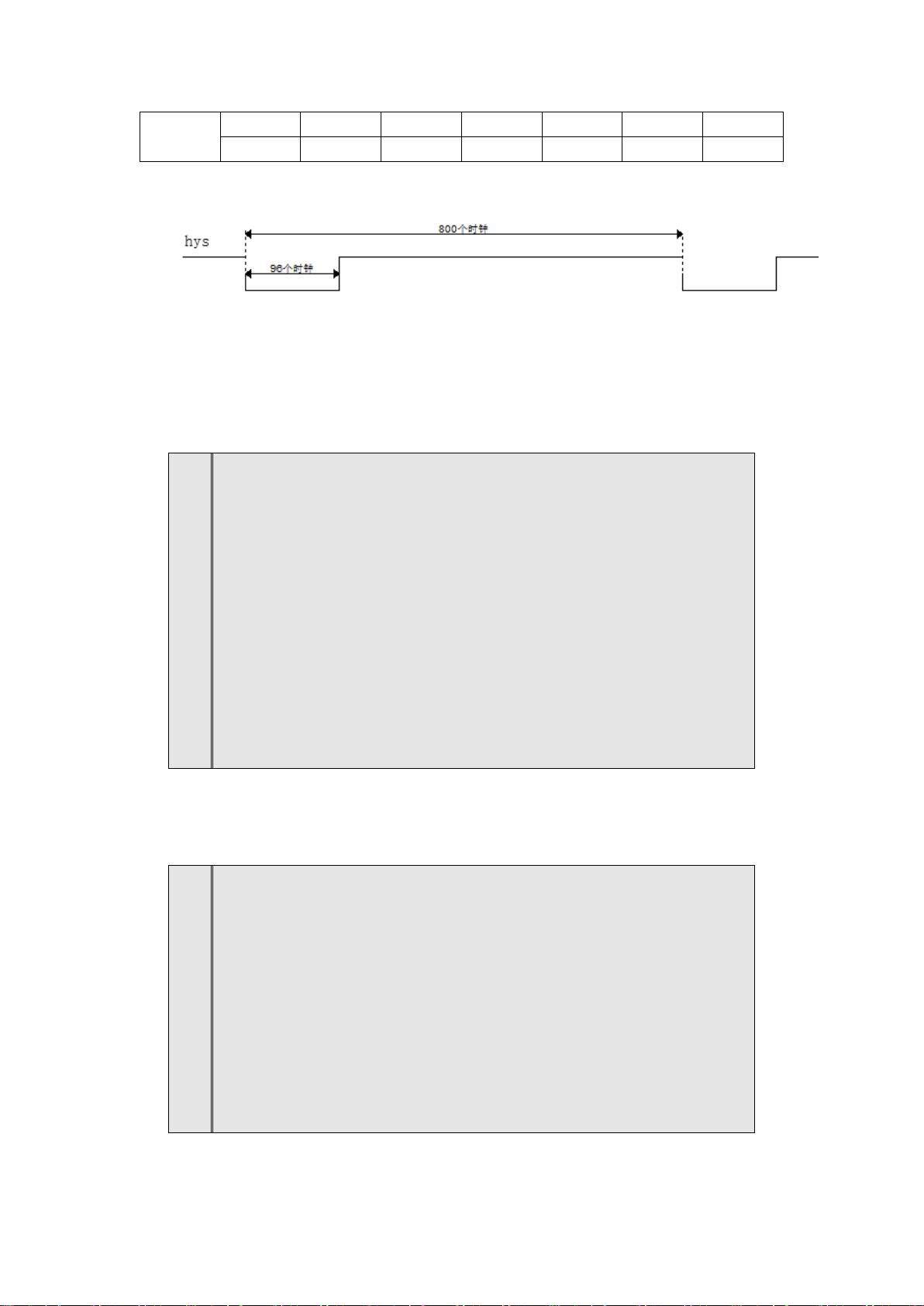

我们先设计场同步信号 hys,VGA 时序中的场同步信号,其时序图如下:

hys 就是一个周期性地高低变化的脉冲。我们使用的是下表中的第一种分辨率,也就是同步脉冲

a 的时间是 96 个时钟周期,而显示后沿 b 是 48 个时钟周期,显示时序 c 是 640 个时钟周期,显示

前沿是 16 个时钟周期,一共是 800 个时钟周期。

分辨率

行/列

同步脉冲

显示后沿

显示区域

显示前沿

帧长

单位

640*480

/60Hz

行

96

48

640

16

800

基准时钟

列

2

33

480

10

525

行

800*600

/72Hz

行

120

64

800

56

1040

基准时钟

列

6

23

600

37

666

行

800*600

/60Hz

行

128

88

800

40

1056

基准时钟

列

4

23

600

1

628

行

1024*768

/60Hz

行

136

160

1024

24

1344

基准时钟

列

6

29

768

3

806

行

将时间信号填入图中,更新后的时序图如下:

很显然,我们需要 1 个计数器来产生这个时序,我们将该计数器命名为 h_cnt。由于 hys 是不停

地产生的,那么 h_cnt 就是不停地计数,每个时钟都要计数器,所以认为该计数器的加 1 条件为“1”,

可写成:assign add_h_cnt = 1。从上图可知,该计数器的周期是 800。综上所述,该计数器的代码

如下:

1

2

3

4

5

6

7

8

9

10

11

12

13

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

h_cnt <= 0;

end

else if(add_h_cnt)begin

if(end_h_cnt)

h_cnt <= 0;

else

h_cnt <= h_cnt + 1;

end

end

assign add_h_cnt = 1;

assign end_h_cnt = add_h_cnt && h_cnt== 800 - 1;

有了计数器 h_cnt,那么 hys 信号就有了对齐的对象。从时序图可以发现, hys 有两个变化点,

一个是 h_cnt 数到 96 个时,由 0 变 1;另一个是当 h_cnt 数到 800 个时,由 1 变 0。所以,场同步

信号的代码如下:

1

2

3

4

5

6

7

8

9

10

11

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

hys <= 0;

end

else if(add_h_cnt && h_cnt == 96 -1)begin

hys <= 1'b1;

end

else if(end_h_cnt)begin

hys <= 1'b0;

end

end

剩余19页未读,继续阅读

资源评论

weixin_38743481

- 粉丝: 694

- 资源: 4万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 第12章spring-mvc自定义类型转换器

- 基于PHP图书管理系统实验报告.docx

- Python爬取淘宝热卖商品并可视化分析

- 5152单片机proteus仿真和源码将按键次数写入AT24C02再读出并用1602LCD显示

- SE-SSD复现过程(Det3D的安装教程)

- 基于Python的在线学习与推荐系统设计与实现(论文+源码)-kaic

- 串口通过 YMODEM 协议进行文件传输

- 蓝桥杯2024年第十五届省赛真题-前缀总分

- com.qihoo.appstore_300101305-1.apk

- tensorflow-gpu-2.7.1-cp37-cp37m-manylinux2010-x86-64.whl

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功